Part1 问题的来源

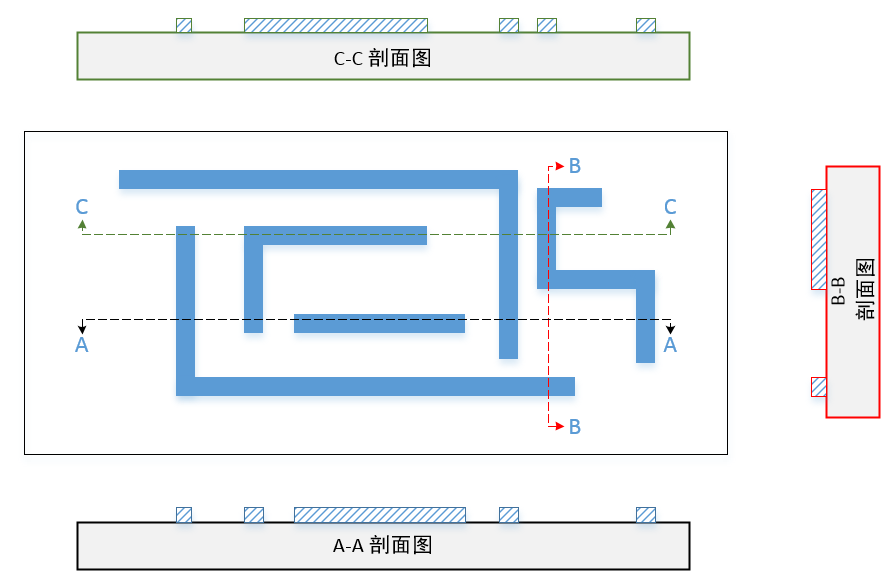

图1.1单层布线

如果之前看过分立电路的印刷电路板(PCB),那么集成电路的布线层就相当于“微缩版的PCB”,它也分为单层布线(单面板)和多层布线(双面板,多层板)。(如图1.1)在集成电路的同一个布线层中,不同金属导线之间通过绝缘材料(二氧化硅很常见)实现电学绝缘。

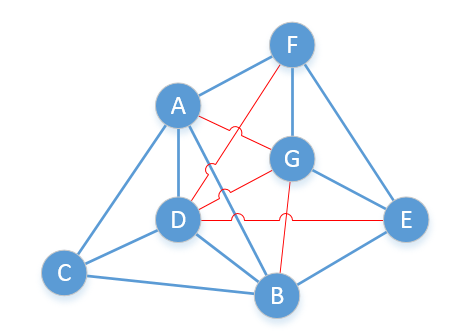

图1.2复杂拓扑关系的布线

为了实现更复杂的功能,电路中的器件会越来越多,器件之间的电学连接拓扑关系也越来越复杂,结果是使用单层布线无法“布通”。这种情况下,只有增加布线层才能实现“布通”的效果(如图1.2,红色跳线就代表需要另外一层才能完成布线),这就是所谓的“多层布线”。

Part2 多层布线

2.1 多层布线的物理结构

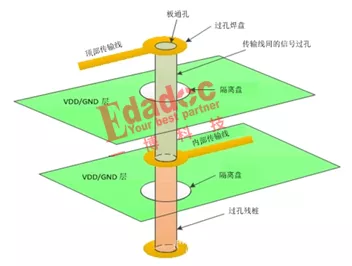

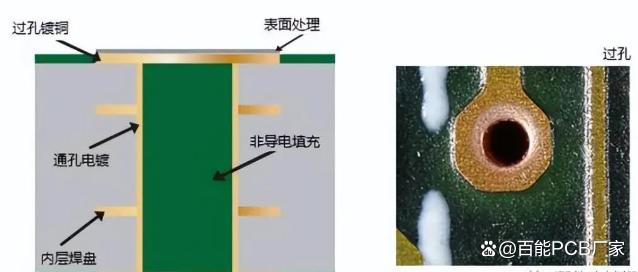

相邻布线层之间使用绝缘材料(常见的是SiO2)进行电学隔离,相同布线层中的导线使用绝缘材料(常见的是SiO2)进行电学隔离;相邻布线层中的导线,通过在绝缘层上开孔、孔内填满导电材料,“实现电学连通”。

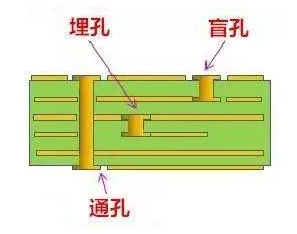

2.2 孔

穿透绝缘层的“孔”分为两大类:第一种“孔”称为Contact(接触孔),用来连接“布线”和“器件层的电极”;第二种“孔”称为Via(通孔),用来连接位于不同布线层的导线。

“孔”,从工艺制备的角度来说,分为两步,首先是开孔,然后是在孔内填满导电材料;从版图的角度来说,画出来就只是一个“矩形”而已。

2.3 量变带来的新问题

在进行“多层互连”的时候,很多问题自然而然的出现了,接下来通过剖面图来逐一说明:

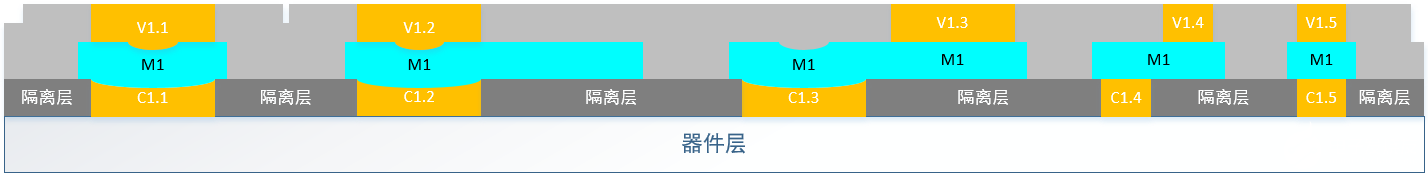

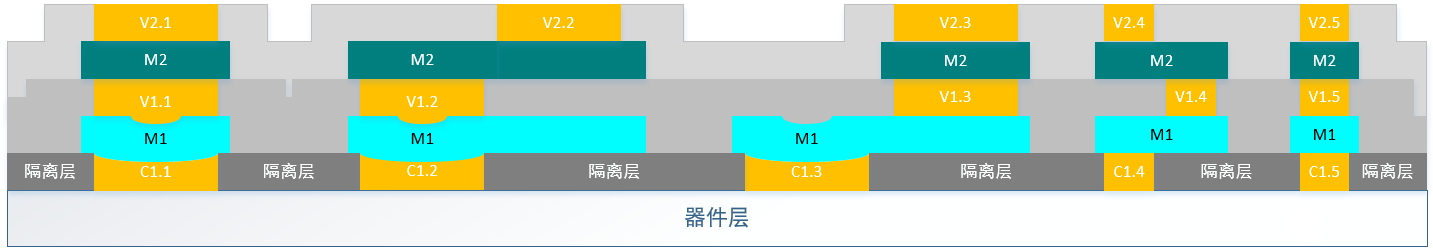

图2.1制作Contact(接触孔)

(图2.1)在器件层上制作了“Contact”,“黄色”表示在孔中填充的导电材料,“灰色”表示各孔之间的绝缘材料,共用C1.1,C1.2,C1.3,C1.4,C1.5表示了五种情况。其中C1.1~C1.3因为孔比较大,所以金属材料在填充的时候,表面会向下凹(表面张力和重力导致);C1.4和C1.5因为孔比较小,所以填充的金属表面近似水平。

图2.2制作Metal 1(简写为M1)

(图2.2)做完了Contact之后,先在材料表面生长一层Metal,然后使用光刻和腐蚀工艺得到需要的金属布线。

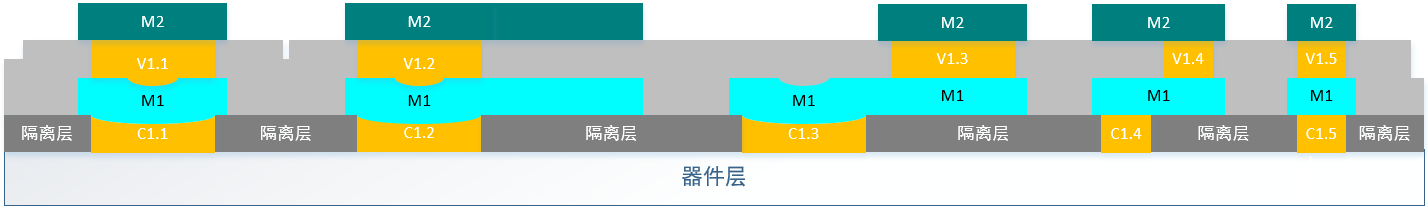

图2.3制作Via 1(简写为V1)

(图2.3)在Metal 1上生长绝缘层,然后做孔。因为这次的孔用来连接M1和M2,所以它的名字改为“Via”,翻译成“通孔”,通的意思类似“架在河上的桥梁,取穿通,打通的意思,打通的就是相邻互连层之间的绝缘材料”。

那么Via应该放在哪里呢?这个东西没有多么神器,你就把它当成做试验,所有的可能都试一下,我画了5种情况,分别是“V1.1~V1.5”。

图2.4制作Metal 2(简写为M2)

(图2.4)做完了Via 1之后,先在材料表面生长一层Metal,然后使用光刻和腐蚀工艺得到需要的金属布线。因为这是第二层Metal,所以称它为Metal 2,这里简写为M2。

图2.5制作Via 2(简写为V2)

(图25)在Metal 2上生长绝缘层,然后做孔,即Via 2。现在,应该把所有的可能都列出来了,如果有忘记分析的情况,大家留言提醒一下。

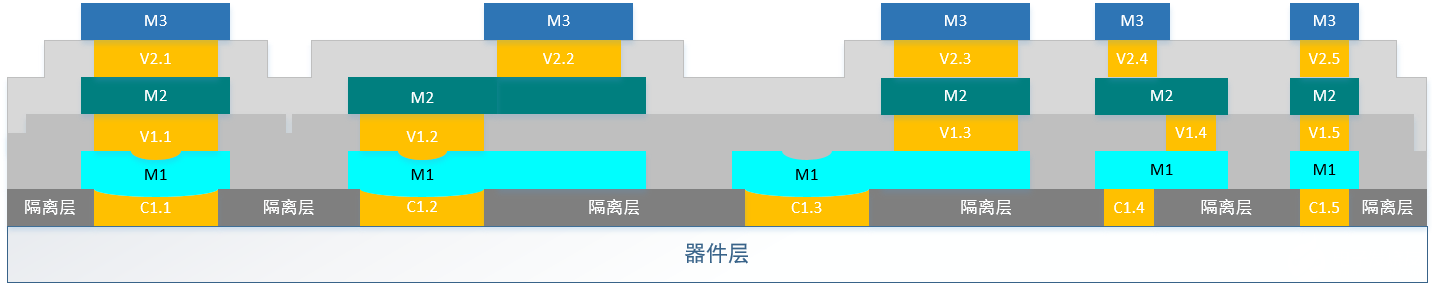

图2.6制作Metal 3(简写为M3)

(图2.4)做完了Via 2之后,先在材料表面生长一层Metal,然后使用光刻和腐蚀工艺得到需要的金属布线。因为这是第三层Metal,所以称它为Metal 3,这里简写为M3。现代多层布线可以到128层以上,这里只画3层进行演示。

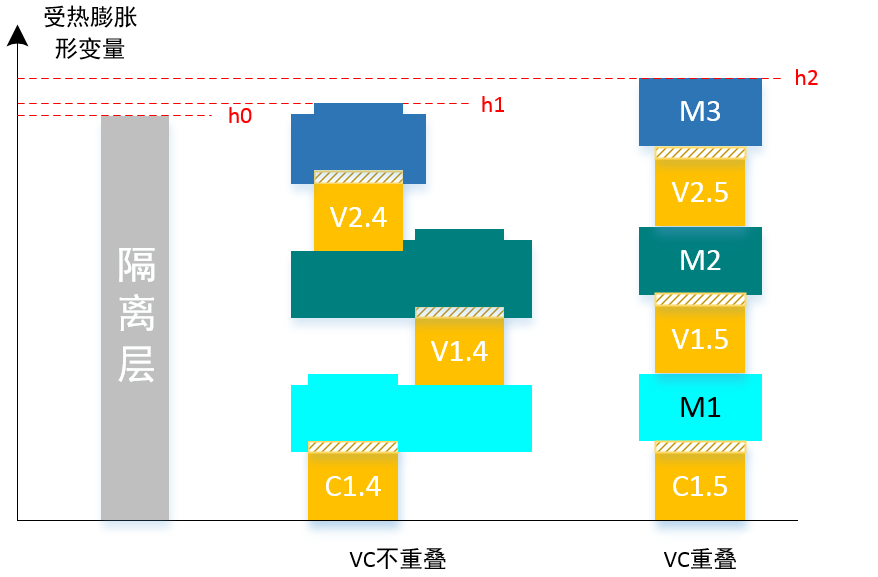

小结一下:金属层数的命名是根据工艺制造的先后命名的,从剖面图来看就是从下向上依次排序的;在垂直方向,C1.1-V1.1-V2.1和C1.5-V1.5-V2.5是重合的,其它的都存在不重合,也就是说,Contact和Via在垂直方向可能会出现“重合、交错”两种情况。

那么问题来了,重合和交错可能会带来什么影响?

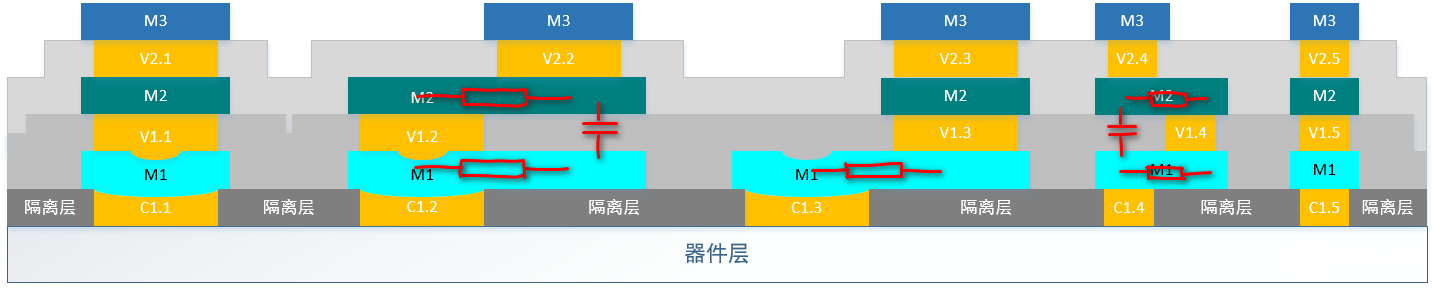

2.4 问题分析

交错的孔会引入寄生电阻和寄生电容,除非是设计本来就有的,否则寄生效应会对电路性能构成不利的影响,会增加后仿真中调整参数的工作量。

图2.7寄生电阻和寄生电容

2.4.2 可制造性

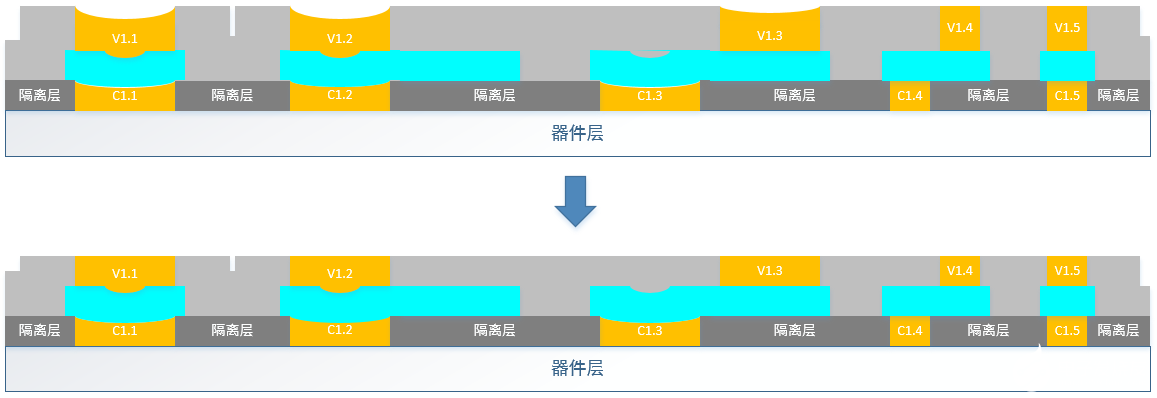

除了电学性能之外,还需要考虑的是可造性。对比V1.2和V1.3,其中V1.2的地基是凹陷,V1.3的地基是平面。因为后面的工艺会继承前面的凹陷,很多时候都会放大凹陷的程度,最终降低良率,所以“平面地基”更有利于后面的工序制造。

对于打孔来说,表面无法填平是客观存在的。为了避免在不平整的地基上做孔,要么采用V1.3的方法做孔,要么开发“平坦化工艺”,比如CMP工艺,把表面去掉一层,也就是表面没有填平的地方全部去掉,那么就不存在不平整的地基了。Via 1这一层就采用了平坦化工艺(如图2.8)。

图2.8平坦化工艺(去掉坑坑洼洼,把表面磨平)

2.4.3 可靠性

集成电路工作时可能会产生大量的热(比如,计算机CPU不加散热器是可以煎鸡蛋的),构成集成电路的各种材料就发生“热胀冷缩”(如图2.9)

图2.9热胀冷缩

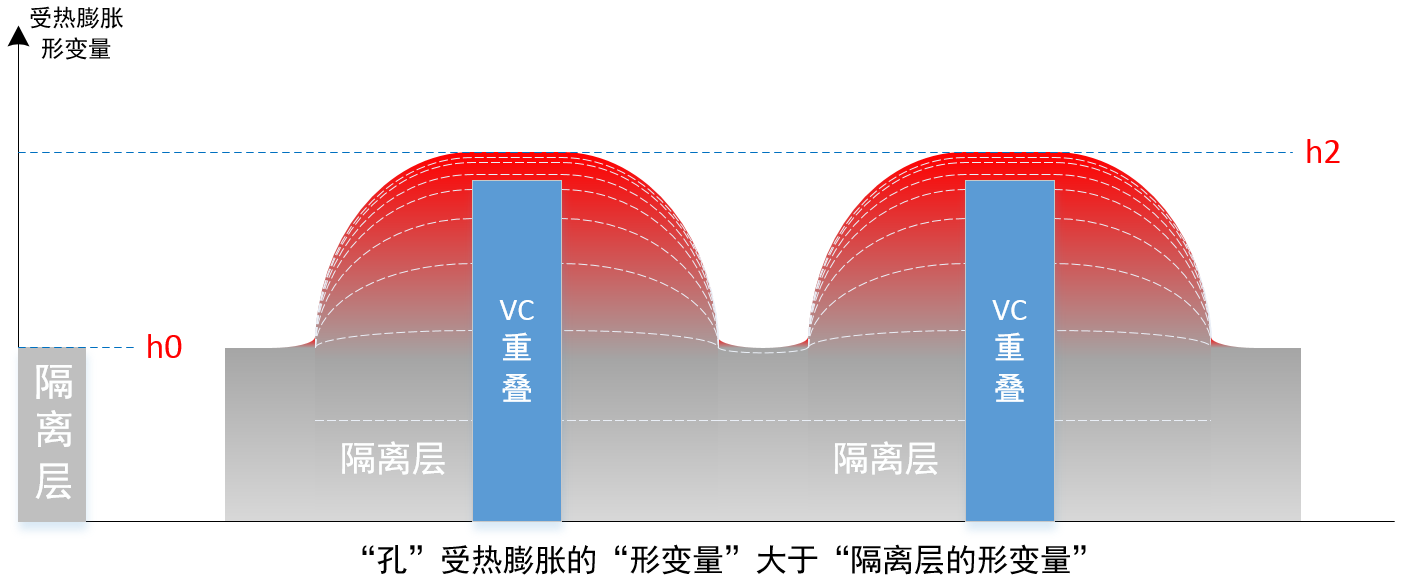

这里做的是最简单的受热膨胀的分析,并且假设“孔受热膨胀变形最严重,绝缘材料(隔离层)和导电材料(Metal)相对很小被忽略”:

(图2.9的纵坐标)重合孔的形变量(h2)最大,交错孔的形变量(h1)次之。随着布线层数↑,h2和h1继续增大,显然“h2-h1”继续增大。

如果h0随温度变化没有h2大,就会出现(图2.10)的情况:最坏的情况=隔离层被孔撑破;次之,隔离层没有被撑破,但是反复大幅度形变,很快就会出现裂缝。隔离层被破坏之后,相邻层的导线可能会短路,形变较大处的导线可能会被折断,通过裂缝入侵的水汽等杂质会破坏芯片内部结果,导致芯片很快报废。“芯片寿命很短,可靠性很低”都是不能被用户接受的。(图2.10)仅以重叠孔为例,“VC不重叠”只是比“VC重叠”的破坏力弱一些而已。

图2.10孔受热膨胀的极端情况

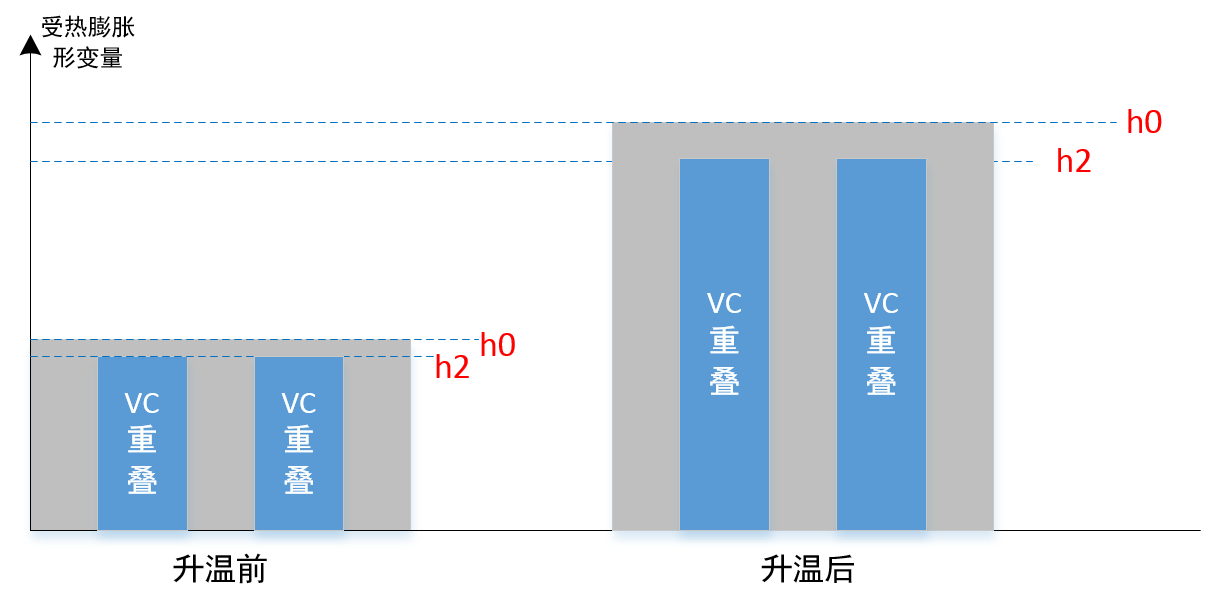

如果h0随温度变化与h2相同,就会出现(图2.11)这种非常理想的情况。

图2.11受热膨胀的理想情况

2.5 对策

版图设计是建立在“工艺流程”基础上的,不能随心所欲的画;版图和工艺配合,就会制造出特定的物理结构。

尽可能的使孔和绝缘材料的膨胀形变量相同,如果工艺上无法实现这一点,首先要减少重合孔的使用,其次是减少布线的层数。

审核编辑:黄飞

-

集成电路

+关注

关注

5464文章

12669浏览量

375615 -

电容

+关注

关注

100文章

6518浏览量

160019 -

cpu

+关注

关注

68文章

11320浏览量

225834 -

光刻

+关注

关注

8文章

367浏览量

31393 -

寄生电阻

+关注

关注

1文章

23浏览量

2530

发布评论请先 登录

多层印制电路板中过孔互连多层供电系的建模与仿真

高速PCB中的过孔设计,你真的懂吗?

过孔是什么

高速PCB设计中的过孔和背钻技术解析

多层PCB如何过孔

如何实现多层PCB的过孔

PCB中过孔和背钻的技术知识

PCB生产中的过孔和背钻有些什么样的技术?

多层pcb设计如何过孔的原理

多层PCB板过孔塞油工艺要点解析

深度解析多层互连的过孔设计

深度解析多层互连的过孔设计

评论