思路很简单,在3个周期里产生两个脉冲,等效于分频1.5。

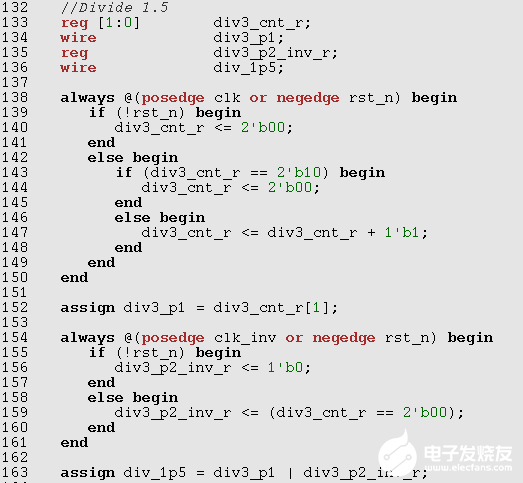

第一个脉冲很容易实现。计数器2’b00 -- 2’b01 – 2’b10无限循环,最高位就是每三个周期出现一次的脉冲。第二个脉冲要用到一个negedge DFF。两个脉冲OR一下,输出就是1.5分频。

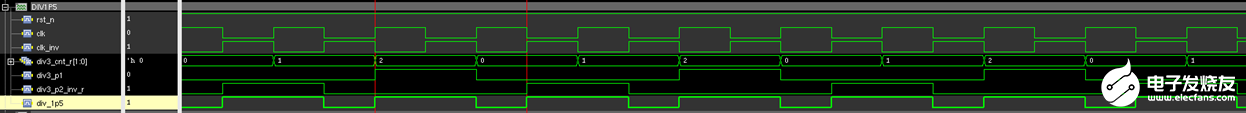

下面是Verilog RTL及波形。

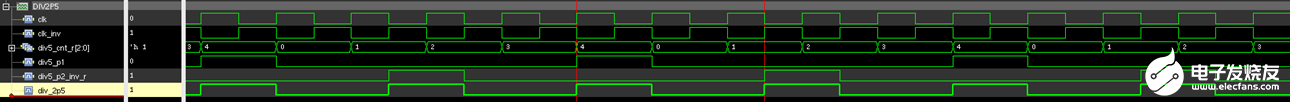

2.5分频

一样的思路,5个周期产生两个脉冲就可以了。

其他x.5分频可以按同样的思路类推。

这种分频后的输出有几个“缺陷“,使用的时候要注意。

-占空比无法做到50-50。

-分频输出有一点jitter。Jitter来自于两个脉冲上升沿相对于原始时钟的上升沿下降沿,delay是不一样的。原始时钟本身上升沿下降沿的jitter会叠加在上面。

要求不高的场合,这种数字逻辑实现的小数分频输出可以当作时钟用。Jitter要求高的场合,还是要用PLL实现。

审核编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pll

+关注

关注

6文章

781浏览量

135301 -

计数器

+关注

关注

32文章

2261浏览量

94952 -

分频

+关注

关注

0文章

241浏览量

24905 -

数字逻辑

+关注

关注

0文章

74浏览量

16695 -

数字前端

+关注

关注

0文章

9浏览量

7802

发布评论请先 登录

相关推荐

五分频电路,四分频电路

四4分频电路下图的分频电路输出占空比均为50%,可用D-FF,也可用JK-FF来组成,用JK-FF构成分频电路容易实现并行式同步工作,因而适合于较高频的应用场合。而FF中的引脚R、S(

发表于 06-22 08:02

IC数字前端设计实战案例系列pdf

来说,verilog是很好的,verilog代码不是说只能在fpga上跑的,用不同的综合器,可以得到不一样的器件,在集成电路工艺上,用cadence综合实现就可以得到数字IC,如果你真想做IC前端设计的话

发表于 12-14 16:18

小白入门数字前端,求大神指教需要学什么知识以及用哪些软件

本帖最后由 无名兵卒 于 2018-3-22 15:24 编辑

事情是这样的,我目前在念研一,我们组里需要做数字的但又没有做数字的,所以老师想让我转到数字前端,可我是啥都不懂啊,望看到这个帖子

发表于 03-22 15:21

用VHDL语言实现3分频电路

用VHDL语言实现3分频电路

标签/分类:

众所周知,分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相

发表于 08-21 15:28

•5725次阅读

汽车音响选择二分频还是三分频改装_汽车音响分频器安装方法

本文首先介绍了二分频和三分频区别,其次阐述了汽车音响选择二分频还是三分频改装,最后介绍了汽车音响三分频的安装方法,具体的跟随小编一起来了解一

数字前端设计的x.5分频实现思路

数字前端设计的x.5分频实现思路

评论