简介

SiC 功率 MOSFET 和肖特基二极管正在快速应用于电力电子转换半导体 (PECS) 应用,例如电动汽车充电和牵引、储能系统和工业电源。SiC 功率 MOSFET 已在电动汽车车载充电器中得到广泛应用,并且在非车载充电器中也越来越受欢迎。与当前逆变器中的 Si IGBT 解决方案相比,这些器件为纯电动汽车带来了改善逆变器续航里程和/或降低成本的优势。服务器电源中的设备已大量出货,牵引逆变器中的设备数量也在不断增加。尽管 SiC MOSFET 至少从 1987 年就已经存在,但在如此大批量和高可靠性市场的广泛采用却花了几十年的时间。这是因为器件的许多方面都需要进行数量级的改进,特别是栅极氧化物的质量和可靠性。

挑战在于,所有这些市场,尤其是交通运输市场,都期望系统级别具有极高的可靠性。应用要求相当高:大量 SiC 芯片和总 SiC 有效面积(数百至数千 mm2)、高结温(通常为 175 °C 及以上)和低故障率(“早期”期间每年累计 < 1 ppm)。”,预计很快就会得到改善。)预计很快就会有所改善。)同时,与硅相比,SiC 的可靠性情况是独一无二的:

- 一些 SiC 失效机制比 Si 更严重

- 至少一种失效机制是 SiC 所独有的,并且在Si

- 对 SiC 的要求在很多方面都高于对 Si 的要求

接受这一挑战意味着 SiC 器件制造商必须能够通过提供彻底且有时新颖的表征,在“浴盆曲线”的所有阶段展示出色的可靠性预测质量、随机故障率和磨损寿命。但这也意味着,与硅行业相比,由制造商和最终用户组成的行业联盟组织必须以极快的速度制定指南和标准。

在硅产业中,相对于技术的成熟度和广泛采用程度,指导方针和标准的启动和制定需要更长的时间。

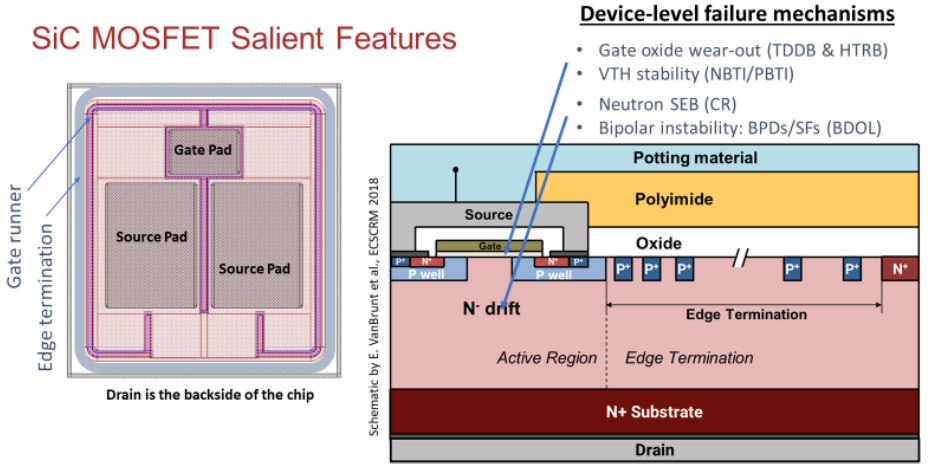

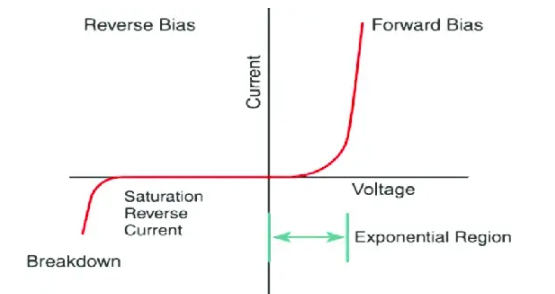

SiC 中的失效机制

在 SiC 器件中观察到的一些失效机制与在 Si 器件中观察到的类似,例如单粒子烧毁(SEB,由于地球中子)和栅极氧化物磨损。SiC MOSFET 显示偏置温度不稳定性 (BTI) 退化机制,具有与 Si MOSFET 类似的加速因子和时间依赖性。然而,由于界面和近界面电荷陷阱的密度较高,SiC 器件中的 BTI 可能更加突出,因此需要更彻底地表征 BTI 响应,包括表征阈值电压 (VT) 的特殊技术。SiC MOSFET 很容易受到双极退化(增加的导通电阻和可能的泄漏),这是由于在第三象限操作中发生的电子空穴复合的影响下基面位错 (BPD) 转化为堆垛层错。这种双极退化机制是 SiC 所独有的,需要新颖的可靠性表征。值得注意的是,观察结果与双极退化是一种早期故障率 (ELFR) 机制而不是内在磨损一致,因为只有预先存在 BPD 的设备才会经历双极退化。通过表征这些机制,可以构建完整的可靠性“浴缸曲线”,其中表示早期寿命故障率/“婴儿死亡率”(双极稳定性)、使用寿命期间的恒定(随机)故障率(SEB 和随机潜在缺陷)产品生命周期的磨损(栅极氧化、VT 稳定性和封装)阶段。本文中显示的可靠性数据来自 Wolfspeed Gen3 SiC 平面 MOSFET,其显着特征如图 1 所示。这些可靠性考虑因素通常也适用于沟槽 MOSFET,尽管其中一些影响的存在和严重程度可能有所不同。

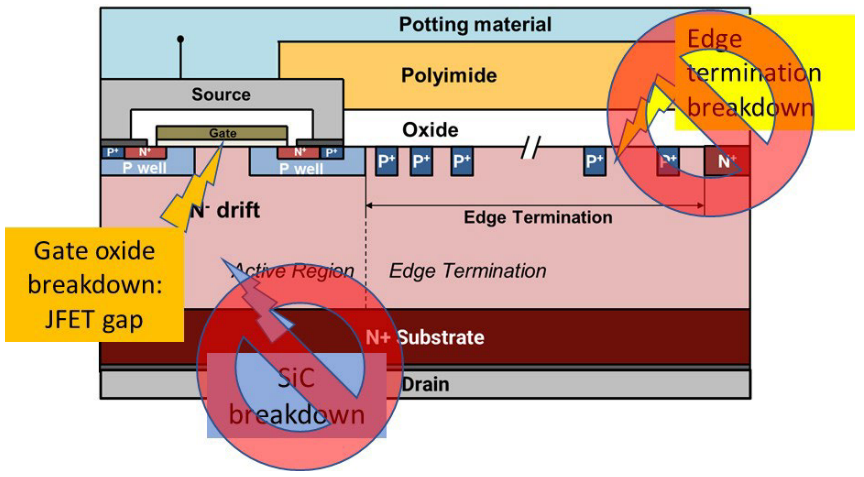

图 1. Wolfspeed SiC 平面 MOSFET 原理图平面图、横截面、显着特征和代表性故障机制。

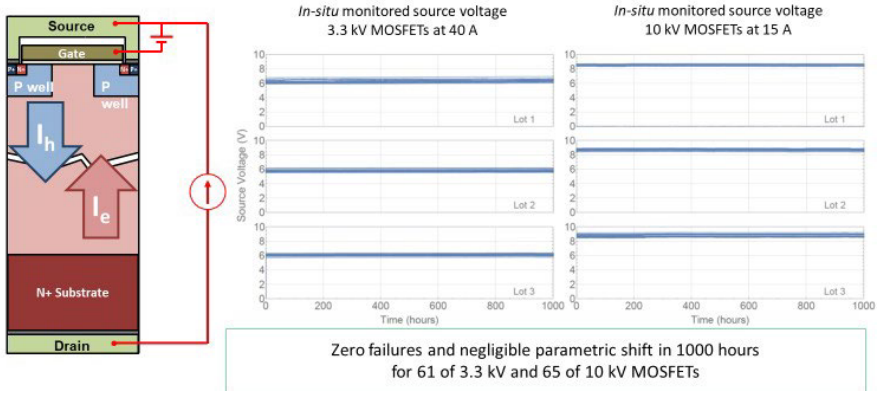

双极稳定性。基面位错 (BPD) 处的复合增强堆垛层错 (SF) 滑移对 SiC MOSFET 中 4H-SiC 双极器件的可靠运行提出了基本的材料挑战。这种情况的发生会导致电阻增加和泄漏。然而,现代 4H-SiC 衬底生产实践已导致基面位错密度大幅降低,当与适当的生产筛选方法相结合时,可以实现具有极低 BPD 密度的可靠器件,因此该机制的故障率较低。几乎不关心两极稳定。双极性稳定性可以通过体二极管工作寿命(BDOL)应力测试来验证,在该测试中,恒定电流施加于第三象限模式下的MOSFET。具有足够的散热和/或占空比,以将结温保持在最大额定值内。例如,Wolfspeed, Inc. 发布了额定值为 3.3 kV 和 10 kV 的中压器件的 BDOL 结果,来自 3 个生产批次的每种类型样品超过 60 个器件,在 BDOL 应力之前和之后零故障且参数变化可忽略不计(图. 2)。这一结果成功地证明了生产 MOSFET 的出色双极稳定性,这可能被认为比低压器件(例如 (650 – 1200) V)更严格,因为 SiC 外延层更厚,因此更有可能发生故障。存在基底面位错。

图 2.(左)BDOL 应力配置示意图、MOSFET 有源单元横截面以及导致 BPD 转换为 SF 的电子-空穴复合电流指示(右)3.3 kV 和 10 kV Wolfspeed 资格测试的 BDOL 电流与时间的关系中压生产 SiC MOSFET。

值得注意的是,如果 SiC MOSFET 一开始就没有任何 BPD,那么 SF 就无法成核和生长,并且不会发生双极退化。因此,减少和筛选BPD的发生对于确保SiC MOSFET的第三象限双极稳定性非常重要。尽管进行了数十年的研究,文献证据尚未表明如何以良好的方式加速双极稳定性,以便构建预测寿命模型,例如栅极氧化物磨损模型。幸运的是,大多数或所有双相稳定性故障发生在相对较短的时间内(BDOL 压力的几小时到几天,而不是几个月和几年)。因此,双极稳定性似乎最好采用早期故障率机制,而不是磨损机制。因此,为了确保采用第三象限操作的应用具有良好的双极稳定性可靠性,制造商必须依靠低 BPD SiC 外延和充分的筛选,并通过测试大样本量和大面积器件来证明这一点,幸运的是,测试周期相对较短。BDOL 压力时间。

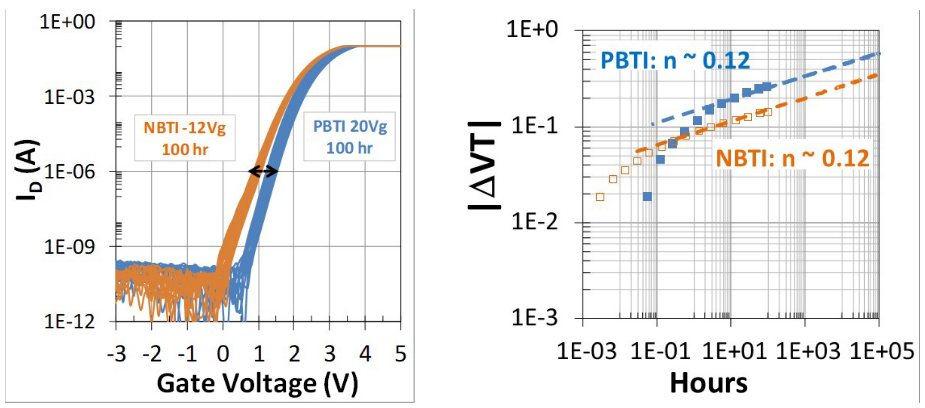

阈值电压稳定性。栅极偏置会导致 SiC MOSFET 的 VT 稳定性随时间漂移,从而改变器件的导通状态和/或阻断特性。这种效应通常称为正/负偏压温度不稳定性 (PBTI/NBTI)。BTI 可以发生在 Si 以及 SiC MOSFET 中,但这种效应通常在 SiC MOSFET 中更为明显,因为它们在氧化物界面处及其附近具有更高密度的陷阱,这些陷阱由氧化物电场填充、清空和/或创建。BTI会受到电场和温度的加速,并随时间呈现出弱幂律。Lichtenwalner 等人对生产 SiC MOSFET 中 BTI 的示例性表征。显示出约 0.12 的时间指数(图 3),这与具有氮化氧化物的 Si 器件(如 SiC)的时间指数相似。这种相似性表明 SiC 和 Si 器件的物理机制是相同的,即氧化物电荷陷阱填充和排空。寿命外推表明,BTI 预计在数千小时内仅漂移数百毫伏,但值得注意的是,与PECS应用中此类器件的典型开关电压相比,即使如此大的漂移也很小,因此预计不会明显影响系统性能。

图 3. 代表性 Wolfspeed Gen3 1200 V SiC MOSFET 的 BTI。(左)在长达 100 小时的累积恒定栅极偏压应力的应力时间内,漏极电流与栅极电压曲线随恒定栅极偏压而漂移,并具有中间读出点。PBTI 和 NBTI 的外推预测,在 150 °C 下加速恒定栅极偏置应力数千小时时,漂移仅为数百毫伏。

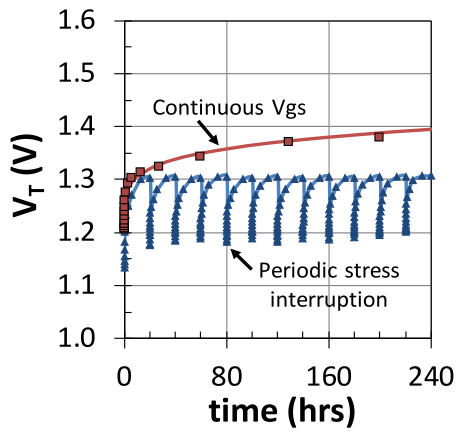

值得注意的是,在栅极偏置应力下观察到的VT漂移可以由长期VT漂移、瞬态VT变化和VT滞后或滞后变化组成。为了证明这种效应,图 4 显示了与中断偏压相比,恒定栅极偏压下 VT 如何随时间漂移,其中定期消除应力,并且允许器件在恢复应力之前松弛。这些行为之间的差异表明可恢复瞬态效应占主导地位,并且由界面退化引起的 VT 漂移相对较小。这说明在恒定栅极偏压应力下观察到的 VT 漂移有多少可能并不代表器件永久性退化,而是反映了临时参数漂移,这在典型开关应用中可能不太明显。

图 4. Wolfspeed Gen3 900 V SiC MOSFET 的 VT 与栅极偏置应力时间关系,显示了 150 °C 下连续 19 V 应力下的 PBTI,与定期消除应力时的 VT 响应进行了比较。这种差异表明可恢复瞬态效应占主导地位。

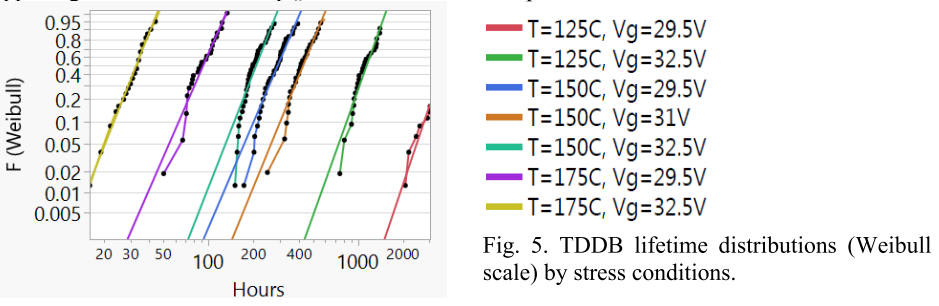

栅极氧化层磨损。SiC MOSFET 栅极氧化物磨损通过时间相关介电击穿 (TDDB) 测试来表征。Wolfspeed Gen3 1200 V MOSFET 上的 TDDB 数据通过具有高 Weibull beta 值的单个 Weibull 统计分布进行了很好的建模,这表明即使在高度加速条件下也具有良好的内在磨损行为,并且没有明显的外在缺陷群(图 5)。热化学模型(方程 1)很好地描述了 TDDB 数据与温度和栅极电压的关系,该模型已广泛用于 Si MOSFET,

其中 E 是栅极氧化物电场,T 是温度,ΔH0 是零施加栅极电场时的 Si-O 键强度,peff 是有效 Si-O 偶极矩。

图 5. 按应力条件划分的 TDDB 寿命分布(威布尔标度)。

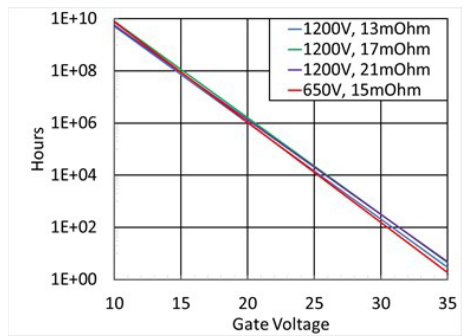

将此模型应用于多个 1200 V 和 650 V 完整生产器件,可得出所有器件在 175 °C、15 V 连续栅极偏压下的固有寿命预测约为 1E8 小时。这表明 Wolfspeed 器件的栅极氧化物寿命对于不同尺寸和电压等级是一致的(图 6),由于栅极结构和晶圆制造工艺的相似性,这是预期的。所得模型拟合参数与 Si 器件的相似,这表明 SiC 和 Si MOSFET 的栅极氧化物磨损机制相似。

图 6. 多个 Gen3 1200 V 和 650 V SiC MOSFET 的 TDDB 固有寿命外推。

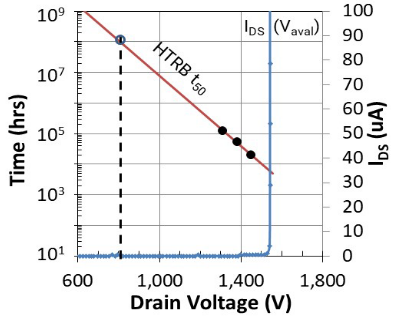

高温反向偏压 (HTRB)。在某些器件设计属性允许的情况下,SiC MOSFET 在阻断条件下的寿命可以通过加速 HTRB 测试 (ALT-HTRB) 来表征。SiC MOSFET 在雪崩电压下表现出相对较低的漏电。器件的设计通常在雪崩电压和器件的额定电压之间留有一定的余量,以确保针对高漏极偏置电压(尤其是瞬态过压)的可靠性和鲁棒性。该裕度可以在高于额定电压但低于雪崩电压的情况下加速漏极偏置测试。在这种情况下,器件 JFET 间隙中的氧化物电场可能足够高,足以引起栅极氧化物磨损。恒定偏压 ALT-HTRB 测试表明,器件显示相对较低的栅极和漏极泄漏,直到发生突然的栅源短路故障,几乎没有前兆信号,类似于 TDDB 中发生的情况。

图 7.(左轴)150 °C 下 ALT-HTRB 寿命中值与漏极偏置的关系,外推至 800 V 下约 1E8 小时。(右轴)代表性器件的漏极电流与电压的关系,显示雪崩电压 > 1450V。

图 7 显示了 Wolfspeed Gen3 1200 V SiC MOSFET 的 ALTHTRB 测试结果。ALTHTRB 寿命数据使用 Weibull 统计数据和线性 V 模型进行拟合,如上文针对 TDDB 所述。结果表明,在 175 °C 和 800 V(这是典型高可靠性 PECS 应用中经常使用 1200 V 器件的总线电压)下,预计平均寿命约为 1E8 小时。

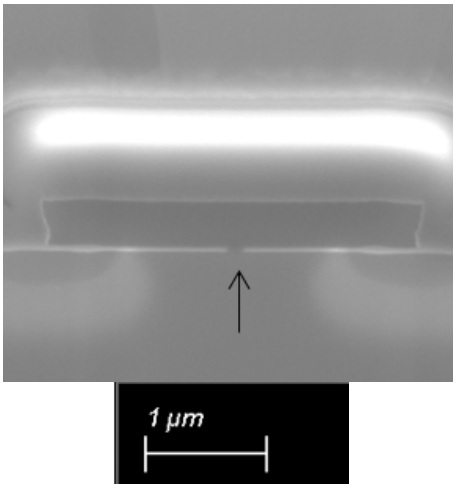

图 8. 在 ALT-HTRB 应力测试中已达到寿命终点的 Wolfspeed SiC MOSFET 失效部位的 FIB 横截面的扫描电子显微镜图像。箭头突出显示了加速寿命应力测试期间发生的氧化物击穿的位置。

失效分析表明,ALT-HTRB 失效机制是 JFET 间隙中心的栅极氧化层击穿(图 8)。这是预料之中的,因为这是反向偏压下栅极氧化物电场最高的位置。失效分析没有发现边缘终端击穿或 SiC 击穿的证据(图 9),这表明栅极氧化物磨损是影响反向偏压可靠性的唯一失效机制。这支持使用线性 V(在本例中为漏极电压,与栅极电压直接相关)模型进行 ALT-HTRB 寿命预测,如上所述。

图 9. Wolfspeed SiC 平面 MOSFET 的横截面示意图,表明故障分析表明 ALT-HTRB 应力期间发生的唯一故障机制是栅极氧化物击穿,而不是边缘终端击穿或 SiC 击穿。

标准化

SiC PECS 器件的这些有趣的可靠性方面一直在推动行业联盟紧急发布可靠性测试和鉴定的指南和标准,尽管方法论正在积极开发并且新数据正在发布。国际电工委员会(IEC)发布了关于双极退化和偏置温度不稳定性的国际标准可靠性测试方法文件。JEDEC 已发布有关偏置温度不稳定性评估的文件、测量 SiC MOSFET 的阈值电压、代表数据表中 SiC MOSFET 的开关损耗,以及最近用于评估 dV/dt 鲁棒性的文件。欧洲电力电子中心 (ECPE) 修订了其关于机动车辆电力电子转换器单元中使用的功率模块资格的文件,现在包含关于基于 SiC 的功率模块资格的附件部分,其中包括功率循环的具体指南、高温栅极偏压、高温反向偏压、动态反向偏压等。

即使对这些文件进行粗略的审查也表明,这些联盟之间尚未在可靠性压力程序的某些主要方面达成一致,当然也没有在 AEC-Q101 或 JEDEC JESD47K 等标准资格指南方面实现一致。然而,可以肯定的是,这些和其他行业联盟将继续非常积极地致力于修订现有的 SiC PECS 指南和标准并发布新的指南和标准。JEDEC 小组委员会 JC-70.2“SiC 电力电子转换半导体标准”正在积极制定有关双极稳定性、栅极氧化物可靠性和 HTRB 的文件。从历史上看,标准组织首先发布指南,然后发布标准。这种做法的优点是,首先更容易就指南达成广泛共识,然后可以作为调整标准(例如资格)的基础。在制造商和客户之间实现广泛的一致具有挑战性,但对于建立信心至关重要,因为 SiC 继续在高可靠性和大批量应用中令人印象深刻地广泛采用。

总结

高可靠性应用中对 SiC PECS 器件的需求快速增长,加上 SiC 中的高芯片数量、恶劣的工作条件和独特的可靠性考虑因素,导致对彻底的可靠性表征和行业联盟标准化的需求非常高。SiC 的关键失效机制,包括 BTI、双极稳定性和栅极氧化物(在栅极偏压和反向偏压下),已被制造商和其他研究人员充分表征。在应力程序、寿命建模和对现场可靠性影响的协调方面正在取得良好进展。几个行业联盟已经发布了许多指南和标准,并且很快还会发布更多指南和标准。下一个挑战将是这些联盟之间更广泛的协调——需要做更多的工作,而且即将完成。

审核编辑:汤梓红

-

MOSFET

+关注

关注

144文章

7080浏览量

212658 -

半导体

+关注

关注

334文章

26988浏览量

215983 -

肖特基二极管

+关注

关注

5文章

911浏览量

34753 -

功率器件

+关注

关注

41文章

1727浏览量

90304 -

SiC

+关注

关注

29文章

2757浏览量

62430

原文标题:SiC 功率器件的可靠性和标准化

文章出处:【微信号:芯长征科技,微信公众号:芯长征科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

什么是失效分析?失效分析原理是什么?

未来发展导向之Sic功率元器件

SiC功率器件概述

浅析SiC功率器件SiC SBD

SiC功率器件SiC-MOSFET的特点

【罗姆SiC-MOSFET 试用体验连载】SiC MOSFET元器件性能研究

SiC器件中SiC材料的物性和特征,功率器件的特征,SiC MOSFET特征概述

SiC功率器件中的失效机制分析

SiC功率器件中的失效机制分析

评论