本次与大家分享的是世健和ADI联合举办的《世健·ADI工业趴:放飞思路,解封你的超能力》主题活动的二等奖文章:《采用ADI公司ADF4107芯片研制C波段频率合成器》。

作者:RF-刘海石

01

背景

本文主要是采用ADI公司的ADF4107频率合成器芯片,设计一款C波段本振源,主要用于Ku波段卫星下变频。具体应用详情客户没有透露太多,这个我也明白,因为这个是某研究所的项目,只说了频率范围是4.8-5.2GHz。这款产品目前在应用中,下面我们分享下怎么设计这个频率合成器。

02

产品简介

首先在这里简单叙述下锁相式频率合成器的原理。

锁相环是一个相位负反馈系统,利用锁相技术来产生所需要的频率,是第二代频率合成技术。早期的间接频率合成器是利用模拟锁相环,它在输出较高的频率时,需要大量的混频器和分频器,以及带通滤波器,因此它的缺点很明显,而且很难弥补。数字锁相环弥补了模拟锁相环的这些缺点,数字锁相环由鉴相器,分频器,环路滤波器,压控振荡器等几部分组成。

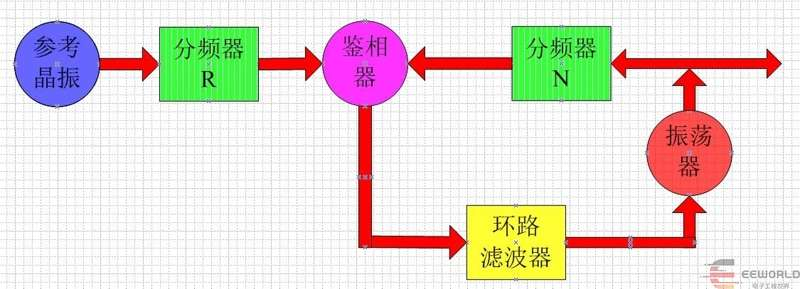

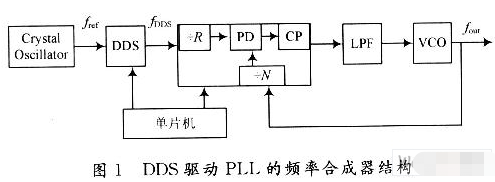

下面是一个单环整数分频锁相环的框图。如图1所示:

图1.单环整数分频锁相环框图

由上图很容易看出数字锁相环主要由鉴相器,环路滤波器,压控振荡器和分频器组成。现代的锁相环芯片内部包括电荷泵电路。

基本原理:参考晶振产生稳定的基准频率,然后被参考分频器R分频,分频后的频率就是鉴相频率,作为鉴相器的一个输入信号。鉴相器检测鉴相频率与N分频器输出频率的相位差,输出平均值与该相位差成比例的直流电流。鉴相器输出的脉冲电流经过滤波和积分产生调节电压,该电压驱动外接的压控振荡器,来增加或者减小输出频率,直到鉴相器的平均输出为零。

环路滤波器就是低通滤波器,有两种方式:

2、有源滤波器,通常由电阻、电容和运算放大器组成。

具体详细设计,请参考锁相环书籍或者其它文献,这里不多叙述了。

接下来,设计如何实现一个C波段的频率合成器,该频率合成器技术指标如下:

频率范围:4.8GHz---5.2GHz

频率步进:1MHz

杂散抑制:≤-50dbc

谐波抑制:≤-50dbc

相位噪声:≤-60dbc/Hz@ 1kHz

≤-75dbc/Hz@ 10kHz

≤-110dbc/Hz@ 100kHz

输出功率:≥10dbm

工作温度:-40~+50℃

03

设计方案

鉴相器选择

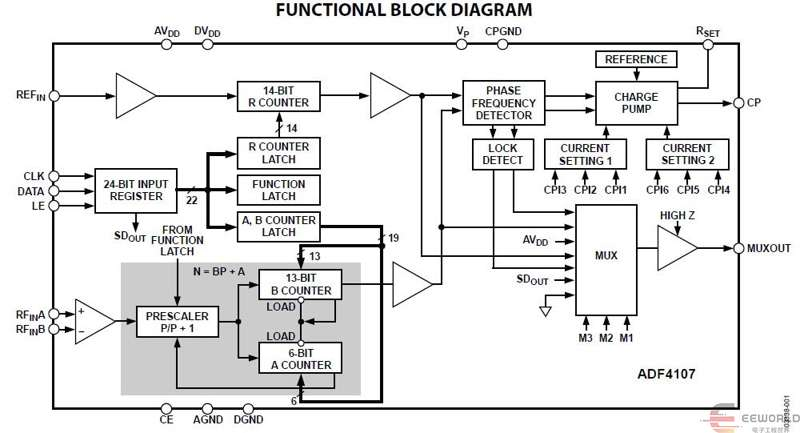

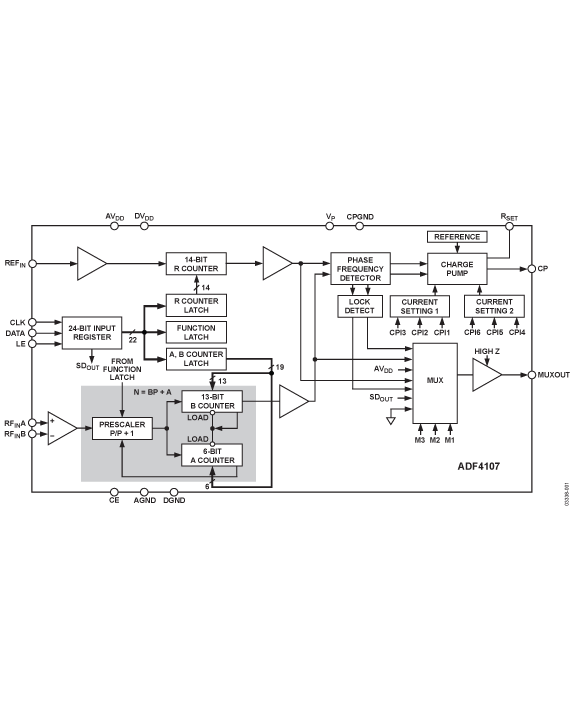

鉴相器选择,在所用的频率范围内,尽量低的归一化噪声基底,具有良好的杂散指标,市面上的种类也比较多,如Analog Devices、Hittite、Maxim、Ti等品牌。本产品输出频率在C波段,经过对比,决定采用ADI公司的ADF4107芯片,该芯片具有高达7GHz的带宽,在芯片内部集成了一个低噪声数字鉴相器,内部一个精密的电荷泵,可编程预分配器,一个前置双模分频器,和可编程计数器。单电源供电,供电电压2.7~3.3V,市面很多降压芯片都可以满足。采用3线串口控制,使用起来非常方便。如图2所示。ADF4107芯片内部示意图:

图2.ADF4107内部示意图

VCO选择

VCO选择,本产品选的的压控振荡器芯片为:Z~communications公司的V950ME08-LF,技术参数如下:

1、输出频率:4450----5350MHz

2、工作电压:+5V

3、工作电流:30mA

4、输出功率:0dbm

5、压控灵敏度:120MHz/V

6、压控范围:0~9.5V

7、相位噪声:-87dbc/Hz@10KHz

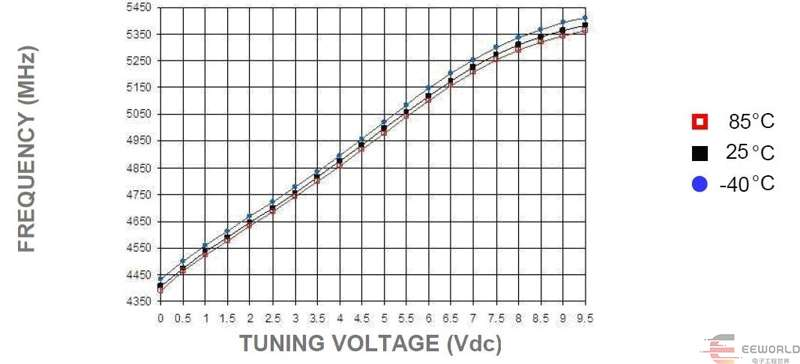

下面是厂商给出的压控频率曲线,如图3所示:

图3.压控振荡器的压控曲线

环路滤波器

环路滤波器在锁相环电路中作用至关重要,它与锁相环各项指标密切相关。调整环路滤波器的元件参数,可以有效的改善锁相环的相位噪声和杂散指标。由于ADF4107的电荷泵最大在5V左右,根据VCO压频曲线,输出频率在5.2GHz时,压控电压在7V以上,所以需要采用有源环路滤波器。

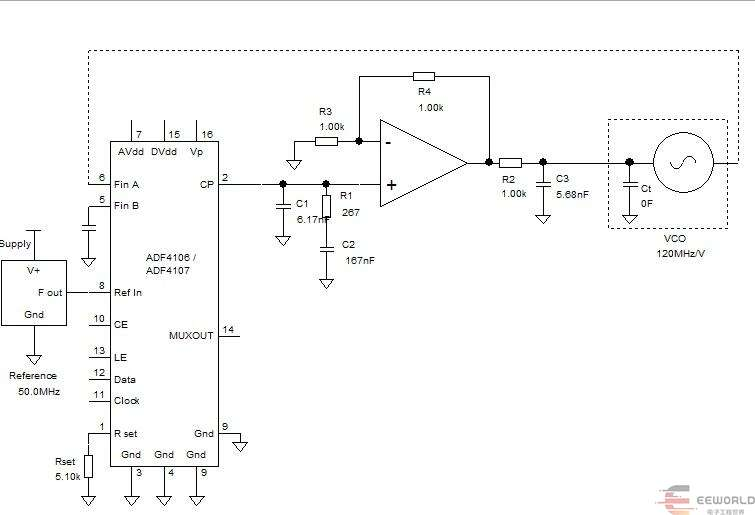

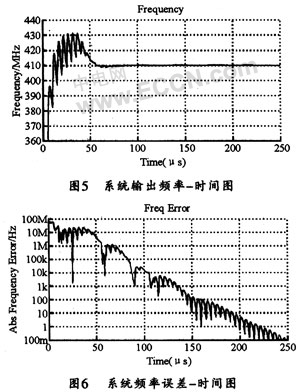

设计环路滤波器时可以借助ADI公司提供的仿真软件ADISimPLL 来进行设计,如图4所示:

图4.ADISimPLL软件仿真电路图

通过ADISimPLL软件仿真得出的环路滤波器参数只是一个初始值,在实际电路中,按照这个初始值制作的锁相环路很有可能出现不能锁定,或者达不到系统技术指标等问题,一次必须对环路参数进行反复调整使之达到最佳。

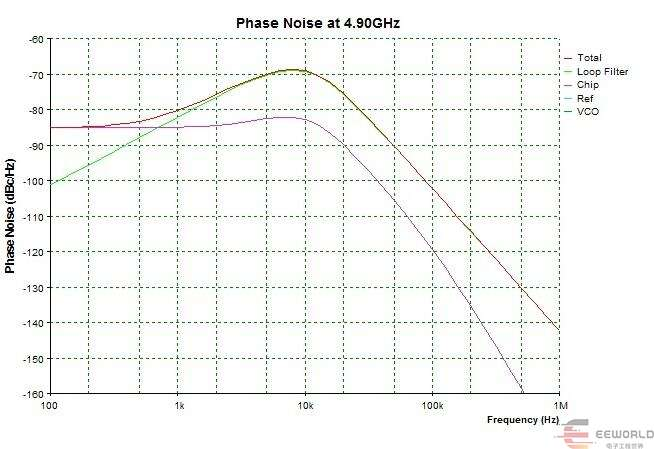

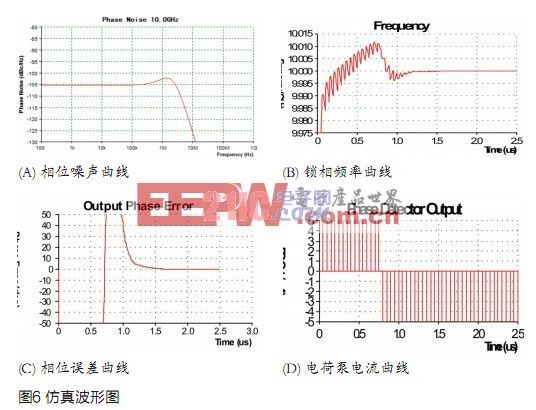

下图是仿真的相位噪声,如图5所示:

图5.仿真相位噪声曲线

图5是仿真出来的相位噪声,中心频率4.9GHz,相位噪声为-80dbc/Hz@1kHz。

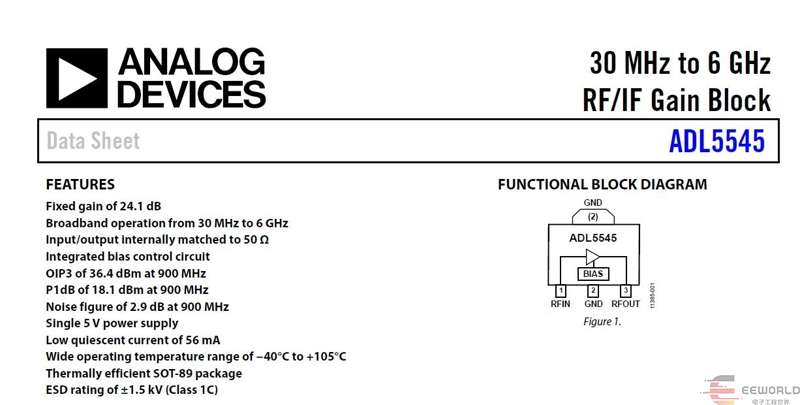

由于技术要求频率合成器输出功率>10dbm,VCO输出只有0dbm,在经过功率分配,最终输出只有-3dbm,所以在VCO输出端口增加推动放大器,放大器采用ADI公司的ADL5545。如图6所示:

图6.ADL5545芯片介绍

如图6可知,该放大器的带宽覆盖了30MHz~6GHz,输入输出端口内匹配到50欧姆,这也省去了外部调节匹配的麻烦,为产品设计节省了宝贵的时间。P1db:+18dbm@900MHz,就在5GHz的频段P1db也在10dbm以上。电路简单,+5V单电源供电,很好的兼容了系统设计。

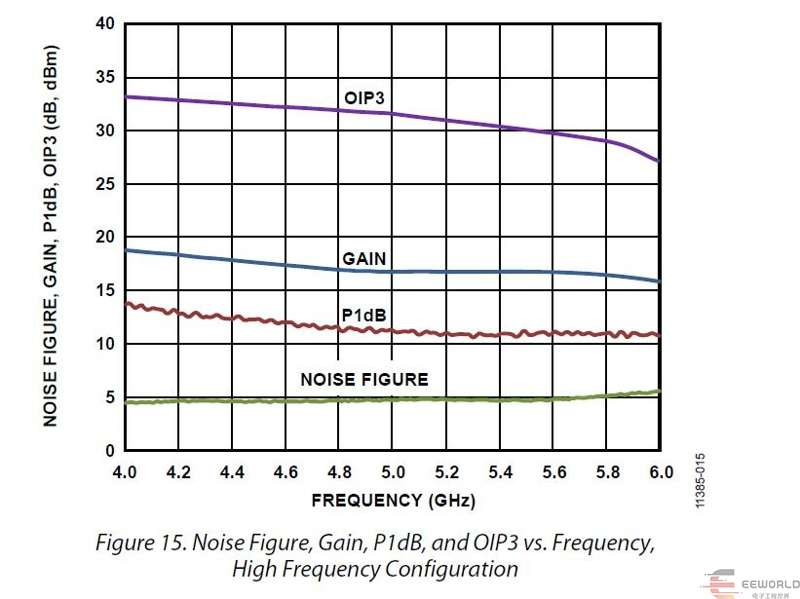

具体参数如图7所示:

图7.ADL5545芯片测试图

如图7所示,给出的频率范围是4GHz~6GHz,正好所设计的频率合成器落在这个频率范围内,如图知:在4.8GHz~5.2GHz,该放大器增益大概有17db,P1db在10dbm以上,OIP3大于30dbm,证明该放大器的线性度良好,所以采用此放大器进行设计。

04

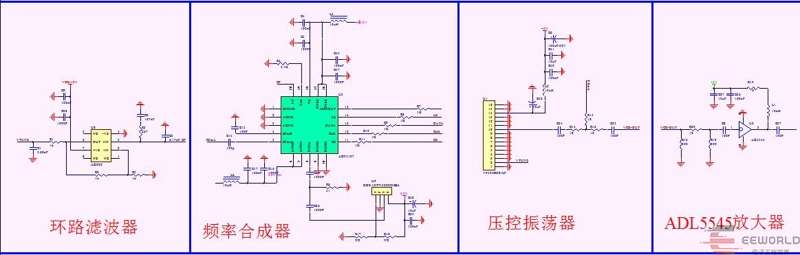

如图8所示,为本项目设计的C波段频率合成器电路图。频率合成器采用ADF4107芯片,外围电路参考技术手册。参考晶振采用KDS温补晶振,如需更高精度,可以采用恒温晶振。VCO采用Z~communications公司的V950ME08-LF,前面已经介绍了,这里不再叙述了,环路滤波器采用有源滤波,用ADI公司的AD820运算放大器设计,可以参考ADI SimPLL软件进行设计,最后功率放大采用ADI公司的ADL5545进行放大,连起来就是一个完整的频率合成器电路。单片机电路我没有给出(我用的是STC单片机),可以用不同型号的单片机去控制,3线串口,很简单。

图8.频率合成器电路图

在这里主要说下,在VCO输出与放大器之间加入了π衰减,主要调节射频输出的增益,要保证ADL5545的线性度。

05

背景

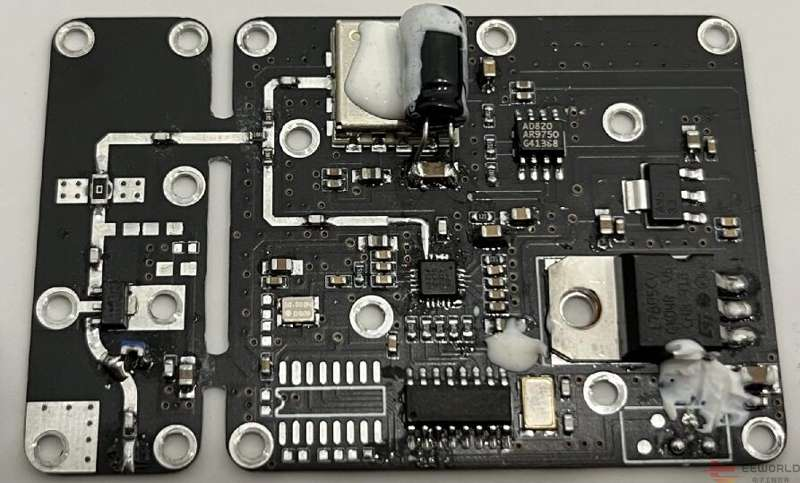

该PCB采用RO4350B高频板材设计,介电常数3.66,板材厚度0.762mm,如图9所示:

图9.频率合成器PCB

外壳采用6061铝合金,CNC加工,屏蔽盒内部隔档,防止互相串扰。

屏蔽盒尺寸:长800mmX宽55mmX高23mm,如图10所示:

图10.频率合成器实物

06

实际测试

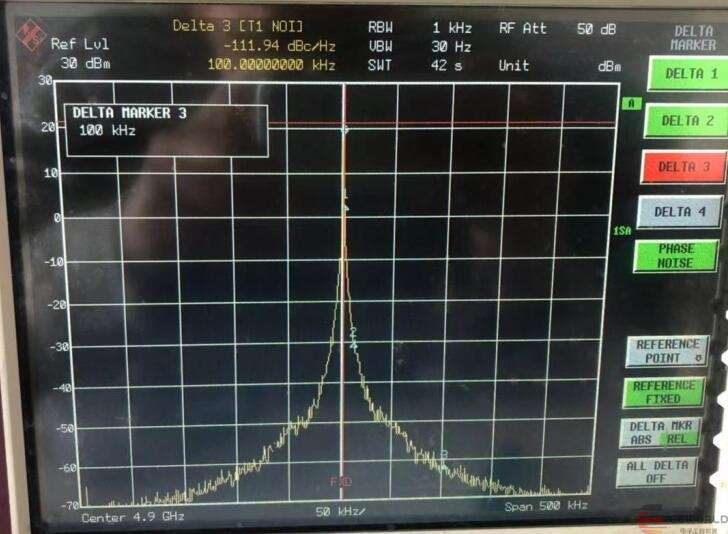

采用R&S频谱仪进行相位噪声测试如图11所示:

图11.相位噪声测试图

如图11所示,中心频率4.9GHz,测试相位噪声:-111dbc/Hz@100k。

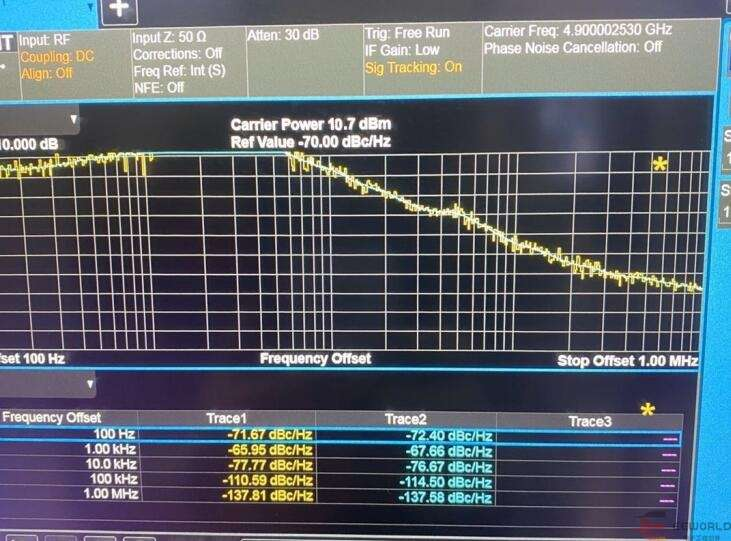

交付客户,客户自己测试的频率合成器相位噪声,如图12所示:

图12.客户测试相位噪声

中心频率4.9GHz,测试相位噪声:

-65.9dbc/Hz@1k

-77.7dbc/Hz@10k

-110dbc/Hz@100k

通过以上测试对比,基本满足客户需求,这个源的指标还可以提升,但是需要反复调整环路滤波器,需要大量的时间。

07

总结调试中遇到的问题

在本次设计中,最大的工作量就是调试环路滤波器,因为环路滤波器决定了频率合成器的好坏,也可以说环路滤波器是频率合成器的核心。所以需要反复调整,达到最佳。

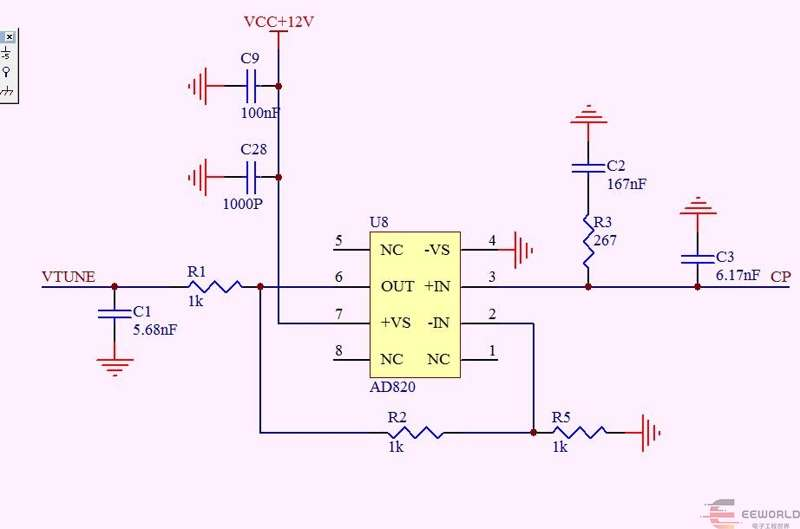

下面按照实际电路来分析,如图13所示:

图13.环路滤波器电路图

1、环路带宽的调整

图13电路中,C1和C3对环路带宽的影响最大,电容增大,带宽变窄,电容减小,带宽变宽。

2、带内插损的调整

图13电路中,R1对带内插损影响最大,电阻值增大,插损变大,电阻值减小,插损减小。

3、带内波动的调整

图13电路中,R3和C2对带内波动的影响较大,增大电阻,带内波动减小,但是电阻和电容同时也会影响环路带宽和插损,所以要结合起来调整。

还有个重要的问题。

在设计的时候在电路中加了MAX232,作为上位机和频率合成器的通信,调试的时候发现,MAX232振荡产生了开关频率,然后调制到载波两端,一开始以为是鉴相器泄漏的,继续调整环路,经过反复调整都没有改善,后来才发现是MAX232振荡的原因,所以PCB板上把MAX232去掉了,最终解决了这个问题。

建议:频率合成器内部最好不要用DC-DC电源直接给频率合成器或者VCO供电,认可牺牲效率也要用线性电源,除非能把开关频率彻底抑制,否则就会调制到载波两端,很难弄掉。

以上是如何设计一个频率合成器的所有过程,至于一些细节理论问题还需参考书籍和文献,最主要的就是环路滤波器的调试,方法我已经分享了。调试就要看基本功了。

免责声明:本文仅代表作者个人观点,与主办方ADI、Excelpoint世健以及EEworld无关。

-

芯片

+关注

关注

459文章

51715浏览量

430894 -

ADI

+关注

关注

147文章

45987浏览量

254808 -

合成器

+关注

关注

0文章

275浏览量

25725

发布评论请先 登录

相关推荐

ADI发布相位噪声性能的PLL频率合成器ADF4153A

ADI推新款频率合成器ADF4371 支持各种射频/微波系统设计

频率合成器ADF4360-4在GPS信号源设计中的典型应用介绍

ADF4108在宽带X波段频率合成器中的设计应用

单片机控制的ADF4106锁相频率合成器设计

射频锁相频率合成器的设计与仿真

ADI推出新款PLL频率合成器ADF4151和ADF4196

基于DDS芯片和集成锁相芯片构成的宽频合成器设计

ADF4107 PLL频率合成器

采用ADI公司ADF4107芯片研制C波段频率合成器

采用ADI公司ADF4107芯片研制C波段频率合成器

评论