传统带隙电压基准

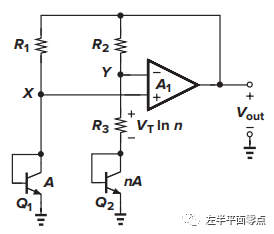

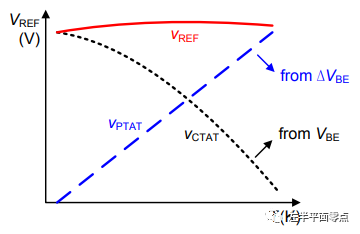

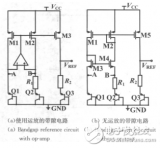

传统的带隙电压基准如图1所示,双极型晶体管基极-发射极电压差ΔVBE具有正温度系数,而双极型晶体管基极-发射极电压VBE具有负温度系数,如果将两个电压进行相加,理论上就可以通过设计合适的参数实现零温度系数电压,如图2。具体可以参考拉扎维模集的第12章的内容。

图2(来源于公开资料)

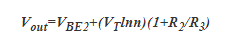

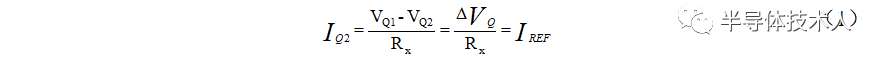

图1电路输出电压为:

其中当ln n (1+R2/R3 )约等于17.2时可以实现输出电压Vout的零温度系数。于是该电路有双极型晶体管不同的电流密度比例n以及R2、R3电阻的阻值3个设计因子。

全CMOS带隙电压基准

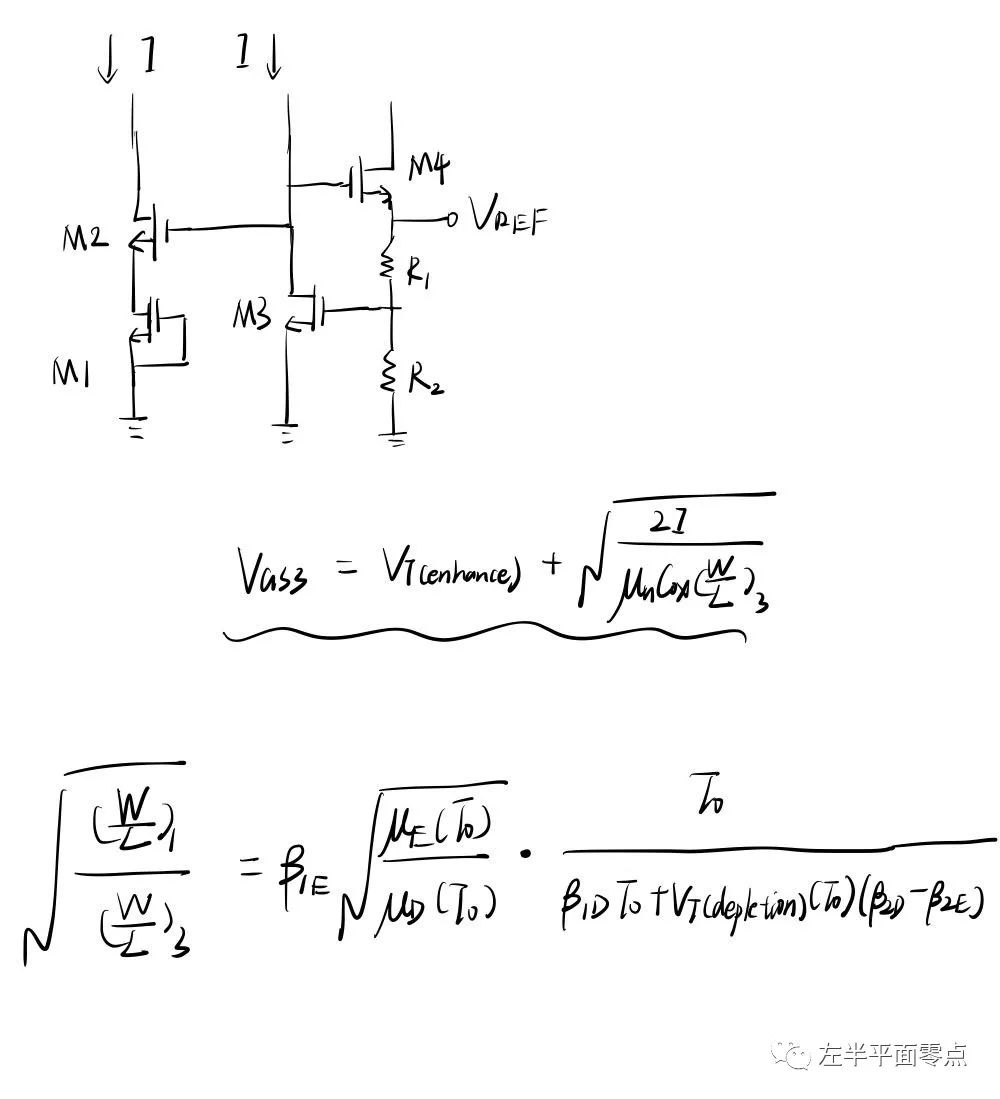

与利用双极型晶体管的基极-发射极电压差ΔVBE、基极-发射极电压VBE实现正负温度系数抵不同,全CMOS带隙电压基准利用了增强型MOS与耗尽型MOS阈值电压不同的原理来实现电压基准。MOS的阈值电压均呈现负温度系数,但增强型MOS的阈值电压>0,耗尽型MOS的阈值电压<0。

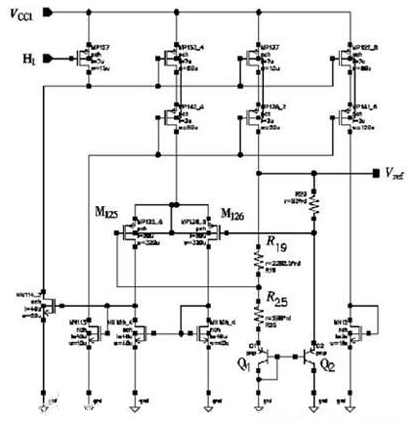

图3

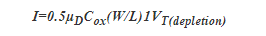

如图3,其中M1、M2为耗尽型MOS,处于常开状态,此支路必然导通,设电流为 I ,则I 可以表示为 (其中VT(depletion)为耗尽型MOS的阈值电压、μD为耗尽型MOS的电子迁移率) :

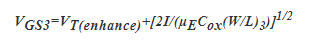

其中M3为增强型MOS,假设使M3通过的电流也为I ,那么其栅源电压可以表示为(其中 VT(enhance)为增强型MOS的阈值电压、μE为增强型MOS的电子迁移率):

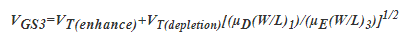

还可以写为:

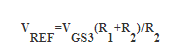

基准电压为:

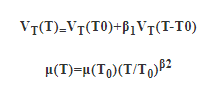

而MOS的阈值电压以及电子迁移率都会随温度变化,可以写为以下关系(其中β1为MOS阈值电压的温度系数、β2为电子迁移率的温度系数,T0为常温):

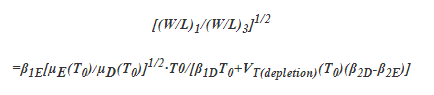

把这两个关系式代回VREF的表达式中,或者代回VGS3计算量更小一些,并对温度T求导,再令其为零。可以自己试着推导一下,公式太长懒得敲了,就只把结论给出来叭,M1与M3的尺寸关系需满足(其中β1E 、β2E为增强型MOS的阈值电压温度系数和电子迁移率温度系数,β1D 、β2D为耗尽型MOS的阈值电压温度系数和电子迁移率温度系数):

结束语

突然觉得学模拟真的很难,之前总觉得看完了拉扎维的模集自己好像没什么东西学了,但现在发现并不是这样。拉扎维老先生的模集真的是一本圣经!可以说早上看跟晚上看有不一样的收获、同男生一起看跟同女生一起看有不一样的收获甚至吃饭看跟上厕所看也有不一样的收获,哈哈哈。所以感觉一方面要多读几遍,另一方面模拟集成电路有意思的电路真的很多,拉扎维老先生也不可能把所有的东西全写上去(都已经几百页厚了你还想怎么样?),所以说还要读各种各样的文章,坚持下去就好了,总有一天会派上用场。

-

集成电路

+关注

关注

5380文章

11377浏览量

360759 -

CMOS

+关注

关注

58文章

5675浏览量

235104 -

电压基准

+关注

关注

1文章

95浏览量

20471 -

晶体管

+关注

关注

77文章

9629浏览量

137808

发布评论请先 登录

相关推荐

CMOS带隙基准电压源曲率校正方法

CMOS带隙基准电压源中的曲率校正方法

用于音频AD转换器的CMOS带隙电压基准源

全CMOS带隙电压基准的工作原理

全CMOS带隙电压基准的工作原理

评论