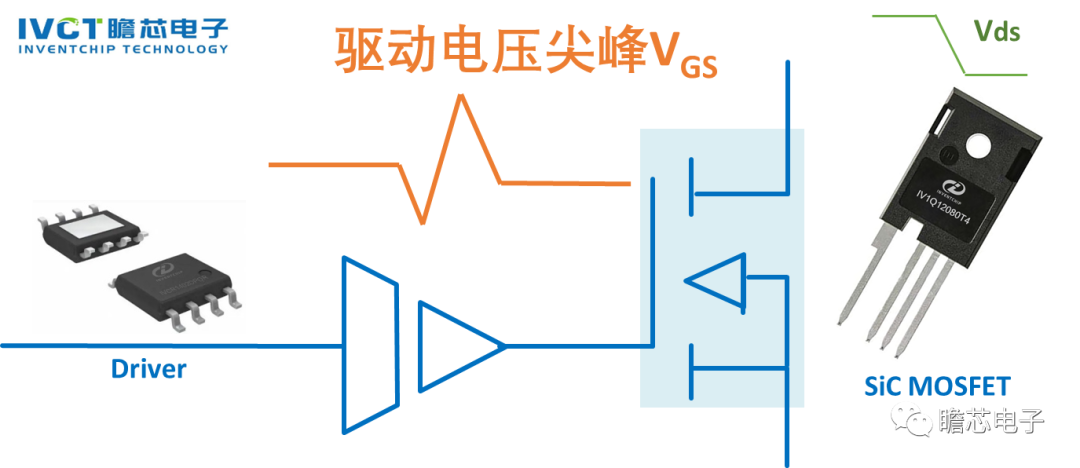

驱动电压尖峰复现与分析

【背景】

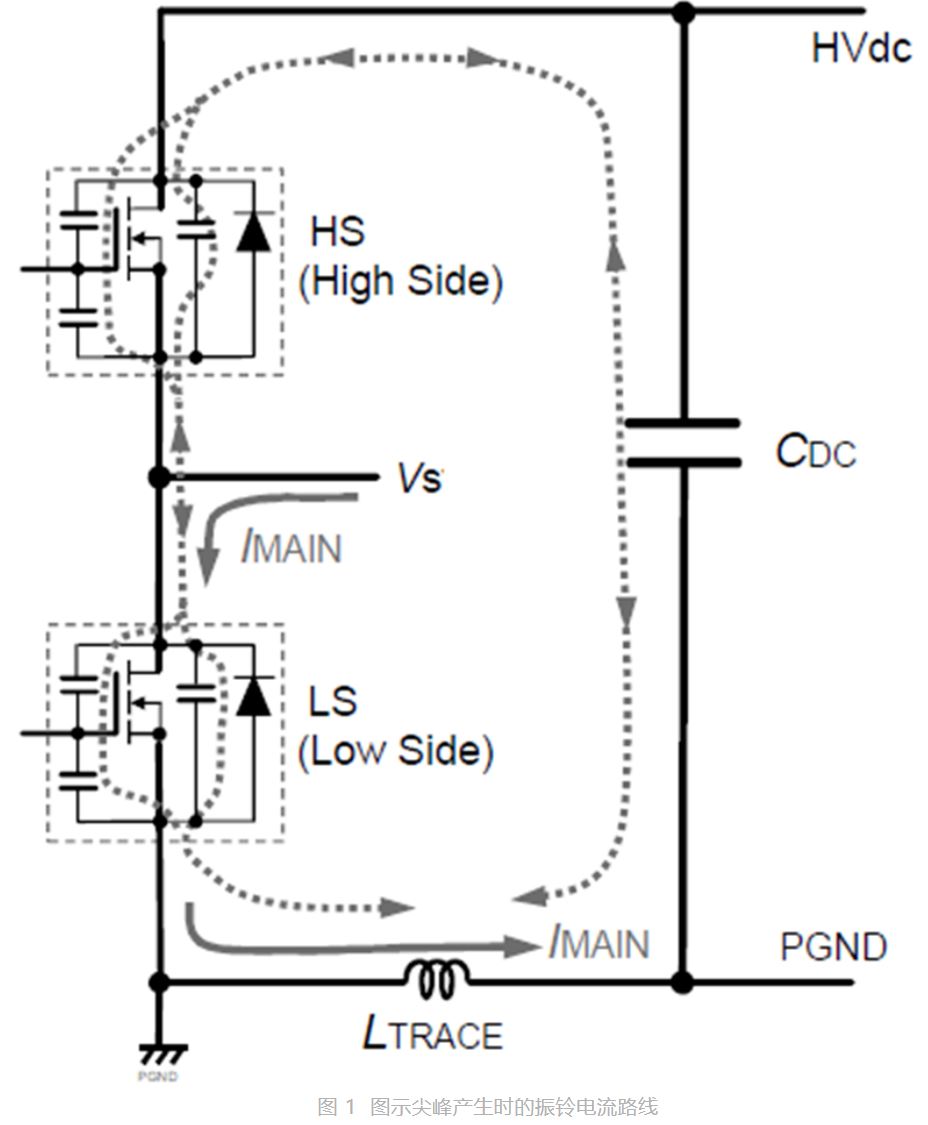

高频、高速开关是碳化硅(SiC) MOSFET的重要优势之一,这能显著提升系统效率,但也会在寄生电感和电容上产生更大的振荡,从而让驱动电压产生更大的尖峰。

驱动电压尖峰会对系统有诸多不良影响。首先,驱动电压尖峰若超出SiC MOSFET的安全驱动电压范围,可能引发器件误开关,甚至损坏器件。其次,尖峰电压可能产生电磁干扰,影响系统EMC指标。最后,驱动电压尖峰带来的高频震荡还会导致电流波形不稳定,从而影响系统的性能和稳定。

因此,设计可靠的驱动电路来抑制的驱动电压尖峰,成为发挥SiC MOSFET优势特性的关键课题。为此,我们首先测试复现驱动尖峰波形并分析原因,然后采取相应措施来抑制尖峰。本篇主讲第一部分:驱动电压尖峰复现与分析。

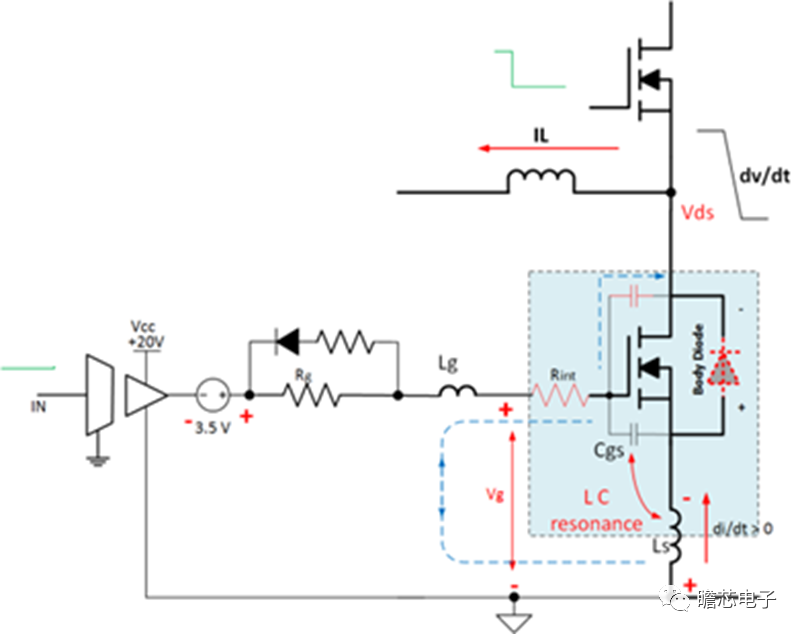

双脉冲测试方法与设备

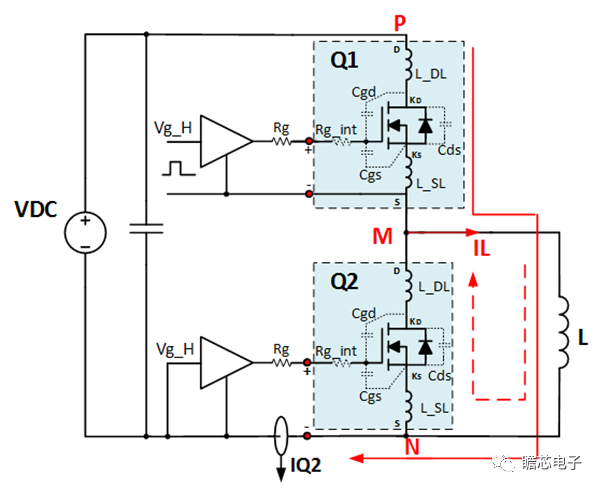

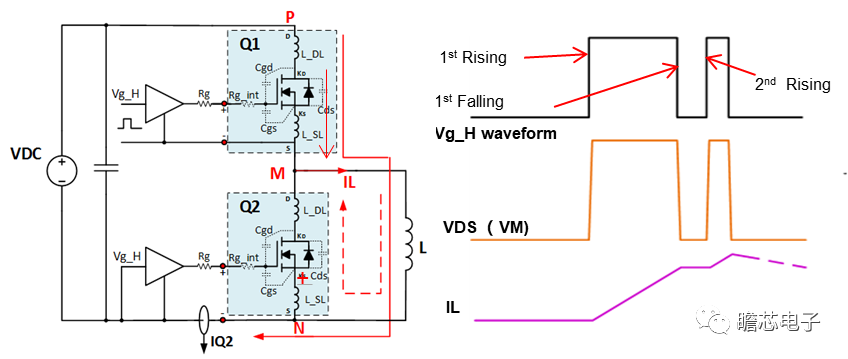

瞻芯电子采用经典的双脉冲测试方法,来复现SiC MOSFET的开关过程中驱动电压尖峰,以便分析原因和采取对策。在双脉冲测试电路中,Q1和Q2为瞻芯电子1200V 80mΩ SiC MOSFET(IV1Q12080T3/T4),下管Q2始终保持关断,上管Q1则进行开关动作。当上管Q1开通时电流路径为红色实线;当上管Q1关断时电流路径为红色虚线,如图1:

图1:双脉冲测试电路

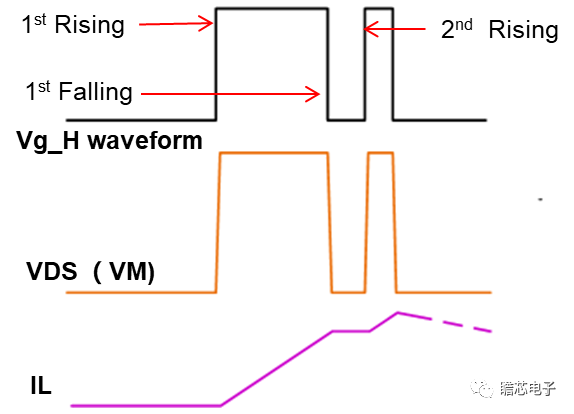

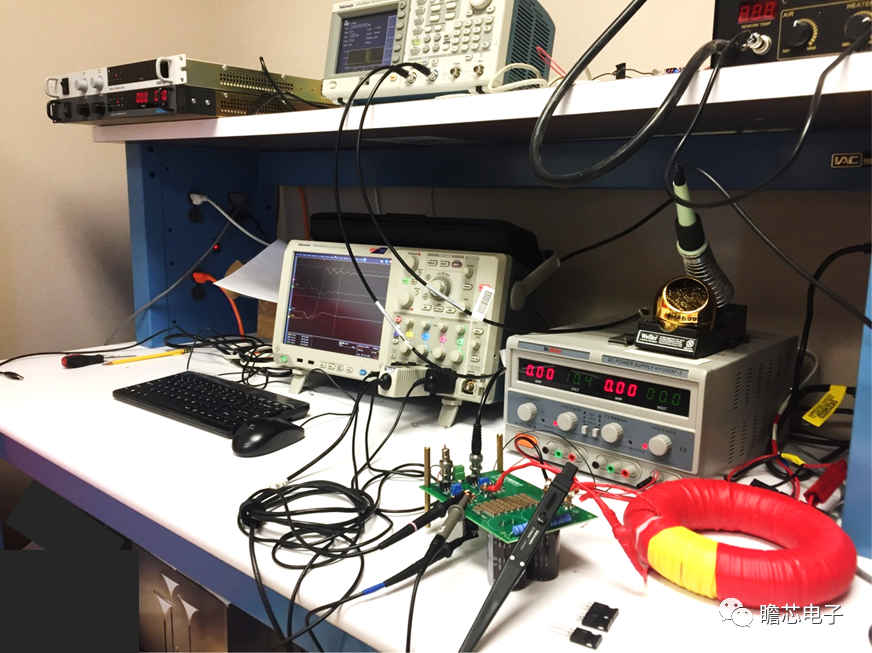

以上测试中,通过开关上管Q1,来测试下管Q2因寄生电感和米勒效应产生的驱动电压尖峰,如下示意图2:

图2:双脉冲测试过程

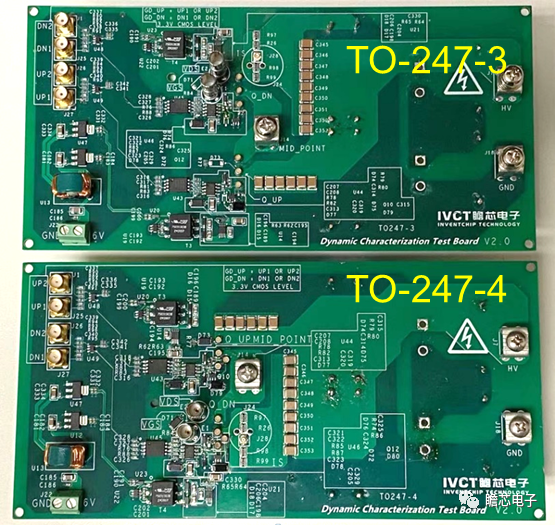

为了消除PCB板的寄生参数对测试波形的影响,瞻芯电子针对2种封装:TO247-3和TO247-4,分别制作了2块双脉冲测试板,如下图3:

图3:双脉冲测试板

具体的测试设备配置,包括信号发生器、直流电源、负载电感、示波器以及高带宽的非隔离探头或光隔离探头,其中非隔离探头采用最小接地环,从而取得更准确的测试结果,如下图4:

图4:测试设备环境

驱动电压尖峰复现

1、用0V关断电压时的参考电路与波形

如果不采取抑制尖峰措施,则驱动电路如下图5:

图5:0V关断且不加钳位的驱动电路

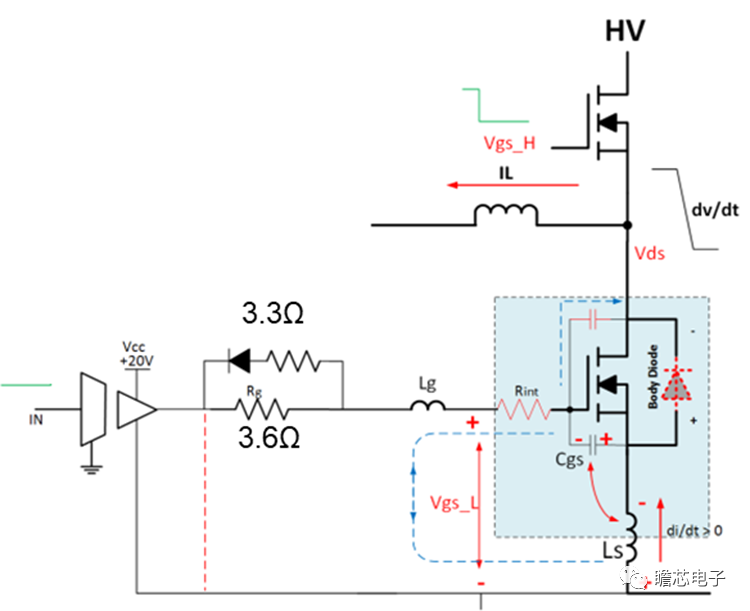

当关闭上管Q1的过程中,测试下管Q2的栅极(Gate)和源极(Source)引脚之间的电压(Vgs),出现较大的驱动电压(Vgs)负尖峰(-4.9V)和正尖峰震荡,如下波形图6:

图6:0V关断且不加钳位的驱动波形

以上波形图中,负压尖峰按不同成因分为两段:第一段是当Vds下降过程中dv/dt较大,因米勒电容放电,放电电流在Rg上产生压降,而让Vgs产生下拉负尖峰;第二段在Vds下降到0V后,Vgs出现负尖峰和正尖峰震荡,这是体二极管续流的di/dt在源极引脚的寄生电感产生。

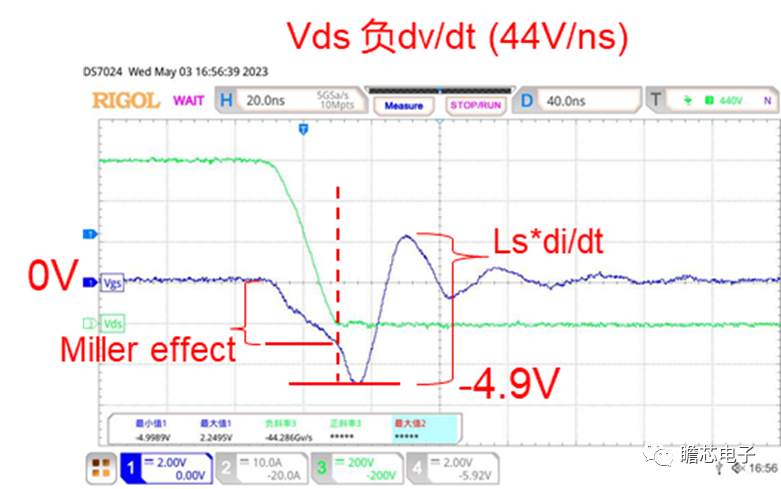

2、用-3.5V关断电压时的参考电路与波形

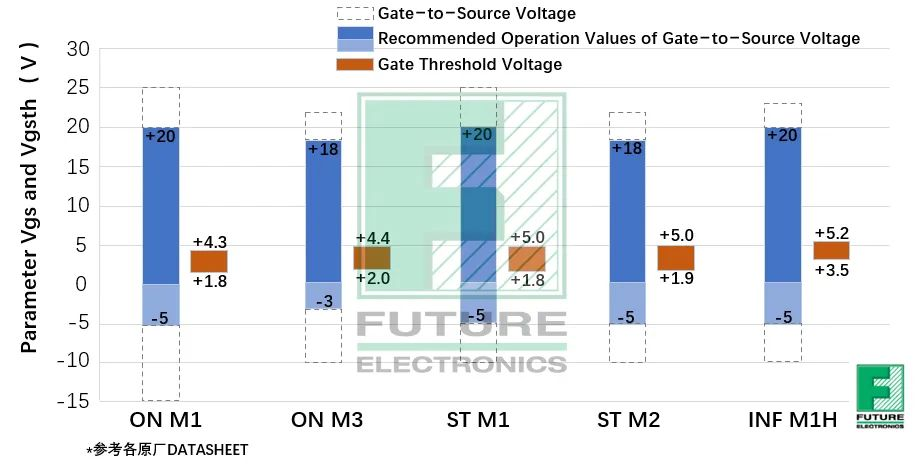

瞻芯电子的SiC MOSFET推荐断负压范围是-3.5V~-2V,这里选择最低值-3.5V电压驱动,来测试串扰引发的尖峰,如下图7:

图7:-3.5V关断且不加钳位的驱动电路

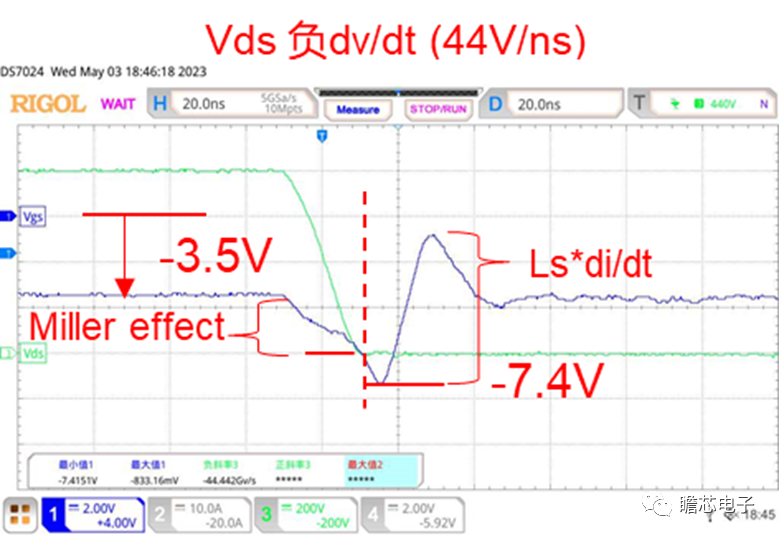

当上管Q1关断时,如下波形图7所示:绿色的Vds降低到0V过程中,蓝色的下管Q2的Vgs因Q2的米勒电容Cgd放电,进而在驱动电阻Rg上产生压降,即为测试波形中-3.5V下方的负尖峰。在Vds下降到0V后,下管Q2的Vgs又因源极寄生电感和di/dt,而产生更低的负尖峰和正尖峰震荡。

图7:-3.5V关断下管Q2时, 关断上管Q1

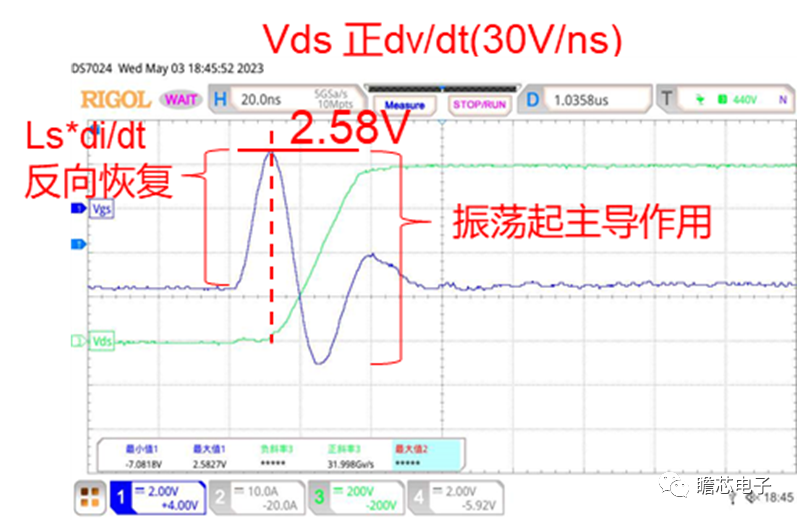

当上管Q1开通时,如下波形图8,在绿色Vds为0V的阶段,蓝色的下管Q2的驱动电压Vgs因体二极管电流转移和反向恢复,而在源极寄生电感上产生较大正尖峰(2.58V)和震荡。在Vds上升的阶段,Vgs尖峰主要由Cgs与寄生电感导致的震荡。

图8:-3.5V关断下管Q2时, 开通上管Q1

综合上述分析,串扰尖峰主要有2方面原因:

1、高dv/dt时的米勒电效应; 2、高di/dt在源极引脚寄生电感上产生的震荡。

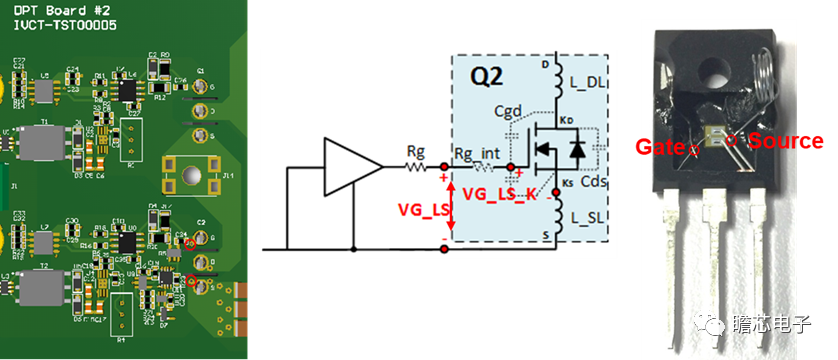

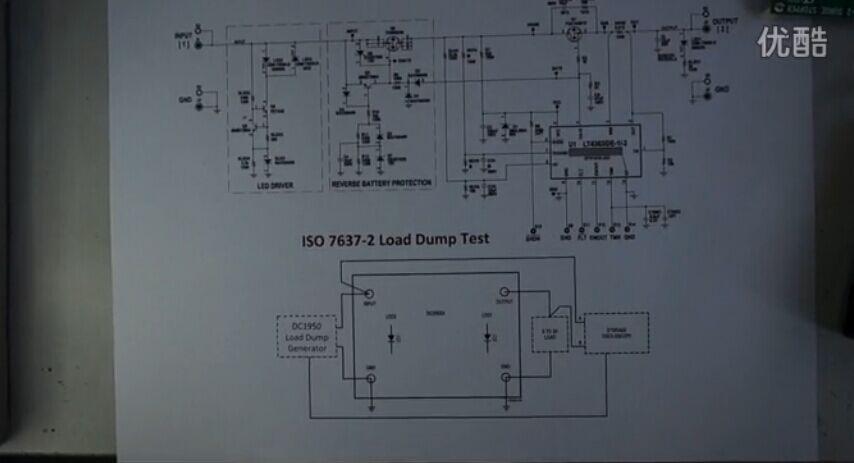

3、开盖测试SiC MOSFET驱动电压

因为SiC MOSFET的驱动电压尖峰的主因之一是驱动回路里的MOSFET 源极电感,所以针对TO247-3封装器件,如果要得到更真实的管芯驱动波形,可去掉器件的塑封材料,直接从芯片上测试驱动电压,可对比呈现引脚上和管芯上的驱动波形差异。

图9:开盖测试点及测试板

其中VG_LS是测源极引脚与栅极引脚之间的电压;VG_LS_K是测管芯源极与栅极之间的电压,测试点如下:

图10:开盖测试点

测试中,下管Q2保持关断,上管Q1进行开关动作,过程如下图11:

图11:测试过程

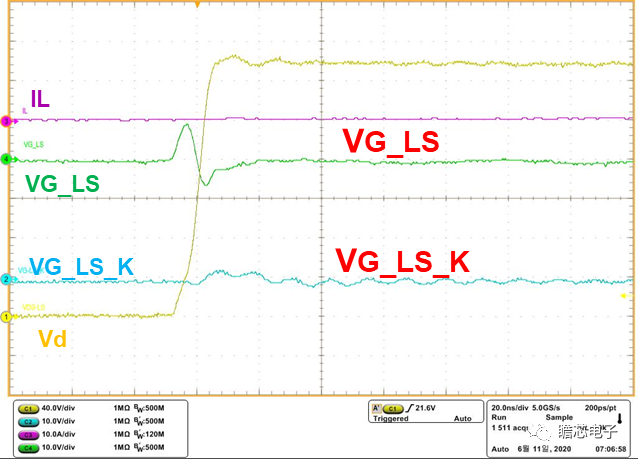

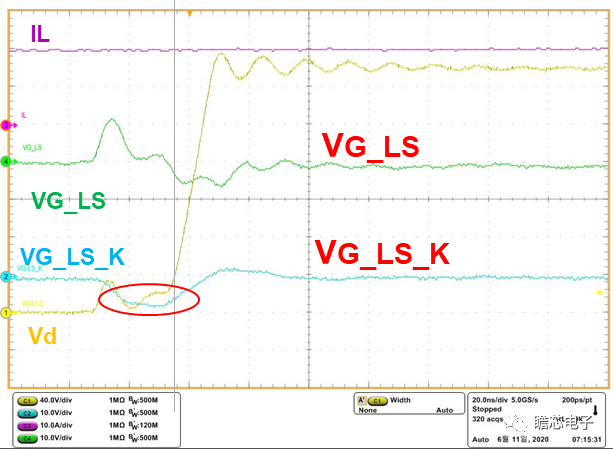

在上管Q1初次开通时(1st Rising),如下波形图12所示:虽然从引脚测试VG_LS有较大正尖峰及震荡,但蓝色的管芯VG_LS_K显示驱动电压波动很小,几乎没有明显尖峰,比较安全。

图12:测试下管Q2芯片时,上管Q1开通

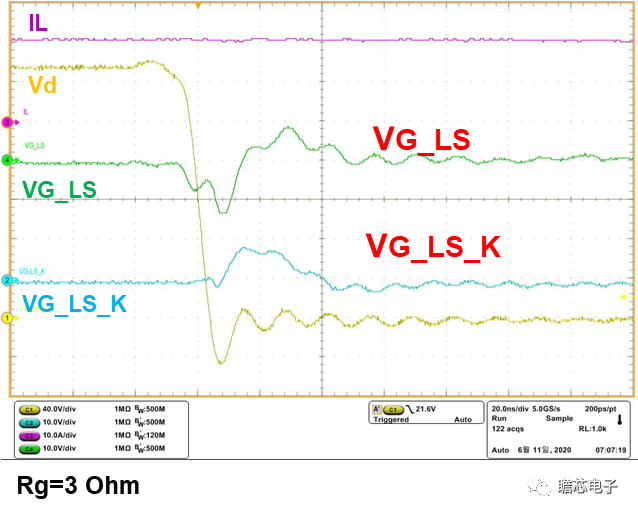

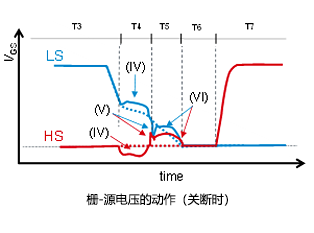

在上管Q1初次关断时(1st Falling),如下波形图13所示:虽然从引脚测得绿色的VG_LS则有较大的负尖峰及震荡;管芯上VG_LS_K几乎没有负压尖峰,但有正尖峰,与VG_LS的差异较大。

图13:上管Q1关闭时,给下管Q2芯片的驱动串扰波形

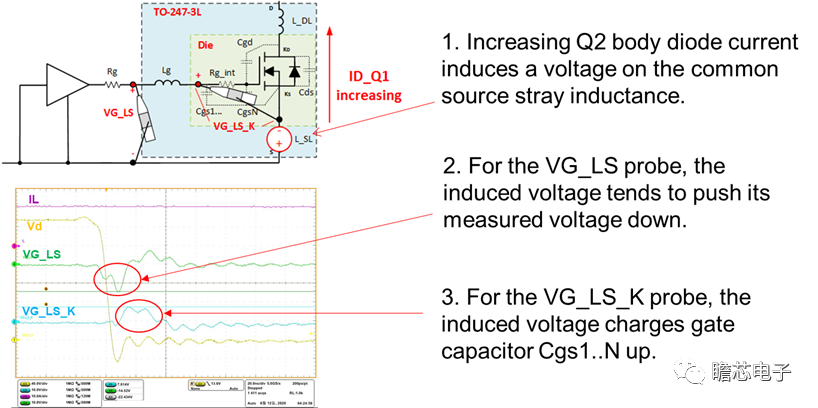

上管关断后,电感电流通过下管的体二极管续流,在下管的源极电感上产生“下正上负”的自感电动势,由于VG_LS测量的是引脚上的电压,因此VG_LS会下降,产生负尖峰。而VG_LS_K测的是管芯上的电压,自感电动势会对Cgs充电,让VG_LS_K抬升。因此会看到引脚与管芯上的电压呈现相反的尖峰波形。

图13:上管Q1关闭,给下管Q2芯片的驱动串扰尖峰分析

在上管Q1第二次开通时(2nd Rising),如下波形图14所示:管芯VG_LS_K没有正尖峰,但有平缓的负尖峰,这是由于下管的反向恢复电流,抬升了源极电动势,从而让Vgs-k出现负尖峰。

图14:上管Q1开通时,给下管Q2芯片的驱动串扰尖峰

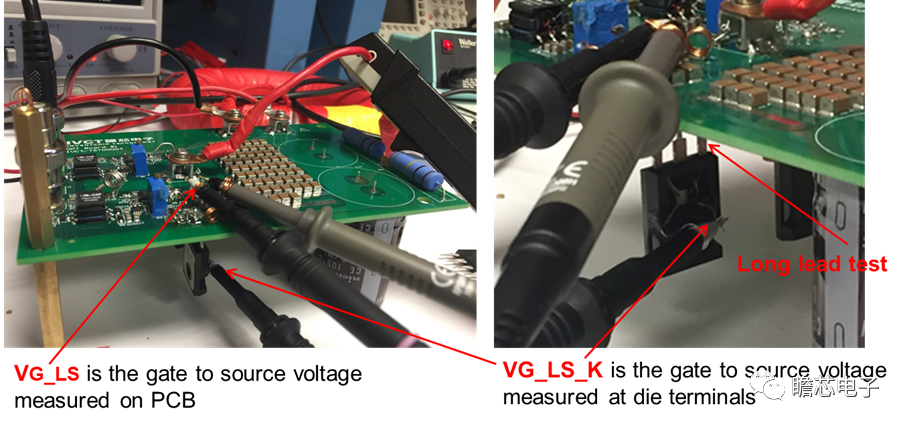

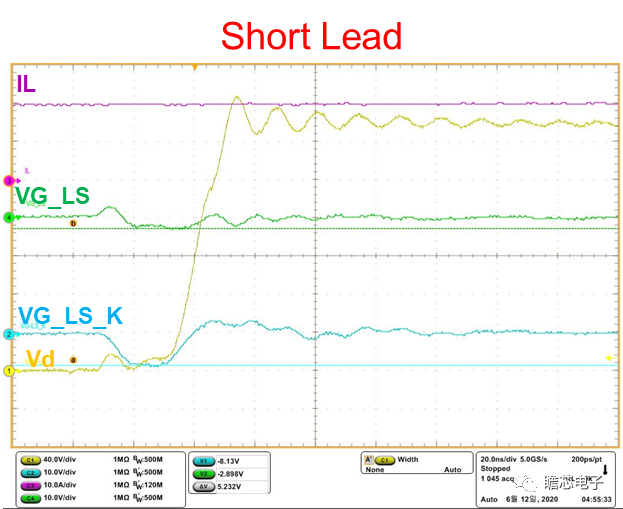

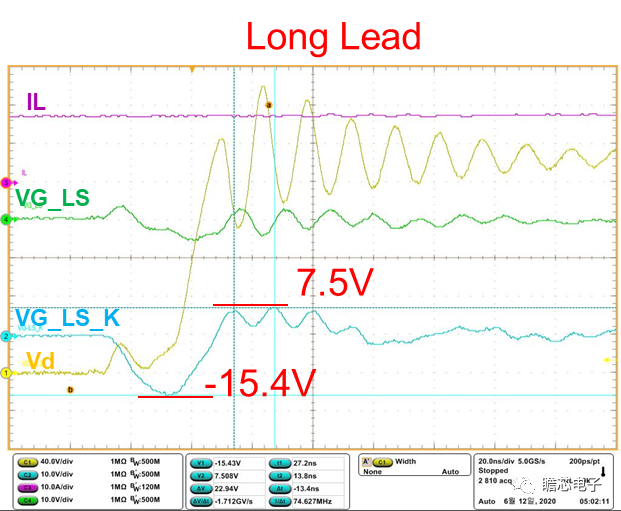

为了对比呈现不同长度的管脚寄生电感的影响,在第二次开通上管Q1时,分别从长/短源极管脚去测试驱动电压Vgs,2组波形如下图15/16:

图15:短引脚测试波形

图16:长引脚测试波形

如上图16,当用较长的源极引脚测试时,管芯真实驱动电压有更大的过冲和震荡,而且超过SiC MOSFET阈值电压(Vth),导致下管Q2误开通和较大Vds震荡。

总结

驱动串扰尖峰的主要原因有2点:

高dv/dt时的米勒电效应;

高di/dt在源极引脚寄生电感上产生的震荡。

2. SiC MOSFET管芯的真实驱动电压,与TO247-3引脚测到的驱动电压可能呈现相反的尖峰波形。

3. 若管脚测到超规格的驱动波形,可进一步确认管芯的真实驱动电压;

4. 若从长引脚测得较大Vds震荡,可能器件有误开通,甚至损坏器件。

5. 建议驱动路径尽量靠近器件引脚根部,规避长引脚的寄生电感。

审核编辑:刘清

-

MOSFET

+关注

关注

147文章

7521浏览量

215220 -

emc

+关注

关注

170文章

3986浏览量

184353 -

电磁干扰

+关注

关注

36文章

2348浏览量

105810 -

SiC

+关注

关注

30文章

2975浏览量

63334 -

驱动电压

+关注

关注

0文章

80浏览量

13491

原文标题:SiC MOSFET驱动电压尖峰分析与抑制(上)

文章出处:【微信号:瞻芯电子,微信公众号:瞻芯电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

应用笔记 | SiC模块并联驱动振荡的抑制方法

为何使用 SiC MOSFET

全SiC模块栅极误导通的处理方法

SiC-MOSFET与Si-MOSFET的区别

【罗姆SiC-MOSFET 试用体验连载】基于SIC-MOSFET评估板的开环控制同步BUCK转换器

SiC MOSFET:栅极-源极电压的浪涌抑制方法-负电压浪涌对策

SiC MOSFET驱动电压尖峰与抑制方法分析(上)

SiC MOSFET驱动电压尖峰与抑制方法分析(上)

评论