作者:洪志斌博士‒日月光研发中心副总经理

在半导体前段制程微缩日趋减缓后,异质整合先进封装技术已然成为另一个实现功能整合与元件尺寸微缩的重要技术发展潮流。伴随着人工智能物联网 (AI-centric IoT)、5G通信、高性能计算(HPC)和智能汽车等主要半导体应用不断发展,新兴应用场域 (如生成式AI) 对于芯片封装互联线的高密度、高速和低延迟需求与日俱增,推动异质整合先进封装技术的需求不断增长与突破。通过先进封装技术实现异质整合,可在单一封装内实现不同设计和制程节点的小芯片 (Chiplets) 整合,让企业能依照需求选择不同单价的制程,例如运算芯片采用3纳米、射频芯片用7纳米,又或者快速产出特定功能的超级芯片,兼顾成本效益。除了追求更高的互联密度外,异质整合还有一个重点,亦即把实现整个系统所需的各种元件 (如逻辑芯片、传感器、记忆体等) 都整合在单一封装,使得能耗、效能获得改善和大幅缩小体积。

推动AI高性能计算的先进封装解决方案

目前用于AI云端计算处理器的高密度先进封装,其尺寸至少都是55mm x 55mm以上,其封装基板上的布线层一般至少是5-2-5 (上面5层、中间2层、下面5层),甚至可多达11-2-11。其封装型态一般是使用扇出型技术加上silicon bridge,也可以是2.5D封装,以硅中介层 (Si Interposer) 作为小芯片的整合平台。业界的目标都是在同样的空间中,获得更多算力。

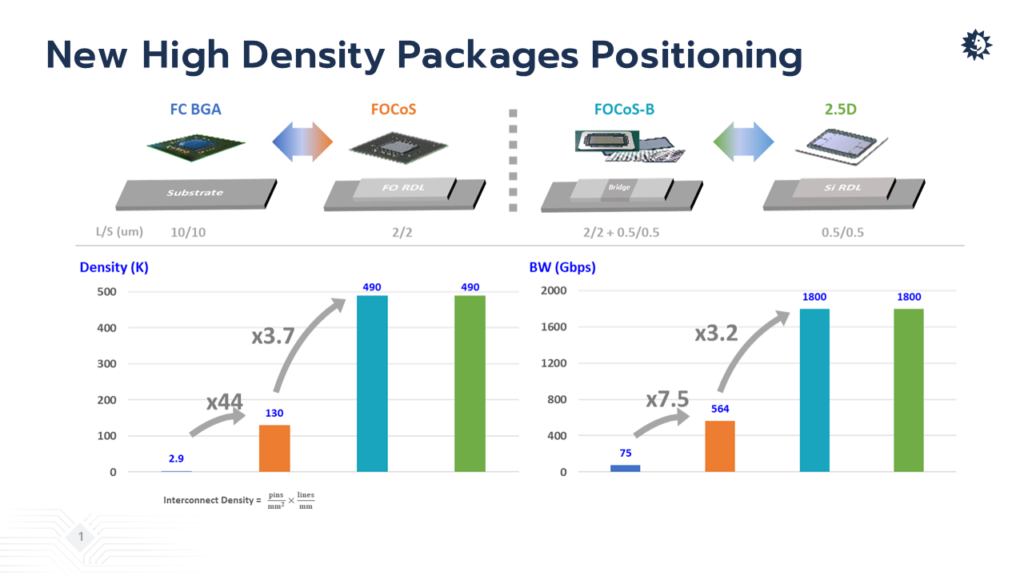

日月光提供的高密度封装的解决方案:包含覆晶球格数组封装 (FCBGA)、Fan Out Chip-on-Substrate (FOCoS)、FOCoS-Bridge以及2.5D封装等三大类。FCBGA芯片间封装互联线的整合是透过BGA基板达成,其最小L/S (线宽/线距) 一般仅能达到10μm/10μm。目前很热门、供不应求的CoWoS (Chip on Wafer onSubstrate) 是一种2.5D封装技术,以硅中介层(Si Interposer) 上的重布线层 (RDL) 连接整合小芯片,可以将L/S大幅微缩到0.5μm/0.5μm。由于硅中介层需要承载所有的芯片 (以相肩比邻的方式排列),因此面积越来越大,使得每片12吋晶圆能切割出的硅中介层芯片越来越少 (一般少于五十颗),导致2.5D封装的制造成本也随之大幅上升。但是并非所有应用皆需要0.5μm/0.5μm的L/S,因此日月光发展FOCoS (Fan Out Chip-on-Substrate),利用扇出型技术的RDL来整合不同小芯片,其L/S可以达到2μm/2μm,其优势是以相对较低的制造成本,提供市场不同的解决方案。此外ASE的FOCoS-Bridge技术利用高密度连接线硅桥 (silicon bridge),L/S可以达到0.5μm/0.5μm,在需要高速传输的区域连接不同芯片 (例如逻辑芯片和记忆体),而在其它区域以Fan-Out RDL整合,因此在L/S设计上可以兼具0.5μm/0.5μm + 2μm/2μm的弹性,同时达成封装密度以及带宽的大幅提升。

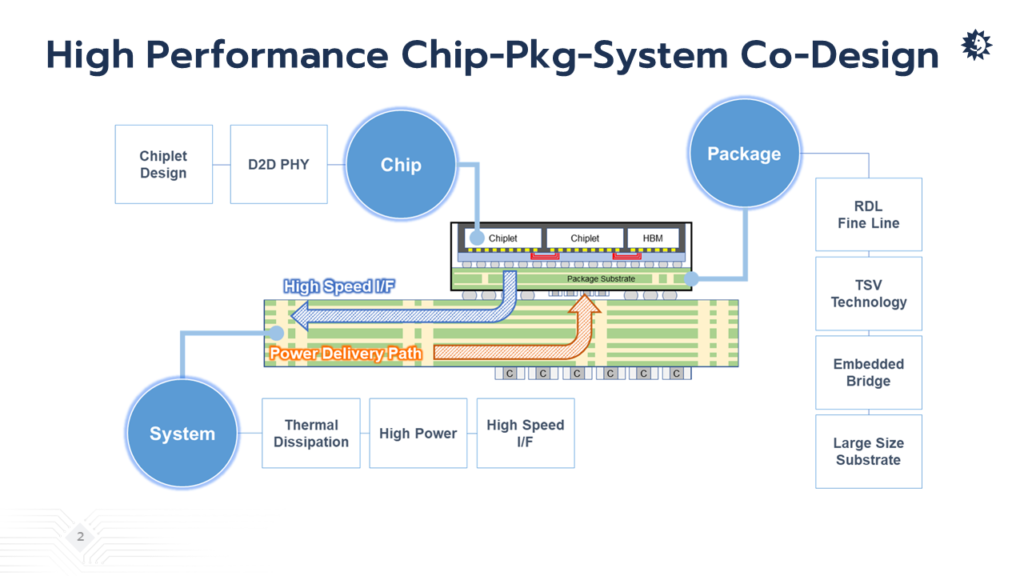

高性能芯片/封装/系统共同设计(Co-Design)

要达成前述的带宽大幅提升,需要由芯片、封装一直到整个系统都要一起考虑,以实现整个系统而不仅是个别元件的Holistic Design最优化。利用电子设计自动化 (EDA) 作设计最优化的时候,需要考虑讯号在整个传输路径上会有多少改变,例如需考虑Cu pillar, RDL fine line, TSV, μbump等,最后利用眼图(eye diagram) 分析 SerDes electrical performance。针对高速讯号差动对线 (differential pairs) 设计的时候,需要降低反射损耗 (returnloss) 及插入损耗 (insertion loss),尤其是在工作的频段。日月光的优势在于我们能够做到由芯片、封装到整个系统,从头到尾的完整设计。

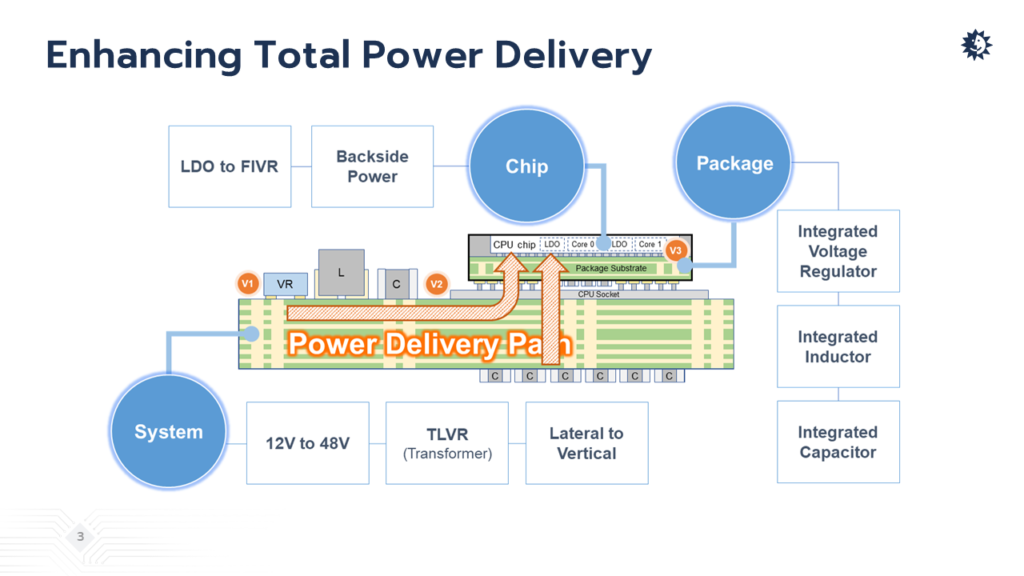

如何节省Power达到更大的每瓦算力

目前业界都在思考一件事情,本来放在系统上的Power组件,能不能放在离Package或Processor芯片越近越好;甚至重新思考设计供电架构,例如直接由芯片背面供电 (Chip Backside Power Delivery)。

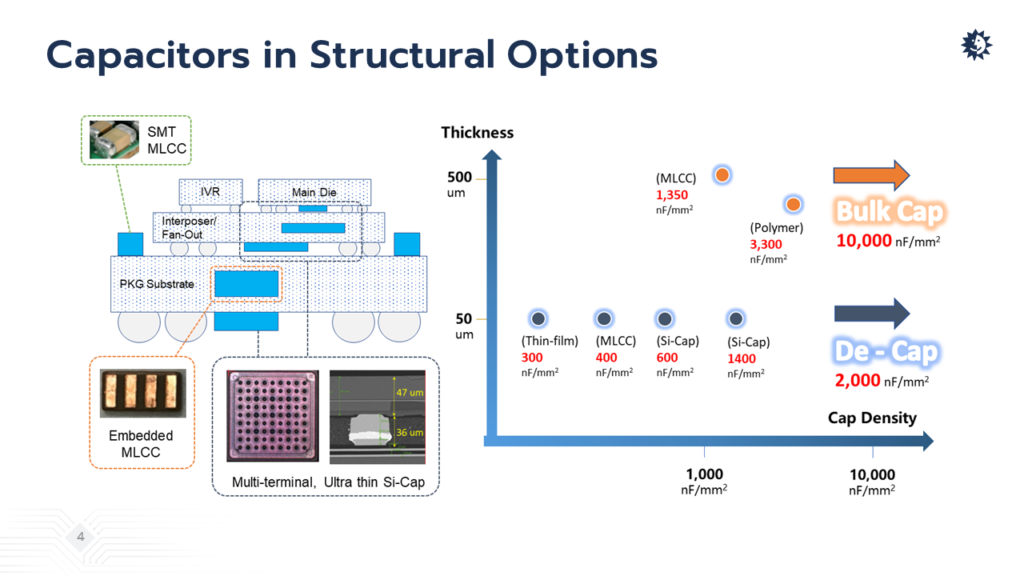

供电网络(PDN)电源完整性设计

电容放对位置可以有效增进电源完整性 (Power integrity),降低电源噪声 (Power Noise),虽然理论上电容离芯片越近越好,但是需要考虑电容的尺寸以及制程,让整体最便宜,效果最好。常见的SMT电容都是蛮大一颗,但现在已经有芯片层级的硅电容 (Si-Cap),也都可以提供不错的电容值。

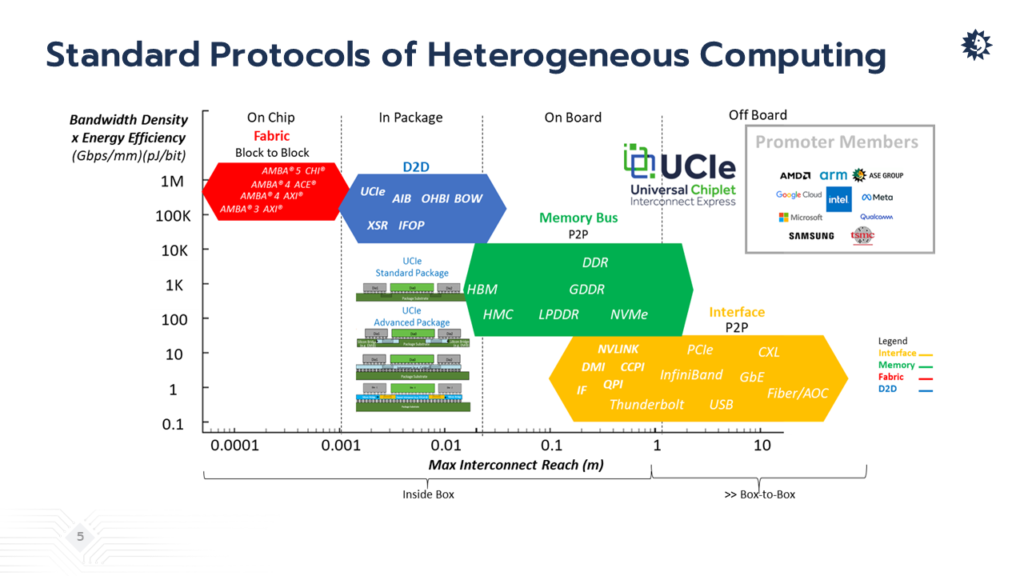

UCIe (Universal Chiplet Interconnect Express) 产业联盟

传统进行系统设计的时候,在芯片端、系统板 (System Board)上,可以看到许多标准通信协议 (例如Memory Bus、Interconnection interface Protocol),封装虽也有一些协议,但是大家没意识到这么重要。直到最近2.5D、FOCoS封装技术在针对小芯片设计所面临的挑战中,业界发现需要有一个共通的Universal Interface;2022年3月Intel邀请半导体产业链上下游厂商共组UCIe产业联盟,将小芯片数据传输架构标准化,以降低先进封装设计成本。日月光很荣幸成为创始会员 (Promoter member),我们拥有最多的先进封装型态,把这些封装设计规范融合进来后,可以连结晶圆代工厂的解决方案,以及系统原始设备制造商 (OEM) 及云端服务提供商的系统需求;需求整合后,新的UCIe PackageStandard就可以布建出来,协助各种不同先进封装技术架构 (如2.5D、3D、FOCoS、Fan-out、EMIB、CoWoS等),在未来高阶运算半导体封装,实现无处不在的小芯片异质整合互连。这也表示台湾开始可以在标准的制定方面扮演角色,为业界提供整合的解决方案。

异质整合的概念已经发展多年,不只可以用在异质小芯片间的整合,也可以把其他非芯片的主/被动元件,甚至连接器都整合在单一封装体内。要做到这点,不只需要封装技术,更需要设计跟测试的配合。日月光可以提供从设计、封装到测试的一条龙服务方案,协助客户减少芯片设计时程并加快产品开发速度。

审核编辑:汤梓红

-

芯片

+关注

关注

463文章

54484浏览量

469833 -

半导体

+关注

关注

339文章

31298浏览量

266886 -

封装设计

+关注

关注

2文章

49浏览量

12190 -

先进封装

+关注

关注

2文章

565浏览量

1065

原文标题:异质整合先进封装设计趋势

文章出处:【微信号:ASE_GROUP,微信公众号:ASE日月光】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

推动AI高性能计算的先进封装解决方案

推动AI高性能计算的先进封装解决方案

评论