▼关注公众号:工程师看海▼

失效分析一直伴随着整个芯片产业链,复杂的产业链中任意一环出现问题都会带来芯片的失效问题。芯片从工艺到应用都会面临各种失效风险,笔者平时也会参与到失效分析中,这一期就对失效分析进行系统的讲解,笔者能力有限,且失效分析复杂繁琐,只能尽力的总结一些知识体系,肯定会有很多不足与缺漏。

一.失效的定义:

造成失效的原因不一而足,失效的表现也纷扰复杂,在进行失效分析之前需要确定什么是失效?

1.性能异常:

这种情况比较常见,芯片的功能正常,但是某些性能未达标。面对这种情况更多的是从设计端入手,结合测试数据与设计指标去定位原因,无论是版图还是电路设计问题,亦或是其他原因,失效分析时都要需要很精细的去排查问题。

2.功能异常:

芯片某些功能失常,甚至芯片无法启动。而发生这种情况的原因大致有三种:

2.1 电路设计:

芯片完全满足电路设计要求,但是问题出在电路设计上,电路有缺陷从而导致功能异常。这种情况下很多失效分析手段都无能为力,因为问题出在设计端,所有的芯片都面临同一问题,无法提供参照指标,没有基线也就无法判定“好”与“坏”。只能通过FIB对各个模块进行切割/连接,利用Nano-Probe对各个模块进行电学性能测量,从而慢慢推断出问题,过程会伴随着巨大的工作量。

2.2 芯片可靠性设计:

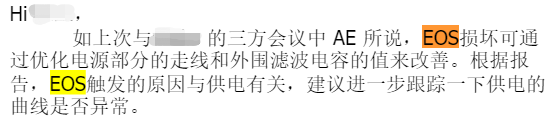

芯片本身的电路设计没有问题,但是芯片在物理可靠性设计上有所欠缺,从而造成芯片存在可靠性缺陷。芯片在面对EOS、ESD、EMI、应力、温度等外界刺激时发生了损伤,从而造成了功能失常。可靠性的强弱也直接决定了芯片量产后的良率。

2.3 工艺:

这种情况在先进工艺上比较明显,Fab的工艺出现问题从而导致芯片失效。现在很多先进制程下的芯片最后的良率只能达到50%~60%很大因素是因为工艺上的问题(笔者的分析主要是针对已经固化的成熟工艺)。

电路功能失效的显著特征就是普遍性,同一批都会出现相同的问题,无一幸免。而大多数因物理可靠性造成的失效都具备一定随机性,要么失效程度不一,要么需要一定的触发条件。因为物理可靠性的缺陷而造成某一性能发生异常的可能性也有,所以失效分析还是要基于实际情况,具体问题具体分析。(笔者也见过很严重的物理可靠性缺陷而导致同批芯片全部失效)

二.失效层次:

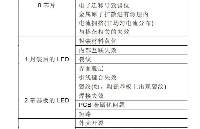

半导体器件的失效可以根据失效发生的阶段划分为三个层次:

芯片(裸片)层次:芯片层次的失效是目前出现概率最高的阶段,因为现在芯片工艺与设计的复杂性,工艺偏差,设计不到位等多方面因素,都会造成芯片在制造、运输等过程中发生失效。

封装层次:封装过程中键合失效,打线过重,粘连失效,空洞过多等因素都会造成封装层次上的失效,随着现在封装技术愈发先进,封装过程中出现失效的风险也在上升。

应用层次:下游客户在芯片应用端造成的失效。诸如PCB板设计不合理、超出极限的应用场景等,这种情况就不表了。

三.失效分析流程:

记录失效表现,将芯片失效的“症状”记录下来,诸如短路、开路、漏电、性能异常、功能异常、时好时坏等。很多失效原因其表现出的“症状”是相似的,例如漏电,物理损坏能造成漏电,隔离不到位也能造成漏电,Latch-up问题也会造成漏电。

定位失效层次,在交付后的应用端发生失效,还是封装后失效,亦或是裸片自身就有问题。三种不同层次对应不同的失效分析思路。

失效触发条件,正常功能测试中出现失效;高低温测试出现失效;ATE出现失效;ESD失效,封装造成失效。(如果测试工程师能严格遵守静电防护要求进行测试和设计测试板,芯片在测试过程中面临ESD/EOS的风险很低)

统计失效概率,是随机性的出现单颗失效还是按一定比例出现多个失效,亦或是全部芯片都出现失效。

复现失效条件,要对失效问题进行复现或追查,确认芯片失效原因,从而帮助推测失效原因。

确定失效类型,对失效类型做出推断,从而确定失效分析的方向。如果无法通过失效结果推断出失效类型,那么只能根据后续的测试结果进行推断。

规划实验计划,对失效原因有大致推断后就需要进行实验去寻找数据支撑,如果推断比较清晰的话实验就比较好去定位。

总结改善措施,得出失效原因的结论后就需要制定相对应的改善措施,并记录在册。每一次的失效结论都是拿钱砸出来的经验教训,也是产品公司必须要经历的过程。

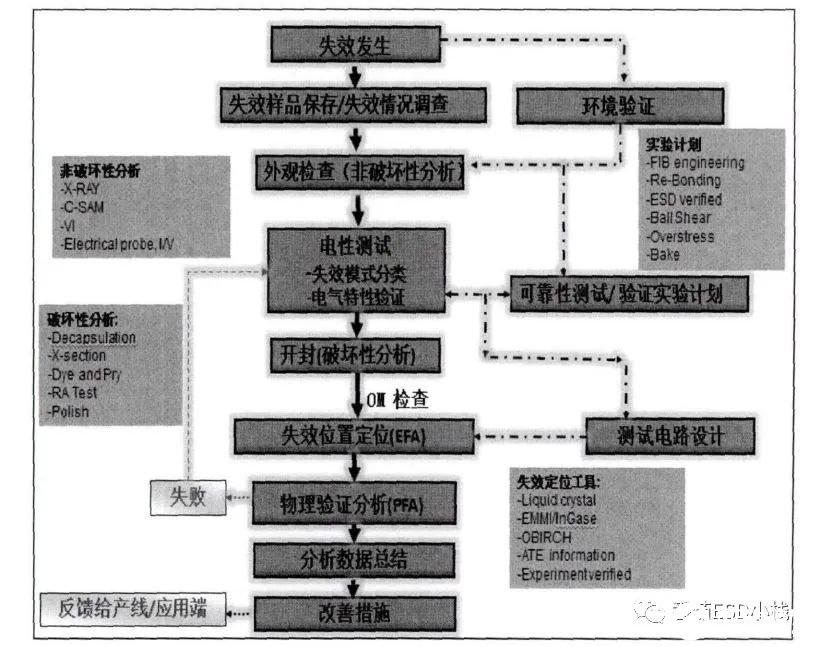

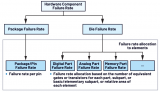

图一.失效分析流程示意图。

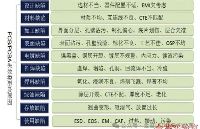

四.失效分析手段

目前国内已经有很多专业的团队在做失效分析和测试,他们不仅具备专业的仪器设备,还会有专业人员对失效分析进行技术支持。但是笔者认为IC设计公司还是得具备一定的失效分析能力,因为整个芯片各个模块的设计与电路指标都是设计公司确立的,版图/后端也是设计公司做的,设计公司对整个芯片更加清楚。第三方公司能辅助定位失效点和提供技术支持,但是其对芯片的熟悉程度远不如设计公司,设计公司应该主导失效分析。这里对几种常见的失效分析手段进行简介:

4.1.非破坏性分析:

4.1.1. OM(Optica Microscope):

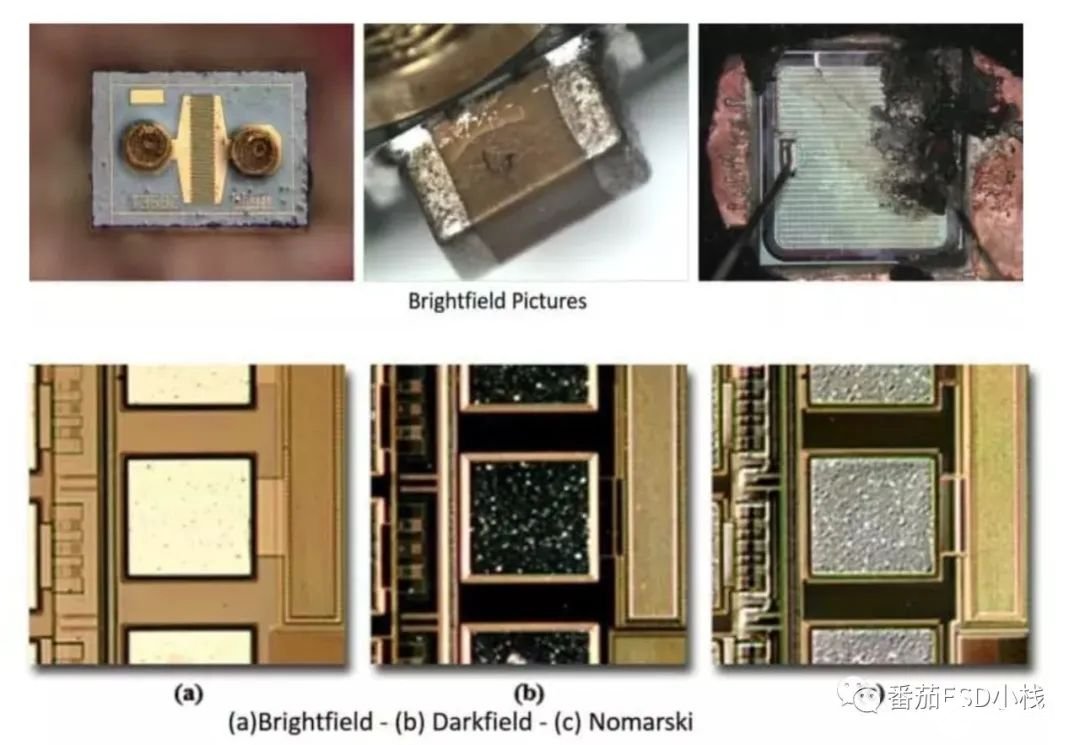

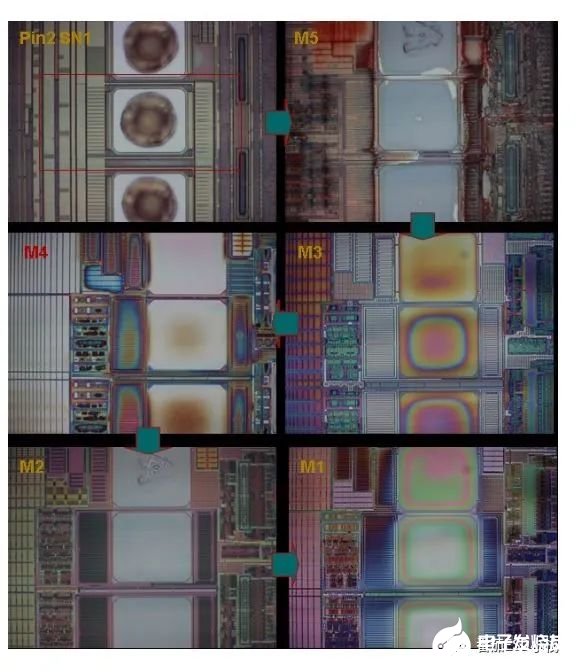

利用高倍数显微镜对芯片或者封装表面进行视觉检测。如图二所示为OM结果,其中暗场技术能观察到表面划痕与污染,Nomarski技术能观察到裂缝与刻蚀坑。

图二.OM观测结果。

4.1.2. SAT/SAM (Scanning AcousticTomography/Scanning Acoustic Microscopy) :

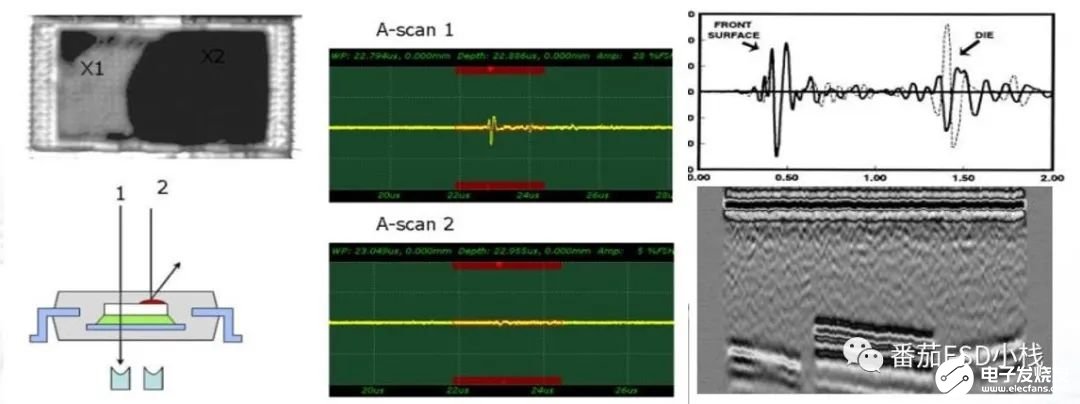

SAT/SAM利用超声波在不同介质中的反射系数,得出封装内部的结构图。该技术能用于检查样品中的空隙、裂纹和分层。而SAM的精度与分辨率是强于SAT的。

图三.SAT/SAM观测结果。

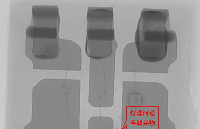

4.1.3.X-Ray/ Computed Tomography (CT) X-Ray:

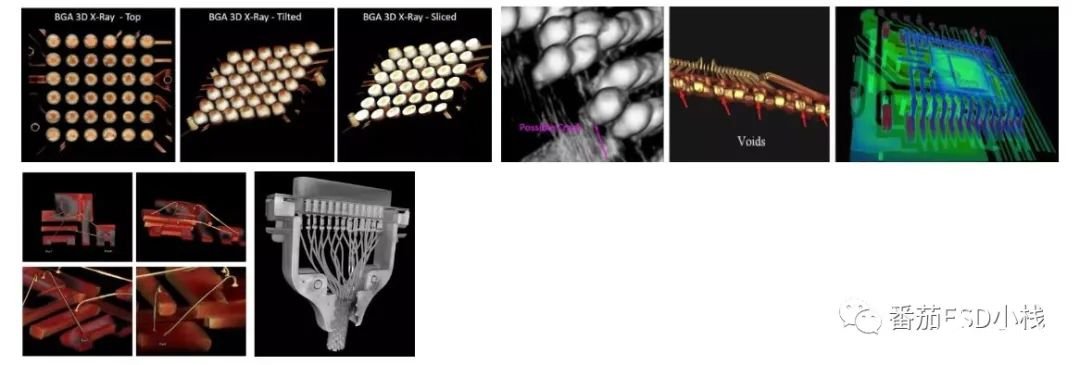

利用X光和CT对芯片进行拍照从而得出内部结构图。如果需要得到更详细的内部结构,可以将样品进行360°拍照,然后利用图像处理技术构建出芯片的3D结构图。

图四.3D X-Ray 结果。

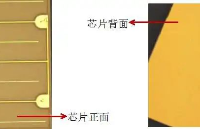

4.1.4. Decapsulation:

大部分封装所造成失效都能通过上述手段检测出来,但是如果需要对芯片进行检测就得去封装(开盖)。目前Decapsulation的手段有两种:1. 化学法:利用硫酸和硝酸去腐蚀开盖。2. 激光法:利用激光将封装熔解。

图五.Decapsulation结果示意图。

4.2. EFA (Electrical Failture Analysis ):

4.2.1. Electrical Testing:

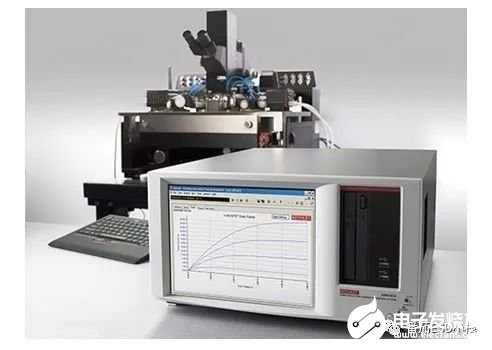

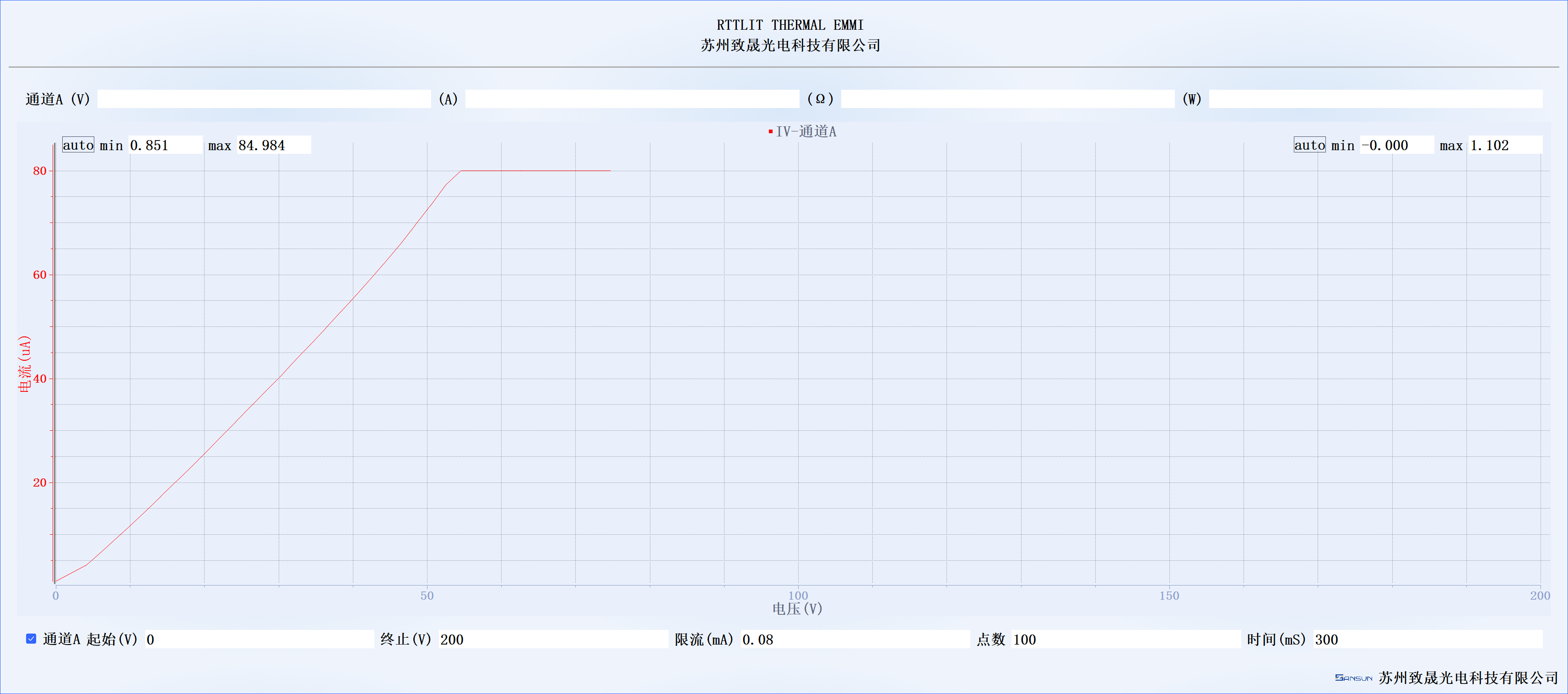

利用探针台+半导体分析仪+电学测试设备,利用探针对芯片内部进行采样和施加激励,直接对电路模块进行电学特性分析。这是最普遍的电学失效分析手段,不过探针的扎针落点有很多限制,有时得配合FIB和金属去层才能对指定的模块进行电学性能测量。

图六.电学特性分析。

4.2.2. Photo Emission Microscope (EMMI InGaAs OBIRCH)

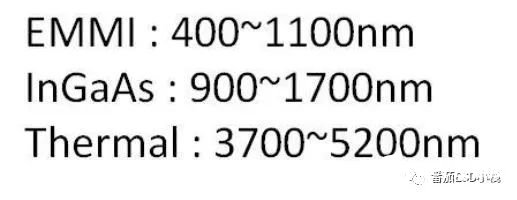

其中关于EMMI之前已经介绍过,传统EMMI的探头为CCD,而InGaAs是EMMI的一种探头,两者的接收波段有区别,且InGaAs更加快速与灵敏。

图七.EMMI、InGaAs、Thermal波段范围。

OBIRCH是利用红外激光照射局部位置引起热梯度造成局部电阻变化,从而观察到电流变化。阻抗异常其电流变化会与其它地方不同,从而定位失效点。EMMI InGaAs OBIRCH是三种应用非常广泛的FA手段,其结果不如SEM, X-Ray等技术直观,且依赖偏置条件,但是能快速定位失效点,其应用场景远比SEM等广泛,是主流的失效分析手段之一。日后笔者会总结EMMI的分析心得,进行EMMI前最好先对失效点及失效原因有个推断,然后给予适当的偏置条件。

4.3.PFA (Physical Failure Analysis)

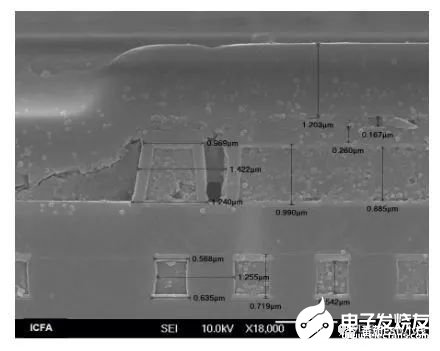

物理失效分析就需要对芯片进行一些物理处理,其中最主要的处理方式一个是纵刨,一个是金属去层。纵刨的样品制备包括清洗、安装然后将样品放入聚酯或环氧树脂中。

图八.纵刨SEM图像。

去层工艺使用化学溶液/气体蚀刻和机械抛光来缓慢、精确地去除芯片上的每一层金属。

图九.金属去层示意图。

4.3.1.FIB (Focus Ion Beam):

FIB是IC设计公司最常用的失效分析手段之一,这里就不赘述了。

浅谈失效分析—FIB聚焦离子束加工技术简介

4.3.2.SEM(Scanning Electron Microscope ):

SEM也是常用手段之一,因为其放大倍数很大,所以利用其他手段确认失效点后便可利用SEM进行直观观察,从而确认失效原因。SEM可以对表面进行观察,也可配合纵刨技术对截面进行观察。

4.3.3 SCM(Scannin Capacitance Microscope):

扫描电容显微镜,这种显微镜主要是利用探针对半导体器件施加信号,然后测量C-V曲线,从而确定半导体器件的掺杂类型。

而类似AFM、TEM、EDX、XPS、XRD等微观物相测量手段,一般是Fab进行更深层次的失效分析时才会用到,Design House一般不需要介入如此深的物相表征。

因为失效分析比较特例化,很难总结出一套通用的细则,且能产生芯片失效的可能性不胜枚举。笔者认为失效分析更需要经验的积累,只有见多识广后才能总结出失效的规律与普遍特征,笔者还有很长的路要走,也希望大家多多交流,毕竟一个人的见识总归是有限的。

原作者:番茄ESD小栈

如果看到这里,请点赞、收藏、分享三连!

限时免费扫码进群,交流更多行业技术

审核编辑 黄宇

-

芯片

+关注

关注

463文章

54410浏览量

469153 -

电路设计

+关注

关注

6745文章

2793浏览量

220206 -

失效分析

+关注

关注

18文章

254浏览量

67901

发布评论请先 登录

芯片失效分析实战指南:精准定位失效根源,护航国产芯片良率提升

PCBA失效分析怎么做?第三方机构详解7步标准流程

芯片越先进,越离不开失效分析:半导体失效分析是做什么的?

对于伺服行星减速机的轴承失效的原因分析

IC引脚失效模式和影响分析(FMEA)的重要性

LED失效分析方法与应用实践

热发射显微镜下芯片失效分析案例:IGBT 模组在 55V 就暴露的问题!

芯片失效步骤及其失效难题分析!

LED芯片失效和封装失效的原因分析

破局SiC封装瓶颈 | 攻克模组失效分析全流程问题

浅谈失效分析—失效分析流程

浅谈失效分析—失效分析流程

评论