鋪銅Plane

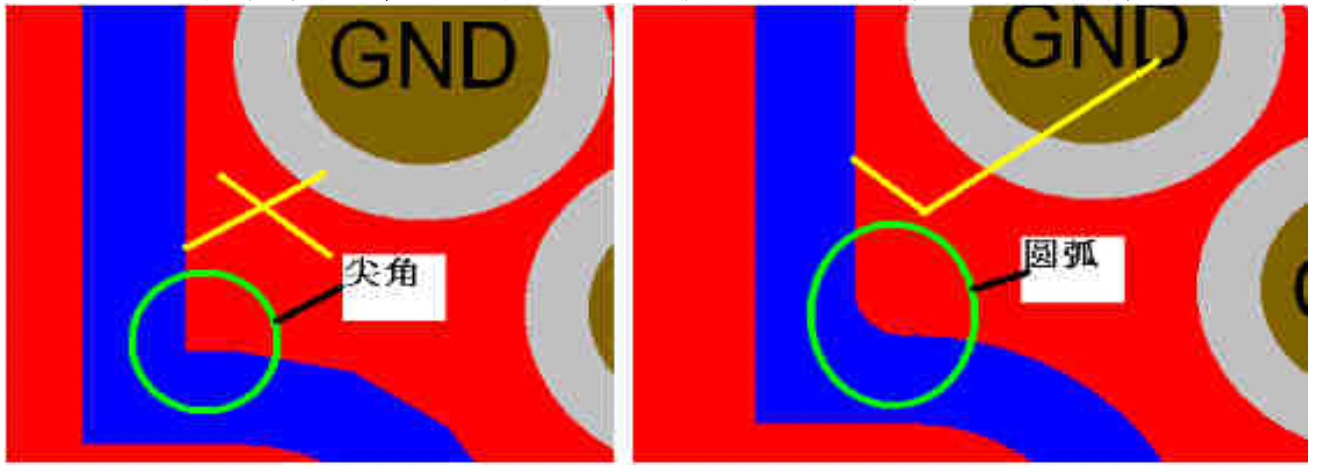

1.1 不要铺成尖角出现,会变成电磁波的能量辐射出去,请将铺成弧!

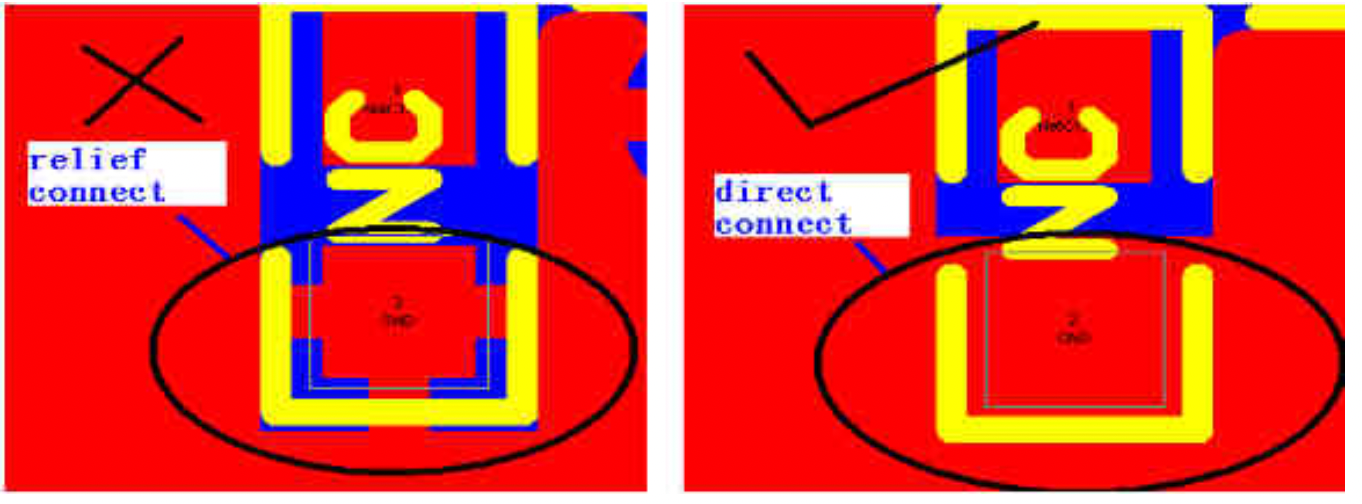

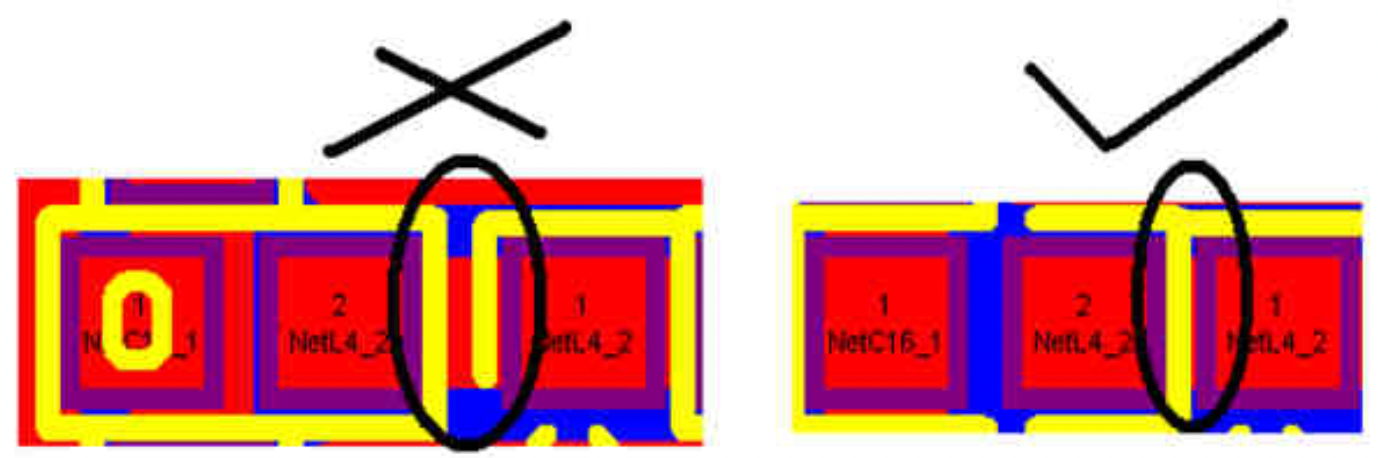

1.2 铺铜连接方式,请设定为direct connect ,不要设定relief connect;目的为增加下地PAD的接地面积

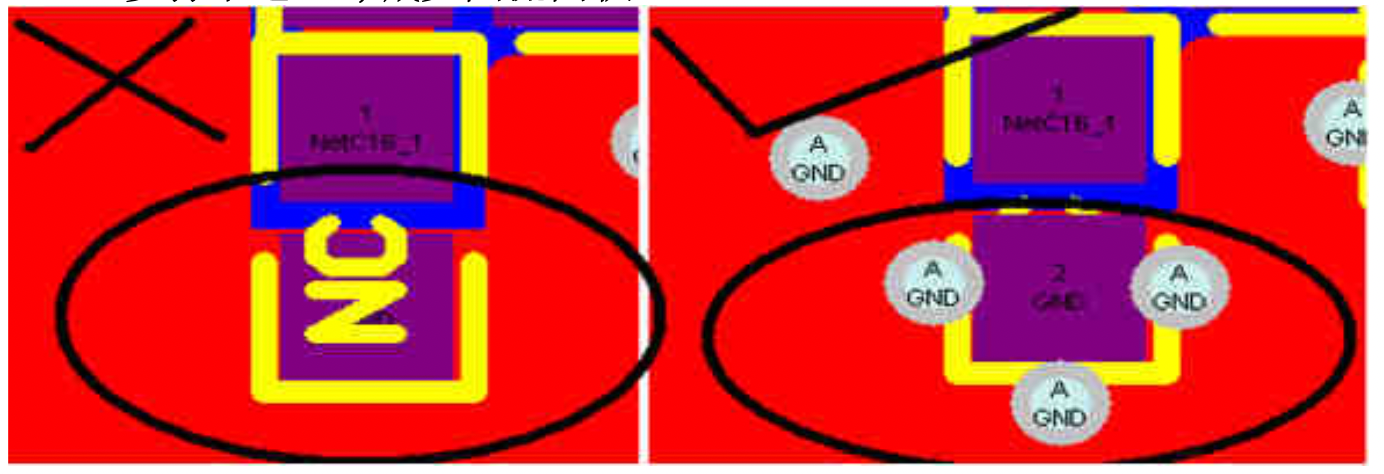

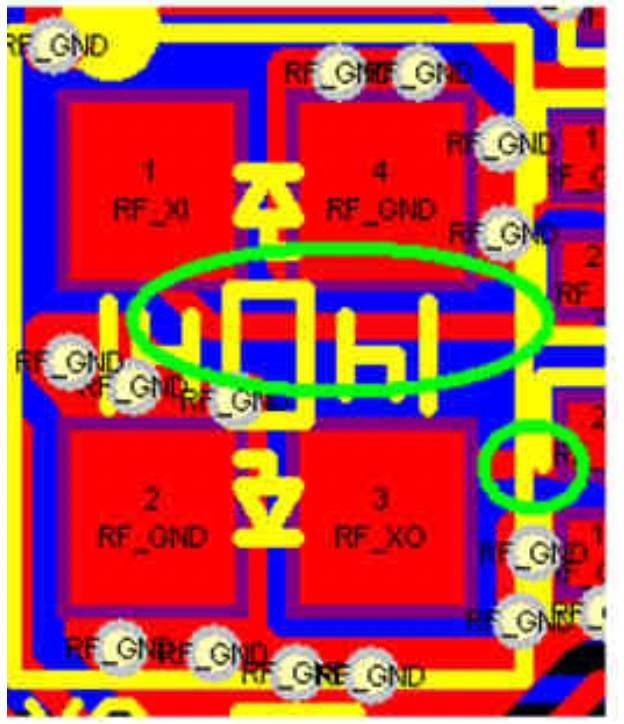

2.元器件接地的脚周围的尽量多打下地via

2.1多打via,减少寄生电感的影响,增加接地性

2.2Via要打得巧,紧靠下地pad(切记打在pad上面,防止元件吃锡不足)

2.3多打下地via,减少回流面积。

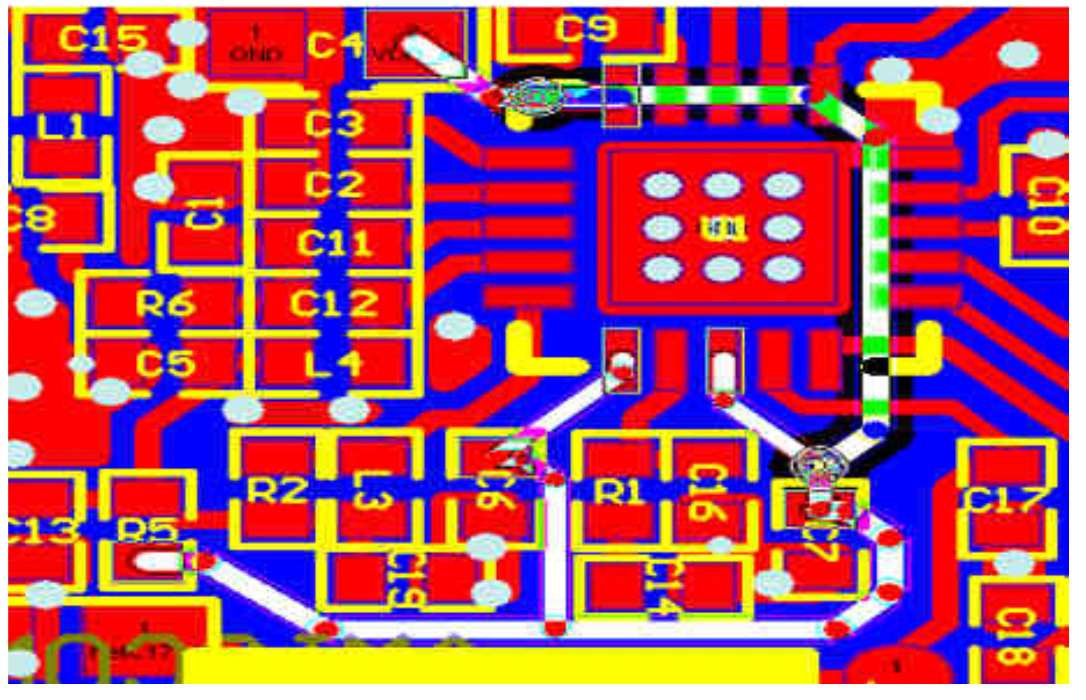

3.RF输入输出(pin3 & pin4)电路中下方不能有电源走线

3.1:高频线与 电源会相互干扰,会影响power 及感度 输出

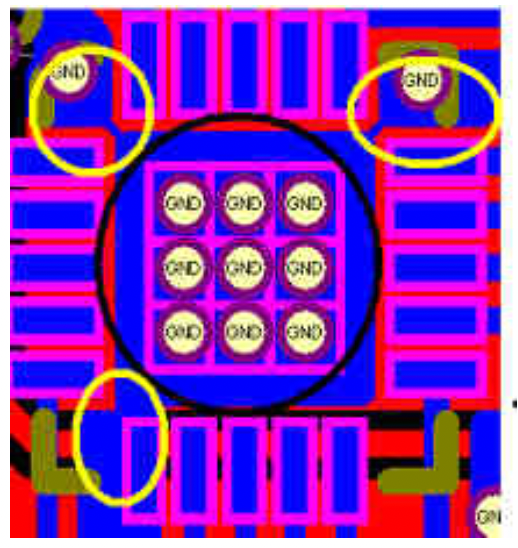

4.IC PCB 封装底部请打九个via下地

4.1QFN封装,底部为地,必须通过一些via将芯片地与PCB地很好的结合起来

4.2IC背面接地区域四角尽量延伸与toplayer大地相连,增加IC底部接地面积

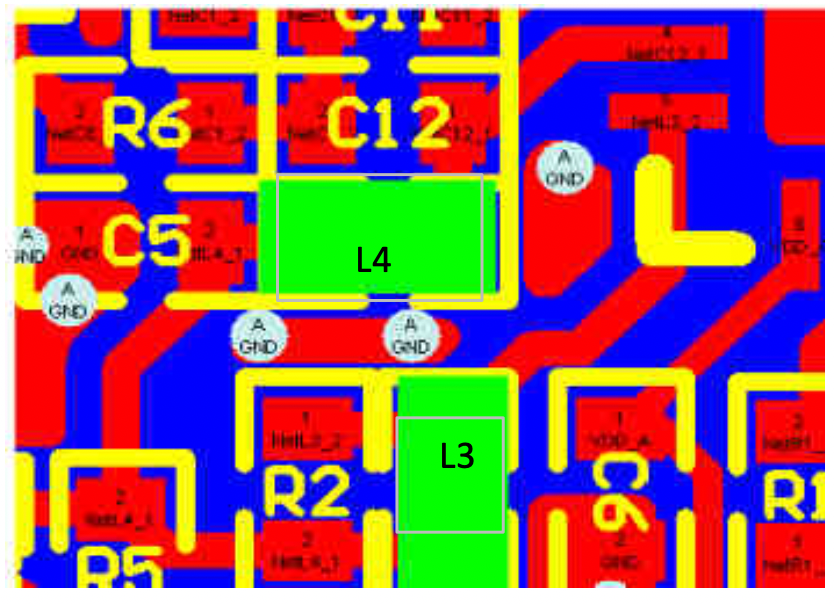

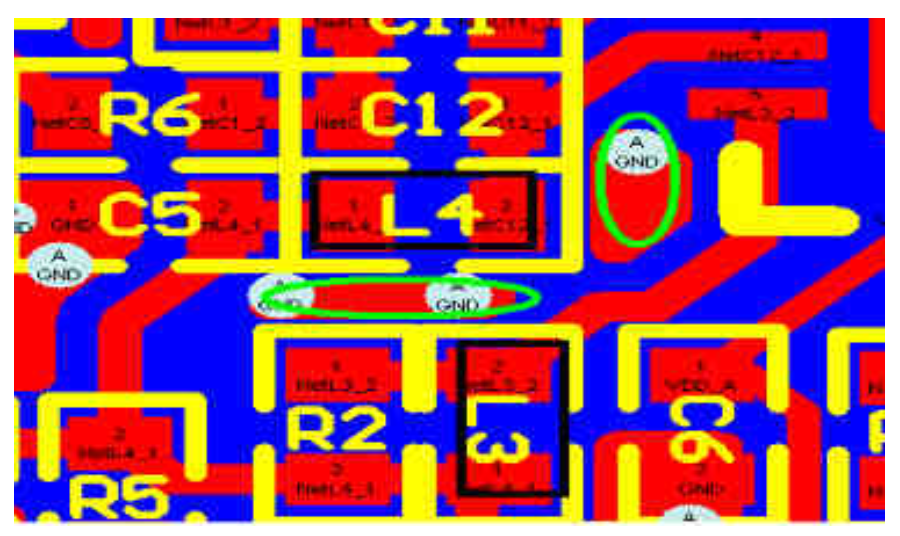

5.在射频前端电路,相邻电感要相互垂直放置,以避免互感,减少耦合

5.1L3与L4之间之间打via走一段地线做隔离

5.2Pin4与pin5之间打via走一段地线做隔离

5.3由于L3与R2并联,L3应该选择更靠近IC pin脚

6.电路元器件,尽量丝印紧靠,并使用较小封装

6.1目的是减少两元件之间的走线,减少走线的电感量产生

7电源走线

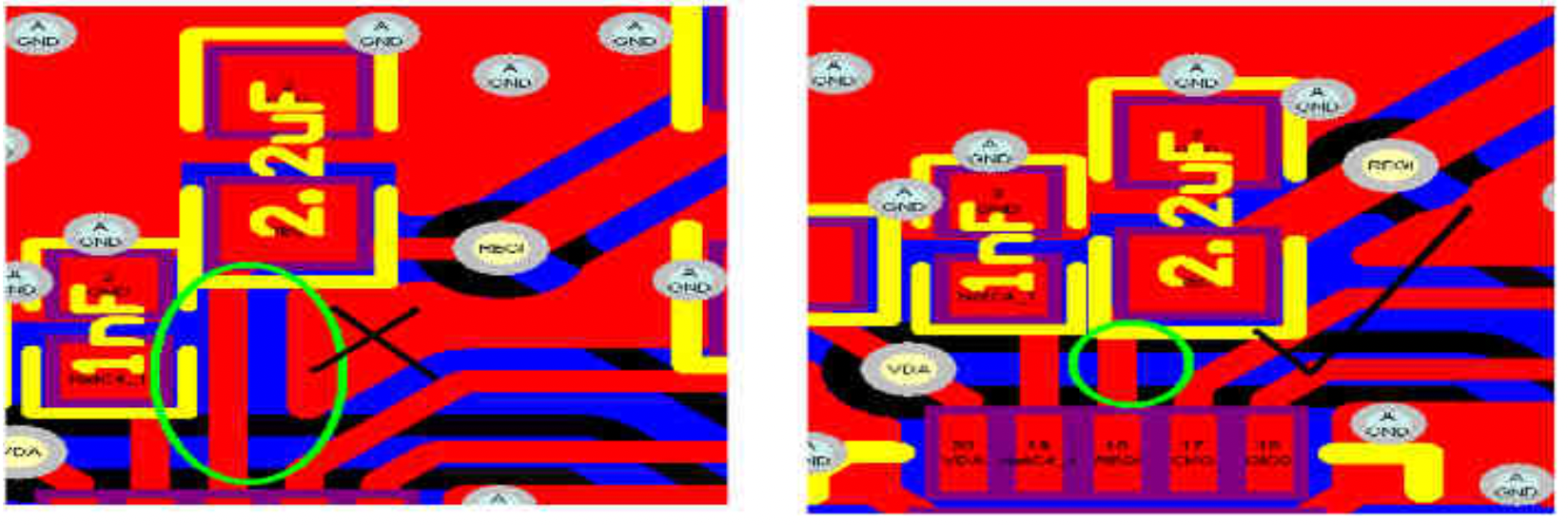

7.1电源滤波电路中的电容尽量靠近VDD pin脚,以确保滤波电容与进入VDD的环路面积最小

7.1.1强调一点:参考电路中的电源滤波电容一个都不能少,每个电容都有其不同的作用,少了会有死机或振荡现象

7.1.2进入IC之前,电源先经过大电容,再经过小电容滤波(小电容靠近IC pin,大电容放外面)

8.晶振

8.1晶振size3225,PCB封装中间是可以走线的

8.1.1晶振有49S插件;还有size更小的2520贴片封装

8.2晶振尽量靠近IC,减少晶振走线长度,同时晶振及其晶振走线下方不要走任何走线

8.3晶振接地PAD,请在PAD边缘多打下地via,(切记不要打在pad上面,防止晶振吃锡不足)

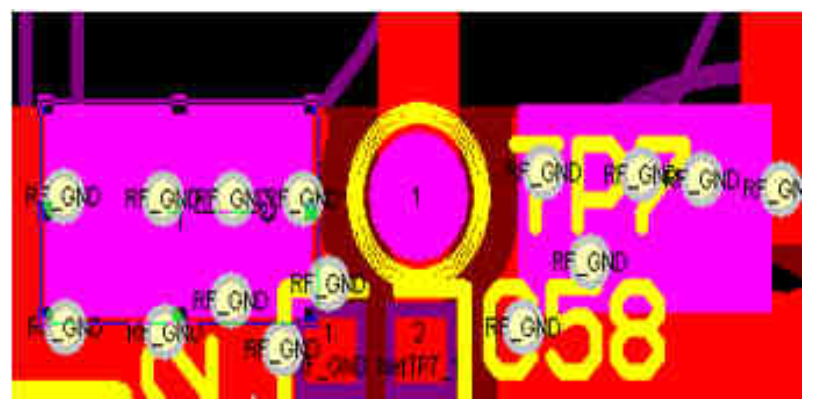

9.务必要留出测试点,为了for研发调试及治具测试 测试点size直径最少大于1.5mm 两测试点之间大于2.0mm

9.1留出SPI测试点 (SCS SCK SDIO GIO1 GIO2)

9.2 留出REGI(电源)及GND测试点

9.3留出RF测试点及RF参考地测试点

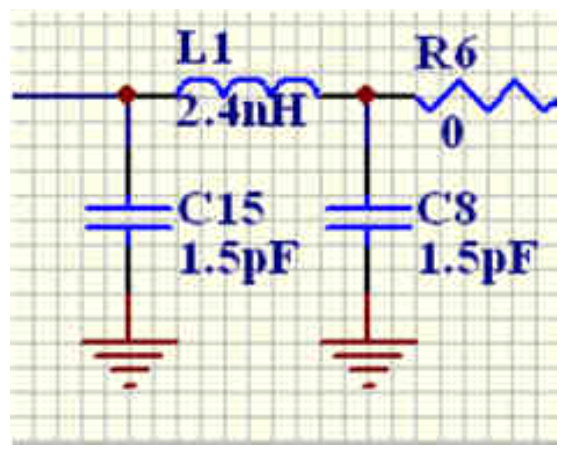

10.滤波器架构

10.1:滤波器架构是为了for法规使用,如果不过法规,滤波电路可以省掉,或者用来调适与天线的50ohm匹配

11.电源VDDA走线

11.1电源VDDA走线建议下图

11.2Pin7为锁相环电路,VDDA走线请远离锁相电路,不要走在其下方

11.3不建议电源VDDA走线走IC正下面,请走IC外围

12.洗板

12.1板厚:0.8mm

12.2板材:FR-4

12.3表面:镀化金

12.4Via :盖油

13.畫板時: 有時候因為面積限制,元器件不見得都要90度擺放(垂直或水平), 可以用任意角度(ex: 45, 30度)來擺放

审核编辑 黄宇

-

pcb

+关注

关注

4420文章

24022浏览量

426967 -

RF

+关注

关注

66文章

3204浏览量

172325 -

2.4GHz

+关注

关注

0文章

50浏览量

18957

发布评论请先 登录

探索ADNK - 6033 - ND24 USB 2.4GHz RF无线激光鼠标设计套件

ADNK - 6033 - CC24 USB 2.4GHz RF无线激光鼠标设计套件解析

深入解析MAX2831/MAX2832:2.4GHz - 2.5GHz 802.11g/b RF收发器

MAX2830:2.4GHz - 2.5GHz 802.11g/b RF 收发器的卓越之选

SGM22001C:2.4GHz 802.11n WiFi 前端模块的技术剖析

CC2520 2.4GHz IEEE 802.15.4/ZigBee® RF收发器深度解析

探索CC2590:2.4GHz RF前端的卓越之选

CC2543:2.4GHz RF应用的集成化解决方案

深入解析CC2545:2.4GHz RF应用的理想片上系统解决方案

内置2.4GHz有源模块PDA手持终端深度评测

CMOS 2.4GHZ 发射/接收 WLAN RFeIC skyworksinc

2.4GHZ 发送/接收 ZIGBEE RFEIC,带分集开关 skyworksinc

2.4GHZ CMOS WLAN/BT 双模 RFEIC,带 PA、LNA skyworksinc

CMOS 2.4GHZ ZIGBEE/ISM 发射/接收 RFeIC skyworksinc

2.4GHz RF IC 布局指导

2.4GHz RF IC 布局指导

评论