SN74HC165DR是一种8位串行至并行移位寄存器。它是一款集成电路芯片,通常用于将并行输入转换为串行输出。在这篇文章中,我们将详细介绍SN74HC165DR的工作原理,包括其内部结构和关键功能。

SN74HC165DR是一种非常常用的集成电路芯片,在数字电子系统中起着重要的作用。它具有高速、高性能和低功耗的特性,可以完成从并行到串行的数据转换,并通过串行输出将数据传输到后续的处理电路中。

SN74HC165DR的内部结构

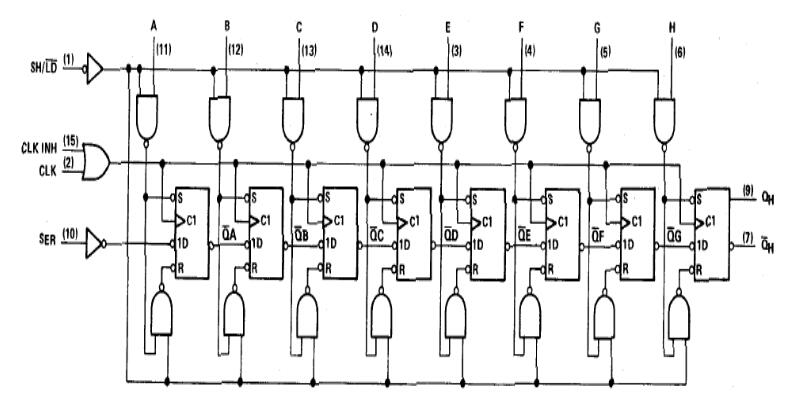

SN74HC165DR由多个逻辑门、存储单元和控制电路组成。

- 逻辑门:SN74HC165DR内部包含多个逻辑门,用于实现数据的输入和输出操作。这些逻辑门可以执行与、或、非等逻辑运算,以实现数据处理和控制功能。

- 存储单元:SN74HC165DR内部包含8个存储单元,用于存储输入数据。每个存储单元均为D触发器,可以存储一个比特位的数据。

- 控制电路:SN74HC165DR还包含一些控制电路,用于控制数据输入和输出的时序。通过适当的时序控制,可以实现数据的稳定和准确的传输。

SN74HC165DR的关键功能

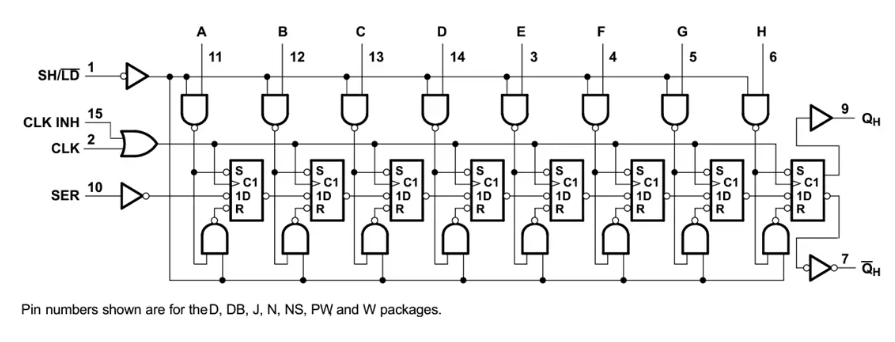

- 并行输入:SN74HC165DR具有8个并行输入引脚,分别为A0~A7。通过这些引脚,可以将8个并行输入数据传输到芯片内部。

- 串行输出:SN74HC165DR具有一个串行输出引脚,称为Q7。通过这个引脚,可以将数据按顺序传输到后续的电路中。

- 移位操作:SN74HC165DR具有一个移位引脚,称为SH/LD (Shift/Load)。通过在移位操作时将SH/LD引脚置高,可以使芯片进入移位模式,此时输入数据将通过串行输出引脚按顺序输出。当移位操作完成后,将SH/LD引脚置低,芯片将停止移位,并将输出数据保持不变。

- 并行加载:SN74HC165DR具有一个并行加载引脚,称为PL (Parallel Load)。通过将PL引脚置高,可以使芯片进入并行加载模式。在这种模式下,芯片会读取并行引脚的状态,并将数据存储到内部的存储单元中。当PL引脚置低时,芯片将停止并行加载,并将存储的数据保持不变。

- 串行时钟:SN74HC165DR具有一个串行时钟引脚,称为CLK (Clock)。通过在每个时钟脉冲到来时改变输入数据,可以实现数据的串行移位操作。

SN74HC165DR的工作原理

SN74HC165DR的工作过程可以分为以下几个步骤:

- 并行加载:如果PL引脚置高,芯片将进入并行加载模式。此时,芯片将读取并行输入引脚A0~A7的状态,并将这些数据存储到内部的存储单元中。

- 移位操作:如果SH/LD引脚置高,芯片将进入移位模式。在移位模式下,芯片将按顺序将存储的数据从Q7引脚输出。通过在每个时钟脉冲到来时改变输入数据,芯片可以实现数据的串行移位操作。

- 控制时序:芯片内部的控制电路会根据时钟信号和控制引脚的状态来控制数据的传输。通过适当的时序控制,可以确保数据的稳定和准确的传输。

总结

SN74HC165DR是一种功能丰富的集成电路芯片,具有高速、高性能和低功耗的特性。它可以将并行输入转换为串行输出,并通过适当的时序控制实现数据的稳定和准确的传输。在数字电子系统中,SN74HC165DR扮演着重要的角色,广泛应用于数据采集、控制和通信等领域。通过对SN74HC165DR的工作原理的详细了解,我们可以更好地理解和应用这一功能强大的集成电路芯片。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

463文章

54429浏览量

469364 -

集成电路

+关注

关注

5464文章

12686浏览量

375729 -

移位寄存器

+关注

关注

4文章

352浏览量

23423

发布评论请先 登录

相关推荐

热点推荐

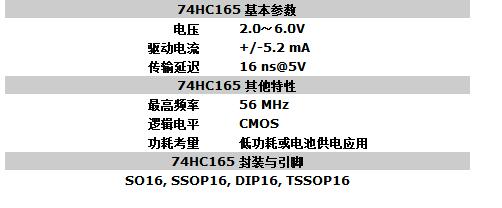

[转帖]SN74HC165DR的技术参数

SN74HC165DR的技术参数产品型号:SN74HC165DR封装/温度(℃):SOIC-16/-40~85描述:8位移位寄存器(并入串出)价格/1片(套):¥1.30相关

发表于 09-18 15:37

74hc165无法使用

检测到一个按键后LED灯亮下,现在无法实现,求助怎么解决!!!#include#include***it led_dr=P2^0;***it hc165_si_dr=P1^1

发表于 12-13 21:17

74HC165读取按键键值的问题

本帖最后由 giakou 于 2016-3-15 14:28 编辑

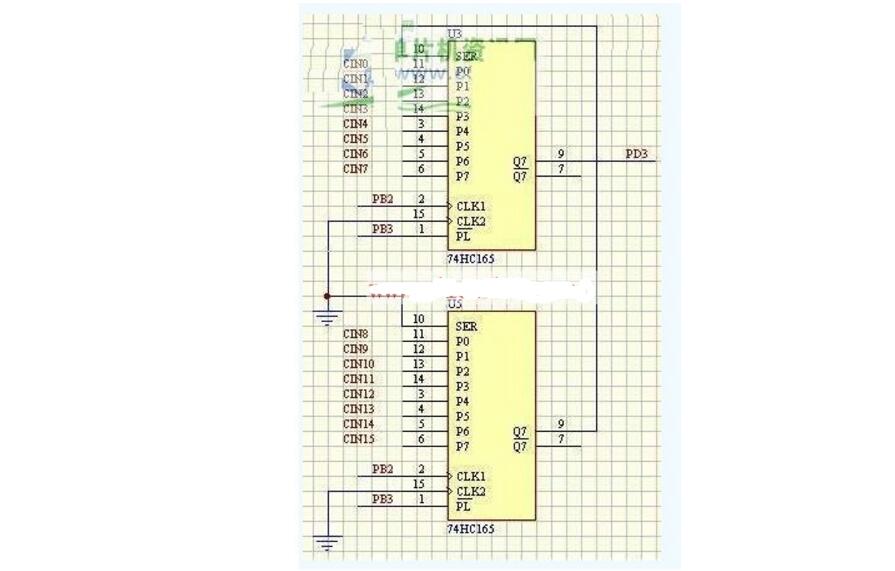

3 片74HC165读取按键,单片机与3片74HC165通过短线连接时没有问题,通过超过两米长的连接时,单片机只能识别一片

发表于 03-15 14:24

74HC165

74HC165可以把并行输入后串行输出,最多可以连接多少个一起用,我有400个并口,可以用50个74HC165连接一起用,数据会出错吗,怎么连接的,高手指点下

发表于 03-30 18:01

74HC165编程篇

前面已介绍过74HC165的工作原理,接下来编写用51单片机来驱动这个片子的代码并用Proteus做了仿真,这次就不使用stm32来驱动了,因为仿真软件里没有ST的单片机。写74HC165的驱动也

发表于 07-02 08:07

74HC165 pdf datasheet

MM54HC165/MM74HC165Parallel-in/Serial-out 8-Bit Shift RegisterGeneral DescriptionThe MM54HC165

发表于 08-06 09:39

•110次下载

74hc165中文资料详细(74hc165工作原理_引脚图及功能_应用电路_逻辑图)

本文介绍了74hc165特性、74HC165逻辑图、74hc165基本参数及真值表,其次介绍了74HC165时序图、分析了74hc165

发表于 02-02 11:16

•21.5w次阅读

74hc165使用方法(74hc165功能_内部结构图_时序图)

74HC165是一款高速CMOS器件。本文开始介绍了74HC165参数与74hc165引脚及功能,其次介绍了74hc165内部结构图与使用方法,最后介绍了

发表于 02-02 11:42

•5.8w次阅读

74hc165级联用法(74hc165级联电路图及程序)

74HC165是一款高速CMOS器件,74HC165遵循JEDEC标准no.7A。74HC165引脚兼容低功耗肖特基TTL(LSTTL)系列。本文介绍了74HC165的级联电路图,介绍

发表于 02-02 13:55

•5.7w次阅读

SN74HC165-EP 增强型产品 8 位并行负载移位寄存器

电子发烧友网为你提供TI(ti)SN74HC165-EP相关产品参数、数据手册,更有SN74HC165-EP的引脚图、接线图、封装手册、中文资料、英文资料,SN74HC165-EP真值表,SN

发表于 11-02 19:20

SN74HC165-Q1 8位并行负载移位寄存器技术解析

Texas Instruments SN74HC165/SN74HC165-Q1 8位并行负载移位寄存器是一种将数据移向串行( ~QH~ )输出的寄存器。通过八个单独的直接数据(A-H)输入提供

SN74HC165QPWRQ1 汽车类 8 位并联负载移位寄存器

SN74HC165QPWRQ1汽车类8位并联负载移位寄存器产品型号:SN74HC165QPWRQ1产品品牌:TI/德州仪器产品封装:TSSOP16产品功能:移位寄存器SN74HC165

sn74hc165dr工作原理

sn74hc165dr工作原理

评论