简介

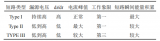

本文汇集了 SiC MOSFET 最新结果的特定方面,涉及由于应用交流栅极偏置应力(也称为栅极开关应力)导致的阈值电压 (VT) 退化及其影响沟槽几何器件对负偏压过应力 (NBO) 效应的强烈依赖。交流栅极偏置应力引起的退化是 SiC MOSFET VT 不稳定性的一个潜在重要方面,最近才被揭示。我们最近的工作表明,这种现象包括看似永久性的 VT 偏移和观察到的 VT 滞后的增加。它还表明,这种退化效应与栅极开关周期的数量成正比,在开关周期期间从积累到强反转再返回的更快转换会导致每个周期更大的退化,并且这种退化可以在 300 ℃ 时退火。最后,当暴露于超过器件负偏压额定值的 NBO 时,这种退化效应主要出现在沟槽几何器件中。我们还发现,并非所有沟槽器件都同样容易受到影响,这表明器件设计和加工细节对于这种影响的严重程度至关重要。由于研究的平面器件和应用的开关周期数量相对较少,早期研究双极交流应力的工作未能发现任何有意义的东西。

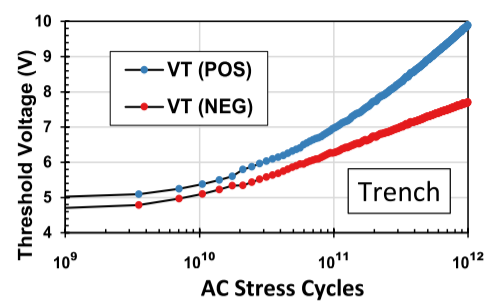

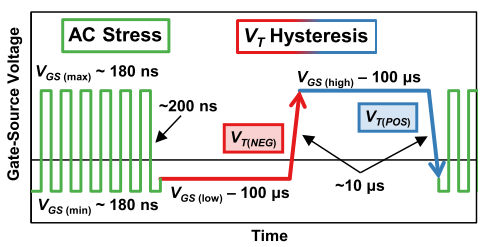

图 1 说明了在某些沟槽几何器件中观察到的基本退化效应,显示了 VT 磁滞测量序列的低侧和高侧变化图,其中应用了第一个栅极偏置极性,并且测量 VT(通过在大约 10 μs 完成快速 I-V 测量后以固定电流水平提取 VGS),然后应用另一个极性并重新测量 VT,揭示存在的 VT 迟滞——作为总电压的函数应用交流应力循环(均在室温下)。在每个栅极极性下,测量 VT 磁滞的应力时间为 100 μs,这与 AC 应力本身施加的 200 ns 有效应力时间形成对比(参见图 2 中所示的应力和测量示意图)。观察到的 VT 不稳定性变化非常显着,在 1012 个总 AC 应力循环后,VT 磁滞从最初的 0.25 V 增加到约 2.25 V,VT 磁滞的低侧增加约 3 V,从 4.7 V 增加到 7.7 V,高侧增加约 5V,从约 5V 到 10V。还值得注意的是,观察到的 VT 迟滞的增加仅在 VT 首次发生显着变化后发生。这一点在下面的两张图中表现得更清楚。

图 1. VT 磁滞测量的高侧 [VT(POS)] 和低侧 [VT(NEG)] 作为沟槽 SiC MOSFET 中交流应力循环(室温)的函数(使用快速 I-V 进行测量) 。

图 2. 示意图显示了交流应力循环和 VT 磁滞测量(在恢复应力之前仅描述了一次完整迭代)——全部在室温下进行。

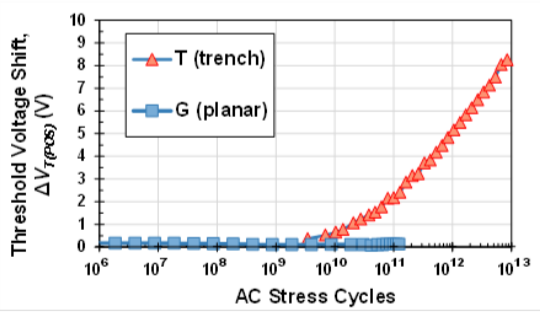

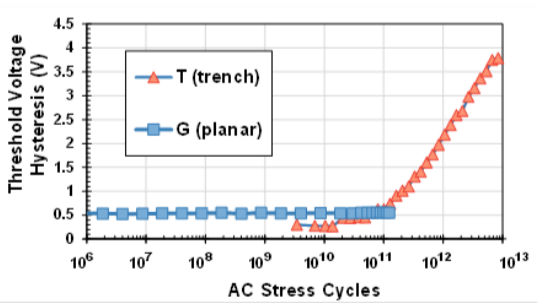

图 3 将沟槽 SiC MOSFET 器件看似永久的 VT 偏移与平面 SiC MOSFET(来自同一制造商)中观察到的没有任何影响的情况进行了比较。沟槽器件的 VT 开始在 109 到 1010 个总交流应力周期之间发生明显变化,在 1012 个总交流应力周期后变化了约 5V,在约 1013 个总应力周期后变化了超过 8V,没有饱和的迹象!图 4 显示,最初,平面器件(不会退化)的 VT 磁滞是沟槽器件的两倍,但超过大约 1011 个总 AC 应力循环后,沟槽器件的 VT 磁滞显着增加(大约VT 已移动约 2 V 的时间)。由于下面将详细讨论的原因,这并不代表额外电荷陷阱的激活。相反,我们发现后一种效应是由于当 VGS - VT 正移几伏时 VT 磁滞测量的低侧显着下降所致。还应该注意的是,大约 1 s 的慢速 I-V 测量显示的 VT 偏移与快速 I-V 测量一样多,如果 VT 偏移是由于某种永久电荷捕获效应(永久电荷捕获效应)造成的,则这是可以预料到的,至少在负偏压下高温退火之前)。另一方面,缓慢的 I-V 测量显示出更小的 VT 磁滞效应(以及 VT 磁滞的变化),这也是可以预料的,因为 VT 磁滞是由动态、短暂的电荷俘获引起的,其大小为测量速度依赖。

图 3. 沟槽和平面 SiC MOSFET(来自同一制造商)的 VT 偏移与 AC 应力循环总数的比较。

图 4. 沟槽和平面 SiC MOSFET(来自同一制造商)的 VT 磁滞与 AC 应力周期总数的比较。

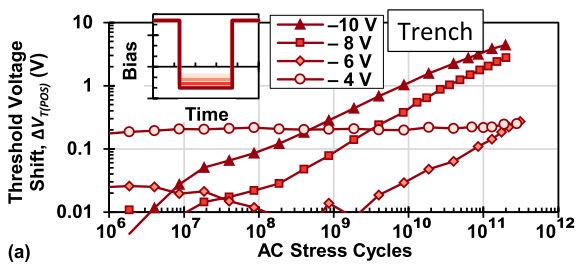

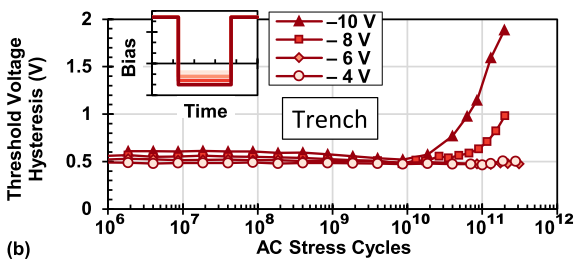

图 5 显示了 VT 偏移与交流应力周期总数的相关性,作为交流应力期间施加的低侧栅极偏置 [VGS (min) - 见图 2] 的函数。栅极偏压越负,退化效应越强。 (对于图 1、3 和 4 所示的结果,VGS (min) 为 -10 V。)计算 VT 偏移的参考点是 VT 磁滞测量值 [VT(POS)] 的高侧。图 6 显示了低侧栅极偏置与 VT 磁滞相应增加的关系。再次清楚的是,VT 迟滞的增加直到 VT 偏移超过至少 1 V 才开始,并且直到大约 2 V 偏移才显着。

图 5. 交流应力的低侧栅极偏压 VGS(最小值)对观察到的 VT 偏移(在 VT 磁滞包络的高侧测量)的影响,作为总应力周期的函数。 VGS(最大值)= +22 V。

图 6. 交流应力的低侧栅极偏压 VGS(最小值)对观察到的 VT 磁滞(使用 +22 V / –4 V 测量)的影响,作为总应力周期的函数。 VGS(最大值)= +22 V。

为了更好地理解 VT 偏移和由于 AC 应力引起的退化而引起的 VT 磁滞变化之间的关系,特别是在沟槽几何器件中,查看 VT 磁滞对施加在低侧的栅极偏压的敏感度 [VGS] 具有指导意义。在没有交流应力的情况下进行 VT 磁滞应力和测量序列(加工后的器件)。图 7 显示了 VT 磁滞幅度如何随着负栅极偏压的增加(同时将高侧 [VGS(高)] 保持在 +22 V)而增加(相对于 VT 磁滞应力间隔时间绘制)。从 VGS(低)= –6V(以粗体突出显示)开始,VT 迟滞幅度显着增加,并且 VGS(低)每增加 2V,VT 迟滞幅度继续增加约 1V,直到 VGS(低)= –14 V(也以粗体突出显示),此后效果很快开始最终饱和(毫不奇怪,制造商为该器件指定的最大负栅极偏压为 –4 V)。相比之下,同一制造商的平面几何器件在相同的负栅极偏压范围内,VT 迟滞几乎没有增加。栅极偏置值(见图 8)。对于平面器件,影响很小,并且在 VGS(低)= –6 V 附近开始饱和。(应该注意的是,如图 7 所示,沟槽器件中对 NBO 的大灵敏度对于两者来说是相同的)主要制造商进行了评估,尽管在 NBO 条件下 [见图 5],交流应力造成的显着退化仅对两家制造商之一而言是真实的。

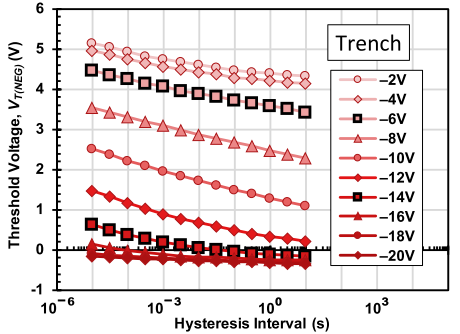

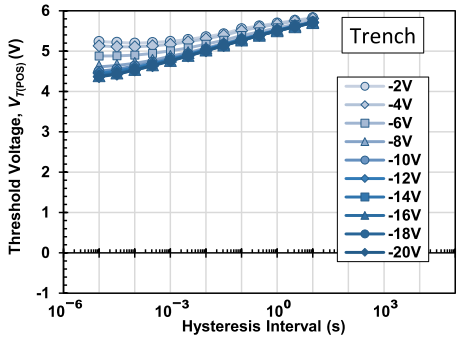

图 9 和图 10 提供了对沟槽几何器件中 VT 磁滞大幅增加的驱动因素的进一步了解(如图 7 所示)。图 9 显示了 VT 磁滞包络线 [VT(NEG)] 的低侧如何随着 VT 磁滞应力 [VGS(低)] 期间负栅极偏压的增加而沿负方向显着向下移动 — 再次绘制与 VT 磁滞应力的关系图间隔时间(见图2)。另一方面,图 10 显示,随着 VT 磁滞应力期间负栅极偏压的增加,同一 VT 磁滞包络 [VT(POS)] 的高侧仅在负方向上稍微向下移动。 (在别处研究了在 VT 磁滞应力 [VGS(高)] 期间改变正栅极偏压的情况。)因此,图 7 中所示的 VT 磁滞幅度的大幅增加几乎完全是由于随着 NBO 的增加,VT 位于 VT 迟滞包络线的低侧。

图 9. 沟槽 SiC MOSFET 的负偏压过应力会导致 VT 磁滞包络线 [VT(NEG)] 的低侧出现显着的负漂移。这种效应在阈值电压稍为负时饱和。 VGS(高)保持恒定在 +22 V。(未施加交流应力。)

图 10. 沟槽 SiC MOSFET 的相同负偏压过应力仅导致 VT 磁滞包络线 [VT(POS)] 的高侧产生较小的负漂移。 VGS(高)保持恒定在 +22 V。(未施加交流应力。)

这意味着,当 VT 由于交流应力退化效应而正向移动时,VGS – VT 将相应减小,从而导致 VT 迟滞测量期间应用的有效栅极偏置值发生变化。例如,在任何正 VT 偏移之前,应用 VGS(低)= −4 V 不会导致 NBO 条件。但 VT 的 2V 正移将导致 VGS - VT 发生变化,从而使 VGS(低)实际上变为 -6V,从而增加 VT 迟滞。这导致 VT (NEG) 值变得比原本应有的正值小 1 V。这解释了为什么图 1 中 VT 磁滞随着正方向偏移而变宽,以及为什么 VT 偏移首先发生,只有当 VT 首先偏移至少 1 V 时,VT 磁滞才会开始增加。因此,不需要额外的陷阱激活来解释沟槽器件中交流应力引起的 VT 滞后的增加。

总结和结论

当暴露于具有负偏压过应力的双极交流应力(栅极偏压超过制造商建议的最大负栅极工作电压,在感兴趣的特定情况下为 -4 V)时,来自特定制造商的沟槽器件会经历较大的在大约 1013 个总周期后,正 VT 偏移接近 10 V,没有任何饱和迹象,而来自同一制造商的平面器件(以及来自其他制造商的所有器件)显示出的影响要小得多。观察到的 VT 磁滞相应大幅增加并不是由于新陷阱的激活,而是由于标准 VT 磁滞测量负偏压侧 VGS-VT 的增加(在平面器件中未观察到)。一般来说,SiC 沟槽 MOSFET 在 VT 磁滞方面表现出对 NBO 的敏感性,但仅这种现象不足以引起交流应力引起的漂移。退化机制可能是由于深态中的电子俘获所致,导致 VT 看似永久的正移。然而,这种损坏可以通过在高温 (300 °C) 下施加负偏压来消除。

审核编辑:汤梓红

-

MOSFET

+关注

关注

147文章

7156浏览量

213144 -

半导体

+关注

关注

334文章

27286浏览量

218079 -

SiC

+关注

关注

29文章

2804浏览量

62607

原文标题:SiC MOSFET 中的交流应力退化

文章出处:【微信号:芯长征科技,微信公众号:芯长征科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

为何使用 SiC MOSFET

SiC-MOSFET的应用实例

SiC-MOSFET与Si-MOSFET的区别

SiC-MOSFET的可靠性

沟槽结构SiC-MOSFET与实际产品

SiC-MOSFET有什么优点

SiC功率器件SiC-MOSFET的特点

浅析SiC-MOSFET

SiC-MOSFET器件结构和特征

SiC MOSFET的器件演变与技术优势

SiC MOSFET体二极管双极性退化问题

SIC MOSFET在电路中的作用是什么?

SiC MOSFET短路失效的两种典型现象

SiC MOSFET中的交流应力退化

SiC MOSFET中的交流应力退化

评论