作者:Stephen Evanczuk

投稿人:DigiKey 北美编辑

航空航天和国防 (ADEF) 系统设计人员面临着迫切的需求,要求通信系统不断降低功耗并缩小体积,并能够对动态信号环境做出敏捷响应。软件无线电 (SDR) 技术超越了传统无线电架构,可帮助满足对 ADEF 无线电快速变化的需求,但 SDR 的实施也提出了诸多挑战,包括满足功能要求和满足减小尺寸、重量和功耗 (SWaP) 的需求。

本文介绍了 [Analog Devices] 提供的一种更高效的 SDR 解决方案,其可以简化低功耗、紧凑型敏捷通信系统的设计,同时又不影响性能。

新出现的挑战带来了更苛刻的要求

在越来越多的工业和任务关键型应用中,设计人员面临着实现更高效通信的需求,这些应用包括安全无线电通信、自适应雷达、电子战、增强型 GPS 导航。这些新挑战催生了对增强宽带运行、更高动态范围、更优频率捷变、可重配置能力的需求。然而,随着通信系统迁移到体积更小的电池供电平台,包括无人机 (UAS) 和便携式设备,这些更苛刻的功能要求可能会与减小 SWaP 的需求相冲突。

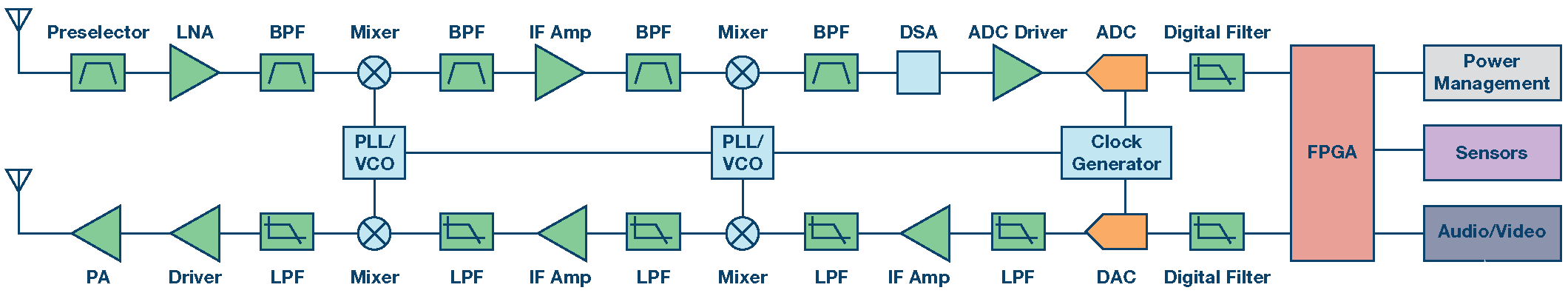

基于传统分立式超外差无线电架构的设计解决方案具有高性能、宽动态范围、小杂散噪声的优点。这种方法的核心是从中频 (IF) 分离出所需信号,对于设计人员来说,这是一项挑战,通常会导致设计复杂和高 SWaP,并且几乎不具备可重配置能力(图 1)。

[ ]图 1:传统超外差无线电架构可以满足性能目标,但由于其复杂性,该架构无法实现最小化 SWaP 的新兴目标。(图片来源:Analog Devices)

]图 1:传统超外差无线电架构可以满足性能目标,但由于其复杂性,该架构无法实现最小化 SWaP 的新兴目标。(图片来源:Analog Devices)

相比之下,直接变频(零中频)架构既降低了滤波要求,又减少了对高带宽模数转换器 (ADC) 的需求,从而简化了设计,可在单芯片上实施(图 2)。

图 2:零中频无线电架构可满足对更高性能和更低 SWaP 的需求,但信号隔离是一项挑战。(图片来源:Analog Devices)

图 2:零中频无线电架构可满足对更高性能和更低 SWaP 的需求,但信号隔离是一项挑战。(图片来源:Analog Devices)

尽管直接变频架构具有明显的优势,但其自身的实施难题也限制了它的广泛应用。在这种架构中,信号被转换为本地振荡器 (LO) 频率的射频 (RF) 载波,但直流 (DC) 偏移误差和 LO 漏泄会导致误差通过信号链传播。此外,即便在同一芯片内,信号路径的差异也会导致同相 (I) 和正交 (Q) 信号出现增益或相位不匹配,从而产生正交误差,影响信号隔离。

SDR 技术具有克服传统无线电架构局限性的潜力,但很少有解决方案能够满足与 ADEF 应用相关的更广泛要求。使用 Analog Devices 的 [ADRV9002]射频收发器,开发人员可以轻松满足这些应用对更高性能和功能的需求,同时减小 SWaP。

集成功能以更低 SWaP 的提供优化的性能

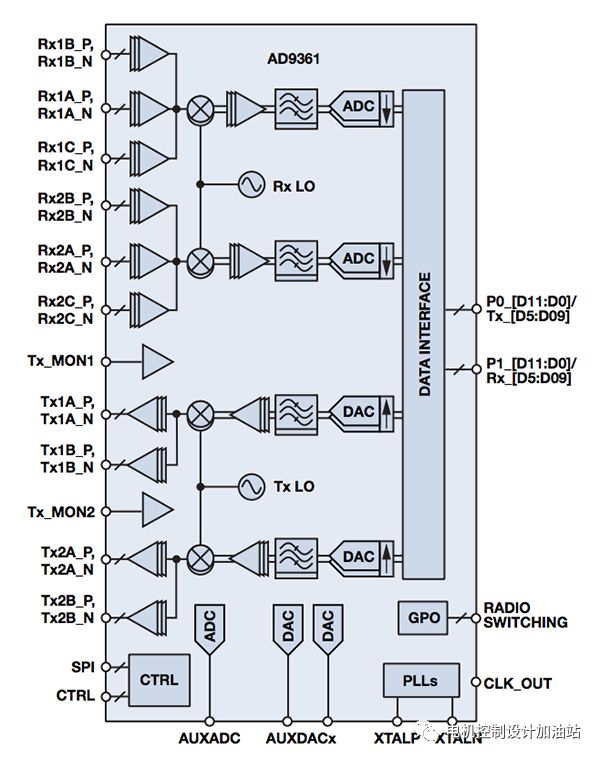

支持从 30 MHz 到 6,000 MHz 的频率范围,ADRV9002 是一款高度集成的收发器,包含满足各种应用需求所必需的所有射频、混合信号和数字功能。该器件同时支持时分双工 (TDD) 和频分双工 (FDD) 工作方式,具有单独的双通道直接变频接收器和发射器子系统,包括可编程数字滤波器、直流偏移校正和正交误差校正 (QEC)。

在片上合成器子系统中,ADRV9002 具有两个不同的锁相环 (PLL) 路径:一个用于高频射频路径,另一个用于数字时钟和转换器采样时钟。最后,该器件的数字信号处理模块包括一个 [Arm®]M4 嵌入式处理器,用于处理自校准和控制功能(图 3)。

图 3:ADRV9002 射频收发器集成了双接收 (RX) 和发射 (TX) 子系统。(图片来源:Analog Devices)

图 3:ADRV9002 射频收发器集成了双接收 (RX) 和发射 (TX) 子系统。(图片来源:Analog Devices)

ADRV9002 具有提供完整信号链的发射器和接收器子系统,可在零中频模式或低中频模式下工作,适用于对相位噪声敏感的应用。每个发射器子系统都提供一对数模转换器 (DAC)、滤波器和混频器,用于重新组合 I 和 Q 信号,并将其调制到载波频率,以便进行传输。

每个接收器子系统都集成了一个用于增益控制的电阻输入网络,为电流模式无源混频器馈送信号。然后,一个跨阻放大器将混频器的电流输出转换为电压电平,并通过一个具有高动态范围的 ADC 进行数字化。在 TDD 运行模式中或仅使用一个接收器系统的 FDD 应用中,发射器空闲时隙期间,未使用的接收器输入可用于监测发射器通道的 LO 漏泄和 QEC,或未使用的接收器输入可用于监测功率放大器 (PA) 输出信号电平。

后一种功能可在 ADRV9002 的集成数字预失真 (DPD) 功能中发挥作用,该功能利用监测的功率放大器信号电平来应用线性化输出必需的适当预失真。该功能使 ADRV9002 能够驱动功率放大器接近饱和,从而优化其效率。

调节功率和性能

ADRV9002 器件在 196 球芯片级封装 (CSP) 球栅阵列 (BGA) 中提供了完全集成的解决方案,并最大限度地减小了 SDR ADEF 通信系统的尺寸和重量。为了帮助开发人员进一步优化功耗,ADRV9002 集成了多种功能,专门设计用于帮助开发人员在性能与功耗之间找到合适的平衡点。

在块级别,开发人员可在单信号路径块上部署功率调整,以降低性能为代价,换取更低的功耗。此外,还可以禁用 TDD 接收 (RX) 和发射 (TX) 帧中的数据块,牺牲 RX/TX 或 TX/RX 的周转时间来降低功耗。为了进一步帮助开发人员优化功耗与性能,每个 ADRV9002 接收器子系统都包括两对 ADC。其中一对 ADC 由高性能 Sigma-Delta ADC 组成,而第二对 ADC 可在功耗较为关键时接手工作。

对于周期性不活动的应用,可以使用 ADRV9002 的 RX 监测模式。在该模式下,ADRV9002 以编程设定的占空比,在最低功耗睡眠状态与检测状态之间交替运行。在检测状态下,该器件会激活接收器,并尝试在由开发人员编程的带宽和 RX LO 频率上获取信号。如果该器件测量到的信号功率水平高于设定的阈值,则会退出监测模式,ADRV9002 的模块加电,以处理所需的信号。

快速原型设计和开发

为了帮助工程师快速进行评估、原型设计和开发,Analog Devices 为基于 ADRV9002 的系统提供了广泛的硬件和软件支持。

在硬件支持方面,Analog Devices 提供了一对基于 ADRV9002 的无线电卡:

- [ADRV9002NP/W1/PCBZ],适用于工作频率在 30 MHz 至 3 GHz 范围内的低频带应用

- [ADRV9002NP/W2/PCBZ],适用于工作频率在 3 至 6 GHz 范围内的高频段应用

这些无线电卡配备 FMC 连接器,支持板载 ADRV9002,具有功率调节和硬件接口,以及时钟和多芯片同步 (MCS) 分配功能。这些卡通过 FMC 连接器连接到 FPGA 主板,例如 [AMD ]评估板,以实现功率和应用控制。

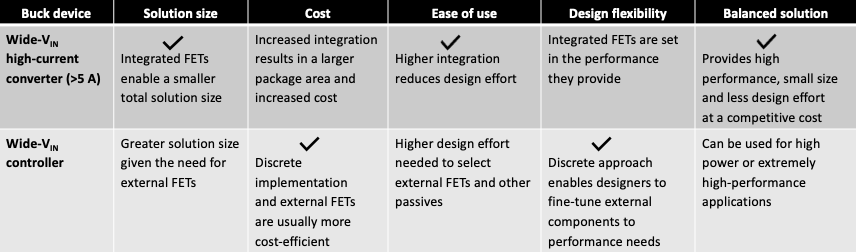

Analog Devices 在支持包中提供了 ADRV9002NP 无线电卡的完整原理图和物料清单 (BOM)。原理图和物料清单为大多数应用的定制硬件开发提供了有效的着手点。某些应用需要额外的射频前端,以满足特定的信号调节要求。对于这些应用,开发人员只需增加几个元器件,即可完成设计(图 4)。

图 4:高度集成的 ADRV9002 收发器使开发人员能够快速实现专用设计。(图片来源:Analog Devices)

图 4:高度集成的 ADRV9002 收发器使开发人员能够快速实现专用设计。(图片来源:Analog Devices)

在本示例中,开发人员可以使用 Analog Devices 的下列电源管理元器件,快速实现合适的射频前端:

- [ADRF5160] 射频开关

- [HMC8411]低噪声放大器 (LNA)

- [ADMV8526]数字可调谐带通滤波器

- [HMC1119] 射频数字步进衰减器 (DSA)

- [HMC8413] 激励放大器

- [HMC8205B]功率放大器

Analog Devices 通过文档和可下载软件包提供全面的软件开发支持。使用上述开发硬件的开发人员可以基于 Analog Devices 的产品线软件或开源软件包来进行原型设计和开发。

本文下面将仅讨论产品线软件。有关开源开发方法的更多信息,请参阅 Analog Devices 的《ADRV9001/2 原型开发平台用户指南》(ADRV9001/2 Prototyping Platform User Guide)。Analog Devices 规定,公司支持文档中的术语“ADRV9001”是一个系列代号,包括 ADRV9002 以及 ADRV9001 系列的其他成员。因此,下面的文本或图表中提及的 ADRV9001 内容适用于本文重点介绍的 ADRV9002 器件。

Analog Devices 基于 Windows 的[收发器评估软件] (TES) 工具通过该公司的产品线软件开发工具包 (SDK) 分发,为快速配置和评估收发器性能提供了一个便捷的起点。

在使用 Analog Devices 基于 ADRV9002 的无线电卡和 AMD 的 ZCU102 评估板进行评估和原型开发过程中,TES 工具提供了一个图形用户界面 (GUI),用于配置硬件和观察捕获的数据(图 5)。

图 5:使用 SDK 工具包中的 TES 工具,开发人员能够在支持的评估平台上快速开始评估 ADRV9002 收发器。(图片来源:Analog Devices)

图 5:使用 SDK 工具包中的 TES 工具,开发人员能够在支持的评估平台上快速开始评估 ADRV9002 收发器。(图片来源:Analog Devices)

然后,TES 工具会自动生成 C# 代码,这些代码可以编译到 Linux 环境、MATLAB 环境或 Python 环境中。该 SDK 提供一整套软件库和应用程序编程接口 (API),包括为 AMD ZCU102 平台开发的 ADRV9001 API 软件包。

SDK 流程还直接支持从评估板评估和原型开发迁移到开发人员的定制目标环境(图 6)。

图 6:SDK 架构允许开发人员轻松地将评估结果扩展到自己的目标平台。(图片来源:Analog Devices)

图 6:SDK 架构允许开发人员轻松地将评估结果扩展到自己的目标平台。(图片来源:Analog Devices)

在此迁移流程中,开发人员像以前一样让 TES 自动生成代码。但是,开发人员不是直接使用这些代码,而是将所生成代码的编辑后版本部署到目标平台上。在实践中,所需的编辑工作主要限于删除引用 TES 工具所识别但目标系统中不需要的硬件组件的函数调用。该 SDK 架构包括 ADRV9001 库与开发人员硬件之间的硬件抽象层 (HAL) 接口,这样开发人员只需提供为特定硬件实现 HAL 接口代码的定制代码。因此,开发人员可以快速从使用 Analog Devices 无线电卡和 AMD 板的评估转向定制目标环境的开发。

总结

在日益复杂的信号环境中,航空航天和国防 (ADEF) 应用面临着越来越多的挑战。除了提供更宽的频率范围,满足对更高性能的需求之外,开发人员还必须减小 SWaP,以支持这些应用向电池供电系统的迁移。使用 Analog Devices 高度集成的收发器,开发人员可以实施 SDR 解决方案,更有效地满足这些要求。

-

adc

+关注

关注

98文章

6489浏览量

544415 -

SDR

+关注

关注

7文章

233浏览量

50455 -

通信系统

+关注

关注

6文章

1187浏览量

53320 -

SWAP

+关注

关注

0文章

51浏览量

12820 -

Tes

+关注

关注

0文章

13浏览量

7893

发布评论请先 登录

相关推荐

航空航天设备上MEMS传感器的应用

国防与航空航天解决方案

航空航天与国防市场未来的关键技术和趋势

PCB在军队的运用 航空航天和国防

是什么使航空航天和国防电子与常规PCB有所不同?

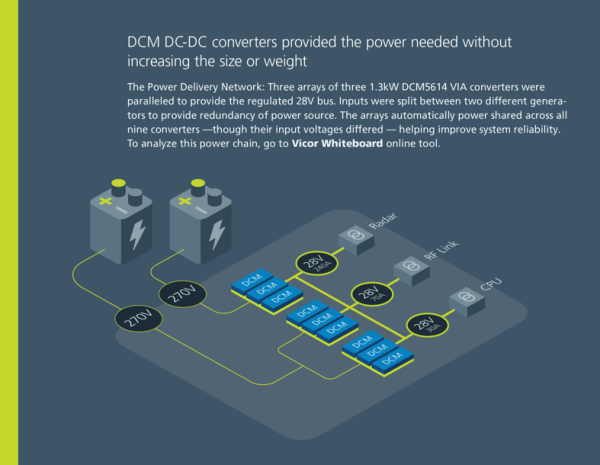

模块化电源满足航空航天和国防应用日益增长的需求挑战

先进的光纤组件支持航空航天和国防领域的新应用

射频收发器为航空航天和国防提供突破性的SWaP解决方案

在面向航空航天和国防应用的自适应 SDR 通信系统中使用敏捷射频收发器

在面向航空航天和国防应用的自适应 SDR 通信系统中使用敏捷射频收发器

评论