硬件术语

| 术语 | 解释说明 |

|---|---|

| sunxi | 指 Allwinner 的一系列 SOC 硬件平台 |

| M33 Star | 基于 ARMv8-M 架构 32 位元微处理器单元 |

| C906 | 平头哥推出的一款 RISC-V 架构的 64 位元处理器单元 |

| HIFI5 | Cadence 推出的 Cadence Tensilica HiFi 5 DSP 32 位处理器单元 |

| R128 | 全志推出的一款包含 M33+C906+HIFI5 处理器的 SoC 平台 |

| AudioCodec | 芯片内置音频接口 |

| I2S/PCM | 外置数字音频接口,常用于外接codec 模块。 |

| AHUB | 音频集线器,内部集成I2S 接口及DAM 混音器,可实现多路输入播放及硬件混音功能 |

| S/PDIF | 外置音响音频设备接口,一般使用同轴电缆或光纤接口。 |

| DMIC | 外置数字MIC 接口 |

| MAD | Mic Activity Detector, 语音能量检测模块 |

| 同源播放 | 不同音频模块同时播放同一份音频数据 |

| 同步采样 | 不同音频模块同时录音(可消除线程调度时差影响) |

软件术语

| 术语 | 解释说明 |

|---|---|

| FreeRTOS | 一种开源的实时操作系统 |

| gcc | GNU 开发的编程语言编译器。用于编译 M33 与 C906 上运行的程序 |

| xcc | Xtensa C/C++ 编译器。用于编译在 HIFI5 运行的程序 |

| hwspinlock | 在多核系统中,hwspinlock 提供一种硬件锁同步机制。 |

| ALSA | Advanced Linux Sound Architecture |

| ASoC | ALSA System on Chip |

| DAPM | 动态音频电源管理 |

| samplebit | 样本精度,记录音频数据最基本的单位,常见的有 16 位 |

| channel | 通道数,该参数为 1 表示单声道,2 表示立体声,大于 2 表示多声道 |

| rate | 采样率,每秒钟采样次数,该次数是针对帧而言。 |

| frame | 帧,记录了一个声音单元,其长度为样本长度与通道数的乘积。 |

| period size | 每次硬件中断处理音频数据的帧数。 |

| period count | 处理完一个 buffer 数据所需的硬件中断次数。 |

| buffer size | 数据缓冲区大小 (period size * period count) |

| DRC | 音频输出动态范围控制 |

| HPF | 高通滤波 |

| XRUN | 音频流异常状态,分为 underrun 和 overrun 两种状态。 |

| 交错模式 | 一种音频数据记录模式,数据以连续帧形式存放 (帧 1_L, 帧 1_R, 帧 2_L, 帧 2_R, —)。 |

| 非交错模式 | 一种音频数据记录模式,数据是以连续通道形式存放 (L-帧 1, L-帧 2, —, R-帧 2, R-帧 2, —)。 |

| tinyalsa | 在 Linux/RTOS 内核中与 ALSA 接口对接的库,可用于基本播录。 |

| alsalib | 在 Linux/RTOS 内核中与 ALSA 接口对接的库,可用于基本播录,并可与常见音频算法组合使用。 |

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

mcu

+关注

关注

146文章

17316浏览量

352427 -

R128

+关注

关注

0文章

41浏览量

116

发布评论请先 登录

相关推荐

ADC128S022的驱动架构参考 ti-adc128s052.c,要如何做移位生成12bit结果呢?

ADC128S022的驱动架构参考 ti-adc128s052.c, 具体如下图所示。

上层读取buf[1], buf[2]请问要如何做移位生成12bit结果呢?

发表于 12-16 06:32

求助,关于ADC128S102的采样速率问题求解

现采用ADC128S102采集温度电压,该芯片的采样速率在500ksps-1Msps。问题(1)一般ADC采样速率从0开始,使用时只要不超过最高采样率都可以使用,不明白该芯片500ksps最低采样

发表于 12-12 07:47

ADC128S102QML-SP 50 kSPS至1 MSPS、12位模数转换器数据表

电子发烧友网站提供《ADC128S102QML-SP 50 kSPS至1 MSPS、12位模数转换器数据表.pdf》资料免费下载

发表于 07-22 11:15

•0次下载

ADC128S052、ADC128S052-Q1模数转换器数据表

电子发烧友网站提供《ADC128S052、ADC128S052-Q1模数转换器数据表.pdf》资料免费下载

发表于 07-22 11:12

•0次下载

ADC128S022低功耗、8通道、CMOS、12位模数转换器数据表

电子发烧友网站提供《ADC128S022低功耗、8通道、CMOS、12位模数转换器数据表.pdf》资料免费下载

发表于 07-22 11:11

•0次下载

ADC128S102-SEP耐辐射8通道、50-kSPS至1-MSPS、12位ADC数据表

电子发烧友网站提供《ADC128S102-SEP耐辐射8通道、50-kSPS至1-MSPS、12位ADC数据表.pdf》资料免费下载

发表于 07-12 09:25

•1次下载

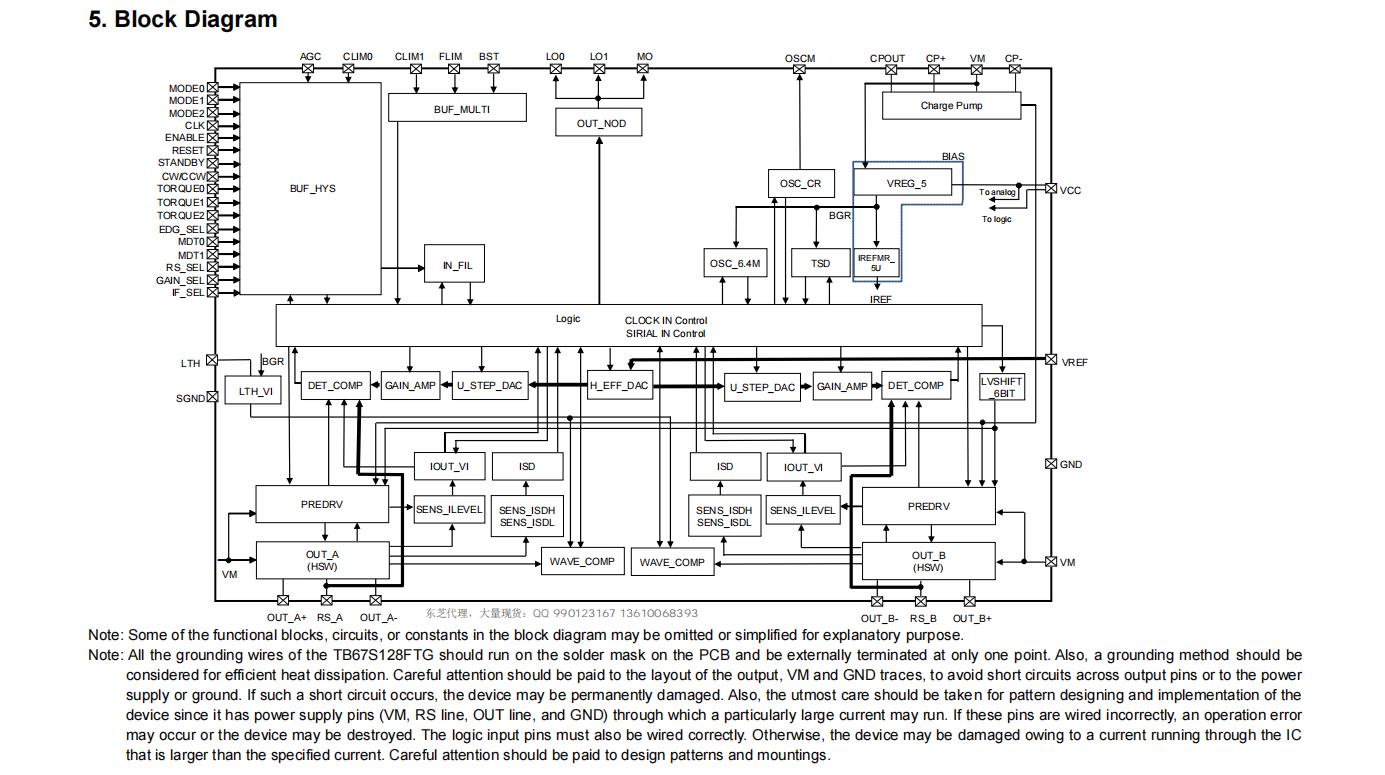

东芝 TB67S128FTG:释放精密电机控制的力量

作为工程师,不断寻求创新解决方案,以提升设计的性能、效率和可靠性。在电机控制领域,精度和效率至关重要。东芝的TB67S128FTG是一款专为先进电机控制应用设计的两相双极步进电机驱动器。让我们

esp32-s2r2芯片无法下载是什么原因导致的?

求助, 我现在遇到esp32-s2r2芯片无法下载问题,一开始怀疑是我电路设计问题。于是我将乐鑫ESP32-S2-WROVER-I模组内ESP32-S2芯片替换为esp32-s2r2芯

发表于 07-01 08:29

HarmonyOS NEXT Developer Beta1最新术语表

模型中代表无界面的Ability,主要为Feature Ability提供支持,例如作为后台服务提供计算能力,或作为数据仓库提供数据访问能力。

S

Service widget,服务卡片

将用

发表于 06-27 16:16

ESP32-S2 FN4R2为什么无法烧录?

我用ESP32-S2FN4R2芯片设计出来的板焊上ESP32-S2FN4R2后烧录不了,已经换过2片芯片了还是烧录不了,不知道是什么原因:IO0上电前已经接地了,IO18上电前也已经上拉10K电阻了

发表于 06-17 08:21

DshanMCU-R128s2术语表

DshanMCU-R128s2术语表

评论