之前给大家介绍过杨百翰大学地球微波遥感实验室(MERS)开发的microSAR,一种小型低成本LFM-CW SAR系统。在这一经验的基础上,BYU与Artemis Inc.合作开发了一个更强力的microASAR,克服了原有设计的许多局限性。

该microASAR设计的一个关键要素是过采样数字接收机。过采样提供了三个主要优点:

信号de-chirped可以在任意中频(IF),从而实现更好的RF滤波;

通过数字滤波降低量化噪声;

SAR能够在de-chirped和脉冲模式下灵活切换。

基于BYU的microSAR系统虽然工作正常,但研究发现由于滤波器的脉冲响应较长,用于抑制馈电数据的High-Q滤波器会引起回波数据的失真。而使用偏置de-chirp可以避免这种失真。我们把这个系统称为偏置IF LFM-CW。

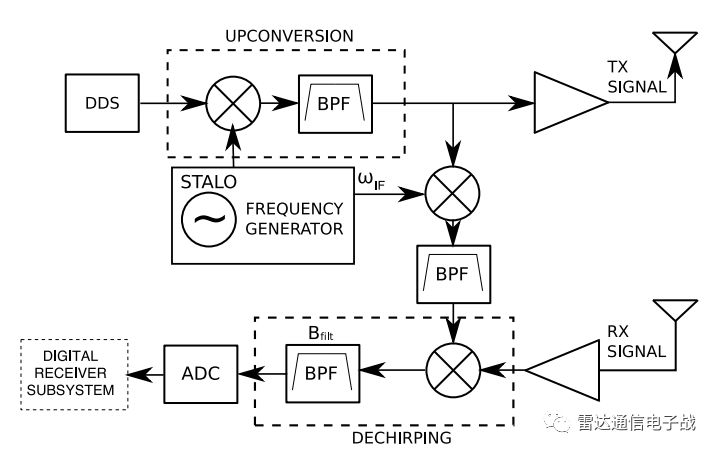

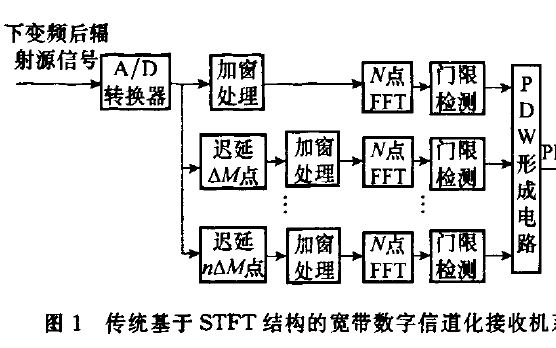

偏置 IF LFM-CW SAR的流程图见图1。首先使用ωIF对发送信号进行部分混频后滤波。然后再与接收到的信号混频,产生的差分分量与传统的LFM-CW中的差分分量相似,但在偏置IF有所不同。有用信号在IF较高的部分,更容易找到High-Q滤波器,使其具有线性相位、锐利截止频率和更好地抑制泄露。

使用一个高速ADC和FPGA就可以实现更高的性能与灵活性。选择一个可以采样接收到的chirp全部带宽的ADC可以实现脉冲模式以及在任意IF的de-chirp操作。FPGA通过提供充足的I/O端口来集成大量组件和通信设备,进一步增强了设计。FPGA提供了灵活的操作模式。

如果忽略相关能量的功耗成本以及ADC分辨率具有可比性,最好以最高速率对接收信号进行采样,能够使得量化噪声减小。因为量化噪声是依据采样频率,以更高的速率采样信号可将噪声谱扩展到更宽的带宽,从而降低信号带宽上的量化噪声功率。

过采样

数字信号处理的过程往往忽视振幅量化的影响,然而在LFM-CW系统中输入信号的量化是噪声的主要来源。一个完全随机的信号在步长q量化时,它相当于在范围内均匀地增加白噪声。通过对信号采样后进行适当的滤波,量化噪声与信号比(QNSR)都降低了约3dB,信号被过采样的因子为2。

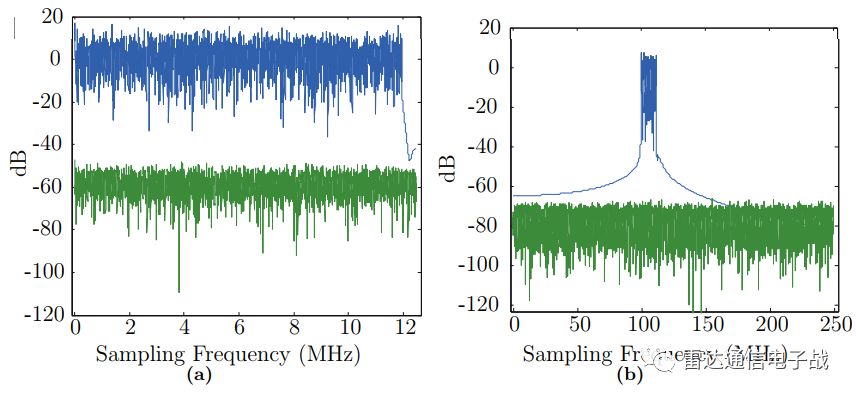

图2 展示了过采样获得的SNR增益。在图2(a)仿真的LFM-CW回波以仅高于Nyquist 的速率进行采样。信号与量化噪声的间隔约为64dB。图2(b)中的信号被过采样因子约为18,比特数与图2(a)相同。信号与量化噪声的间隔则约为75dB。适当的采用带通滤波器,过采样可减少11dB的QNSR。

图 2 用相应的量化噪声来描述子采样(a)和过采样(b)信号的频谱的图。注意:过采样的信号具有较大的信号,与噪声间隔约为11dB;两个图中的信号频谱具有相同的带宽,图形的频率缩放是不同的。

对信号进行采样后,下一步是在不影响数据完整性的情况下降低数据速率(抽取)。此过程中有两个步骤,第一步是滤掉量化噪声,将信号变到基带,以降低滤波后的信号采样频率。所有滤波功能都是采用数字多相滤波器实现,这种滤波器结合了过滤器和解码器的操作, 从而减少了FPGA资源。

降低数据速率的第二步是预加。预加是将顺序的回波加在一起,具有低通滤波多普勒频谱的效果。预加可以用于microASAR数据,因为高PRF可用于分离泄露和第一个目标,PRF远远高于信号的多普勒带宽所要求的水平。

从信号处理的角度来看,预加和滤波的顺序是可改变的。但预加和滤波的顺序极大地影响了实现的内存和硬件要求。还应该注意的是,在每次信号处理操作后,数据的比特宽度都会增加,以防止溢出。

FPGA实现

为使所需系统达到上述的灵活性和高性能,microASAR数字接收机配备了一个12bit 500MHz ADC和一个Xilinx Virtex-5 FX-30T FPGA。这种组合可以使microASAR能对200MHz带宽的发射信号进行完整的采样,并在各种de-chirp模式下工作。本节简要介绍了用于 de-chirp操作的FPGA实现的总体设计,并概述了所使用的设计方略。

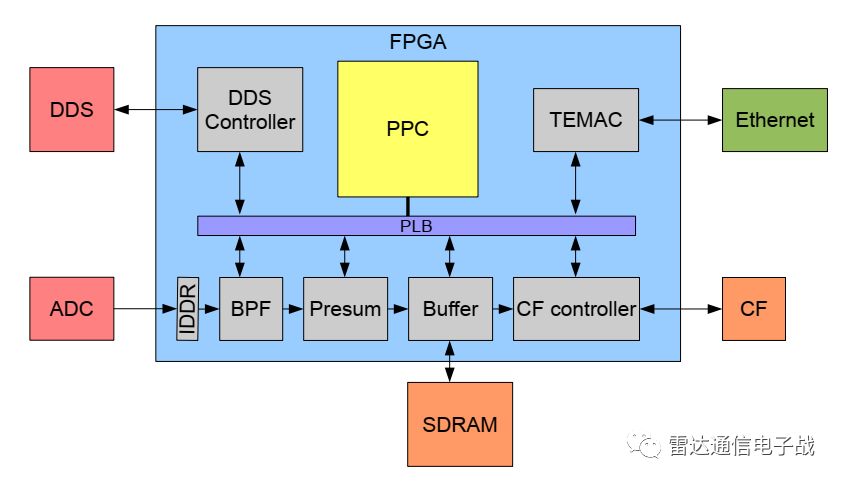

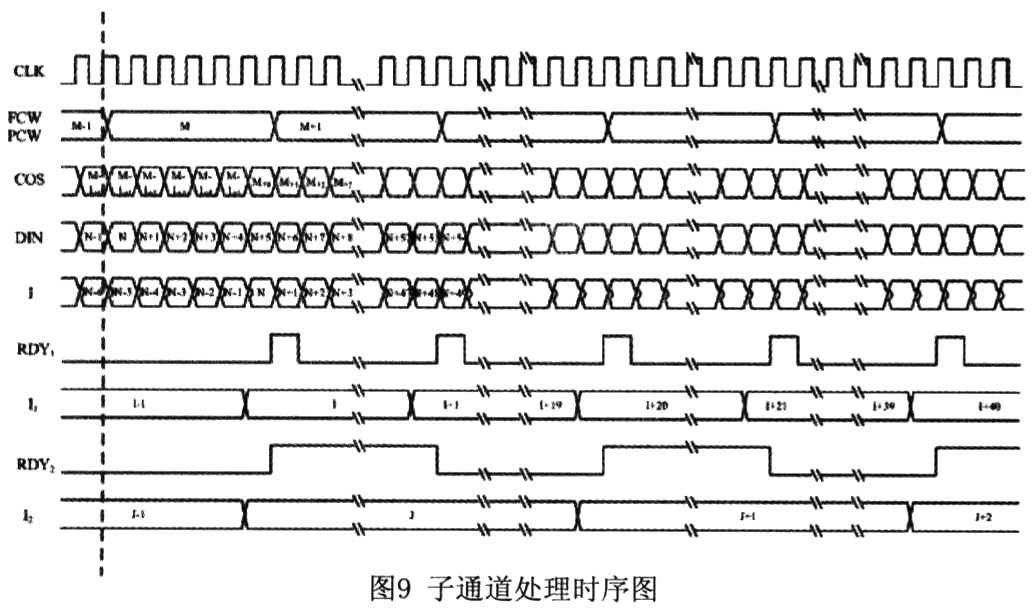

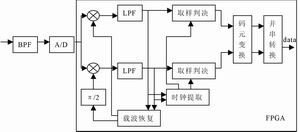

FPGA实现框图如图3 所示。FPGA上的嵌入式PowerPC处理器用于控制和协调完整数字接收机的操作,大多数参数可以通过与powerPC的以太网通信来设置。正常的信号数据路径是从ADC到滤波子系统,然后通过缓存器存入存储卡。

数据路径也可以中断并通过以太网端口传输。ADC中的数据立即被分成两个交错的数据路径,使得滤波器的时钟速率可以减少两倍来缓解时序约束。这两个交错数据流相位差180度,并在之后重组。

这个滤波子系统包括所有的滤波,预加重,抽取步骤,并且能够配置不同的操作参数。滤波子系统由多相滤波器组成,以处理大量的操作并减少FPGA资源。多相滤波器减少量化噪声并限制了信号频谱以便通过抽取数字采样数据将信号转换为DC。

对于microASAR,这是通过采用用12MHz的带通滤波器(BPF),从ωIF开始以20倍抽取,提供约3.3位的分辨率增加。这使信号的有效位数(ENOB)达到16位ADCs,这些ADC通常仅适用于较低的采样率。预加在滤波之后进行,以减少内存要求,从而使假定可以在on-chip memory中计算。

若先执行预加可以减少滤波所需的乘法器。不过,在大多数情况下,这需要外部高速存储,从而增加功耗和开发时间。用多相滤波器替换单相滤波器,后接混频器和多相低通滤波器,可以存储更大的带宽。同样,除了使用混频器和低通滤波器,同样可以使用FFT。这两种方法都需要更多的FPGA资源,并由于定点乘法和查找正余弦表而给信号增加噪声。

这种简洁的设置最大程度地减少了FPGA资源,只需改变PRF即可对各种应用进行操作。降低PRF可以降低调频斜率,压缩de-chirped后的目标。模拟和数字滤波器有效地测量de-chirped数据的门。因此,通过将PRF从7-14kHz改变,SAR可以在5-1000米的高度、30-2500米的幅宽和0-150m/的速度下工作。虽然部分参数在机载作业中无法达到,但microASAR符合地面系统使用条件。

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21734浏览量

603111 -

滤波器

+关注

关注

161文章

7801浏览量

178053 -

数字接收机

+关注

关注

1文章

23浏览量

11637

原文标题:MicroSAR数字接收机的FPGA实现

文章出处:【微信号:雷达通信电子战,微信公众号:雷达通信电子战】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何实现基于多相滤波的数字接收机的FPGA?

基于独立DSP 平台的实时卫星导航接收机的设计实现

DS-SS接收机全数字AGC的FPGA实现

宽带数字接收机的设计实现

DS/FH混合扩频接收机解扩及同步技术的FPGA实现

模块化FPGA设计在某雷达接收机中的应用

宽带数字信道化接收机的FPGA实现

基于多相滤波的数字接收机的FPGA实现

全数字跟踪接收机的设计与实现

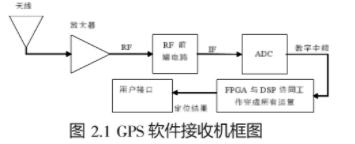

基于FPGA-DSP平台实现GPS卫星导航接收机的设计

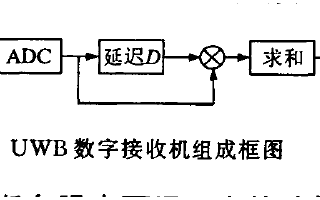

如何使用FPGA实现ADC的TR UWB数字接收机性能

如何使用FPGA实现高效的宽带数字接收机

MicroSAR数字接收机的FPGA实现

MicroSAR数字接收机的FPGA实现

评论