1、function的使用场景

function的作用返回一个数值,此数值由一串组合逻辑代码计算得到。

那为什么要用function呢?主要有两大原因:

a)当组合逻辑实现的功能比较复杂,无法用少量代码完成编写,使用function替代,不用在always块里面写一大堆的组合逻辑,会使得代码逻辑更加清晰,可读性强。

b)当组合逻辑实现的功能在同一个模块内被多次调用,所有使用此功能的代码只需要调用function就可以了,有效减少编码量,而且只需检查function实现功能是否正确,也能够降低错误率,减少bug。

2、Function 规则

a) function结构内不可以使用任何时间控制,例如不可使用#, @, wait等关键字

b) functions 不可以调用task

c) function 至少有一个input申明.

d) function 不能有任何output或者inout申明

e) function 不能使用任何非阻塞赋值(<=)或程序连续赋值(assign and force).

f) function不能使用任何事件触发语句(always@语句)

3、Function使用说明

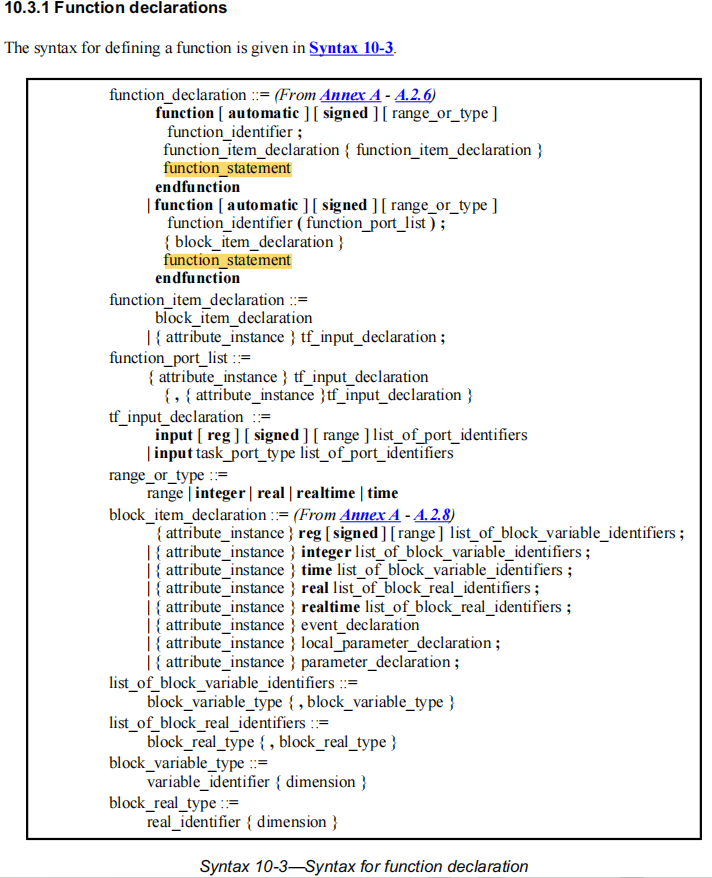

协议中的2种格式

function [ automatic ] [ signed ] [ range_or_type ] function_identifier ; function_item_declaration { function_item_declaration } function_statement endfunction

function [ automatic ] [ signed ] [ range_or_type ] function_identifier ( function_port_list );

{ block_item_declaration }

function_statement

endfunction

可选择的关键字automatic和signed设计人员一般不使用,此处不再描述,请详细描述请见verilog标准(IEEE P1364-2005)

range_or_type指定function返回的数值是real、integer、time、realtime 或者位宽为 [n:m]的数值。

如果range_or_type缺失,则默认function_identifier是1bit的。

function_identifier就是function_name(代表你期望function计算出的结果),function中会隐形地定义一个变量,变量名称就是function_name,最终会把function_statement计算得出的结果赋值给function_name,在调用function_name时,会返回计算结果。

item_declaration是内部变量等的申明,设计中常见为reg [xx:xx] reg_name1; localparameter PARA_NEME ;

integer i;

function_statement 是function实现的逻辑功能,在可综合设计中,就是一串组合逻辑。

两种格式的两个案例:

//第一种格式: function [7:0] getbyte; input [15:0] address; begin // code to extract low-order byte from addressed word . . . getbyte = result_expression; end endfunction //第二种格式:input在括号中 function [7:0] getbyte (input [15:0] address); begin // code to extract low-order byte from addressed word . . . getbyte = result_expression; end endfunction

Verilog标准对function定义的描述:

4、function案例

案例1:格雷码转二进制

wire [ADDR_WIDTH:0] raddr_sync ; wire [ADDR_WIDTH:0] raddr_gray_sync ; //fifo raddr address gray to bin assign raddr_sync = gray2bin(raddr_gray_sync);//fifo raddr address gray to bin function [ADDR_WIDTH:0] gray2bin; //to change the gray code to bin code input [ADDR_WIDTH:0] gray_in; //input gray code reg [ADDR_WIDTH:0] gray_code; //reg gray reg [ADDR_WIDTH:0] bin_code; //bin code result integer i,j; //integer reg tmp; //tmp begin gray_code = gray_in; for(i=0;i<=ADDR_WIDTH;i=i+1) begin tmp=1'b0; for(j=i;j<=ADDR_WIDTH;j=j+1) tmp=gray_code[j]^tmp; bin_code[i]=tmp; end gray2bin= bin_code; end endfunction

案例2--CRC计算

module CRC32_D8(DATA_IN, CLK, RESET, START, LOAD, CRC_IN, CRC_OUT);

input [7:0] DATA_IN;

input CLK;

input RESET;

input START;

input LOAD;

input [31:0] CRC_IN;

output [31:0] CRC_OUT;

reg [31:0] CRC_OUT;

reg start_int;

reg [7:0] data_int;

always @(posedge CLK)

begin

start_int <= START;

data_int <= DATA_IN;

end

always @(posedge CLK or posedge RESET)

begin

if (RESET) begin

CRC_OUT <= 0;

end

else if (start_int == 1) begin

CRC_OUT <= nextCRC32_D8(data_int, CRC_OUT);

end

else if (LOAD == 1) begin

CRC_OUT <= CRC_IN;

end

end

// polynomial: (0 1 2 3 4 5 7 8 10 11 12 16 22 23 26 32)

// data width: 8

// convention: the first serial data bit is D[7]

function [31:0] nextCRC32_D8;

input [7:0] Data;

input [31:0] CRC;

reg [7:0] D;

reg [31:0] C;

reg [31:0] NewCRC;

begin

D = Data;

C = CRC;

NewCRC[0] = D[6] ^ D[0] ^ C[24] ^ C[30];

NewCRC[1] = D[7] ^ D[6] ^ D[1] ^ D[0] ^ C[24] ^ C[25] ^ C[30] ^

C[31];

NewCRC[2] = D[7] ^ D[6] ^ D[2] ^ D[1] ^ D[0] ^ C[24] ^ C[25] ^

C[26] ^ C[30] ^ C[31];

NewCRC[3] = D[7] ^ D[6] ^ D[3] ^ D[2] ^ D[1] ^ D[0] ^ C[24] ^ C[25] ^

C[26] ^ C[27] ^ C[30] ^ C[31];

NewCRC[4] = D[7] ^ D[6] ^ D[4] ^ D[3] ^ D[2] ^ D[1] ^ D[0] ^ C[24] ^

C[25] ^ C[26] ^ C[27] ^ C[28] ^ C[30] ^ C[31];

NewCRC[5] = D[7] ^ D[6] ^ D[5] ^ D[4] ^ D[3] ^ D[2] ^ D[1] ^ D[0] ^

C[24] ^ C[25] ^ C[26] ^ C[27] ^ C[28] ^ C[29] ^ C[30] ^

C[31];

NewCRC[6] = D[7] ^ D[6] ^ D[5] ^ D[4] ^ D[3] ^ D[2] ^ D[1] ^ C[25] ^

C[26] ^ C[27] ^ C[28] ^ C[29] ^ C[30] ^ C[31];

NewCRC[7] = D[7] ^ D[5] ^ D[4] ^ D[3] ^ D[2] ^ D[0] ^ C[24] ^ C[26] ^

C[27] ^ C[28] ^ C[29] ^ C[31];

NewCRC[8] = D[5] ^ D[4] ^ D[3] ^ D[1] ^ D[0] ^ C[0] ^ C[24] ^ C[25] ^

C[27] ^ C[28] ^ C[29];

NewCRC[9] = D[6] ^ D[5] ^ D[4] ^ D[2] ^ D[1] ^ C[1] ^ C[25] ^ C[26] ^

C[28] ^ C[29] ^ C[30];

NewCRC[10] = D[7] ^ D[5] ^ D[3] ^ D[2] ^ D[0] ^ C[2] ^ C[24] ^ C[26] ^

C[27] ^ C[29] ^ C[31];

NewCRC[11] = D[4] ^ D[3] ^ D[1] ^ D[0] ^ C[3] ^ C[24] ^ C[25] ^

C[27] ^ C[28];

NewCRC[12] = D[6] ^ D[5] ^ D[4] ^ D[2] ^ D[1] ^ D[0] ^ C[4] ^ C[24] ^

C[25] ^ C[26] ^ C[28] ^ C[29] ^ C[30];

NewCRC[13] = D[7] ^ D[6] ^ D[5] ^ D[3] ^ D[2] ^ D[1] ^ C[5] ^ C[25] ^

C[26] ^ C[27] ^ C[29] ^ C[30] ^ C[31];

NewCRC[14] = D[7] ^ D[6] ^ D[4] ^ D[3] ^ D[2] ^ C[6] ^ C[26] ^ C[27] ^

C[28] ^ C[30] ^ C[31];

NewCRC[15] = D[7] ^ D[5] ^ D[4] ^ D[3] ^ C[7] ^ C[27] ^ C[28] ^

C[29] ^ C[31];

NewCRC[16] = D[5] ^ D[4] ^ D[0] ^ C[8] ^ C[24] ^ C[28] ^ C[29];

NewCRC[17] = D[6] ^ D[5] ^ D[1] ^ C[9] ^ C[25] ^ C[29] ^ C[30];

NewCRC[18] = D[7] ^ D[6] ^ D[2] ^ C[10] ^ C[26] ^ C[30] ^ C[31];

NewCRC[19] = D[7] ^ D[3] ^ C[11] ^ C[27] ^ C[31];

NewCRC[20] = D[4] ^ C[12] ^ C[28];

NewCRC[21] = D[5] ^ C[13] ^ C[29];

NewCRC[22] = D[0] ^ C[14] ^ C[24];

NewCRC[23] = D[6] ^ D[1] ^ D[0] ^ C[15] ^ C[24] ^ C[25] ^ C[30];

NewCRC[24] = D[7] ^ D[2] ^ D[1] ^ C[16] ^ C[25] ^ C[26] ^ C[31];

NewCRC[25] = D[3] ^ D[2] ^ C[17] ^ C[26] ^ C[27];

NewCRC[26] = D[6] ^ D[4] ^ D[3] ^ D[0] ^ C[18] ^ C[24] ^ C[27] ^

C[28] ^ C[30];

NewCRC[27] = D[7] ^ D[5] ^ D[4] ^ D[1] ^ C[19] ^ C[25] ^ C[28] ^

C[29] ^ C[31];

NewCRC[28] = D[6] ^ D[5] ^ D[2] ^ C[20] ^ C[26] ^ C[29] ^ C[30];

NewCRC[29] = D[7] ^ D[6] ^ D[3] ^ C[21] ^ C[27] ^ C[30] ^ C[31];

NewCRC[30] = D[7] ^ D[4] ^ C[22] ^ C[28] ^ C[31];

NewCRC[31] = D[5] ^ C[23] ^ C[29];

nextCRC32_D8 = NewCRC;

end

endfunction

案例3-输入数据datain中bit 1的数量大于2,则返回XBC为1

module functionCall(XBC, DataIn);

output XBC;

input [0:5] DataIn;

function [0:2] CountOnes;

input [0:5]A;

integer K;

begin

CountOnes =0;

for(X=0;R<=5;K=X+1)

if(A[K])

CountOnes = Countones +1;

end

endfunction

// If number of ones in DataIn is greater than 2, return 1 in XBC.

aasigm XBC = CountOnes (DataIn)>2;

endmodule

审核编辑:刘清

-

二进制

+关注

关注

2文章

801浏览量

41802 -

Verilog

+关注

关注

28文章

1355浏览量

110590 -

CRC校验

+关注

关注

0文章

84浏览量

15296

原文标题:verilog语法-使用function提高效率

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

明德扬视频分享点拨FPGA课程--第二十章 提高效率技巧

如何使用UCC28056优化过渡模式PFC设计来提高效率和待机功耗?

keil5提高效率的技巧

卡套管的使用有助于提高效率并达到更合格的标准

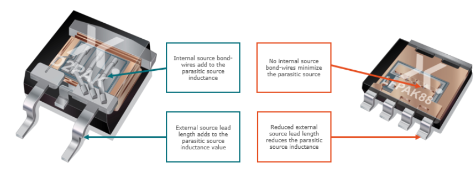

LFPAK88是提高效率的捷径

NIKKEI逻辑整合Brocade SAN以提高效率和安全性

提高效率的DC电源模块设计技巧

verilog语法-如何使用function提高效率?

verilog语法-如何使用function提高效率?

评论