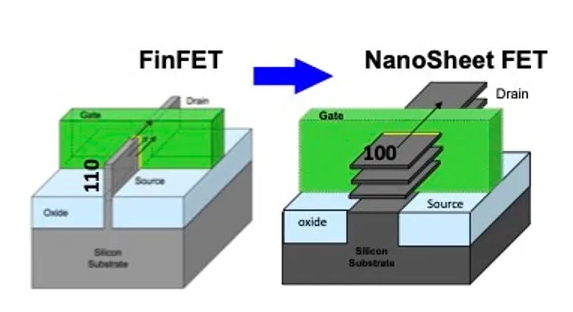

在经历了近十年和五个主要节点以及一系列半节点之后,半导体制造业将开始从 FinFET过渡到3nm技术节点上的全栅堆叠纳米片晶体管架构。

相对于FinFET,纳米片晶体管通过在相同的电路占位面积中增加沟道宽度来提供更多的驱动电流(图1),其环栅设计改善了通道控制并较大限度地减少了短通道效应。

图1:在纳米片晶体管中,栅极在所有侧面接触沟道,可实现比finFET更高的驱动电流

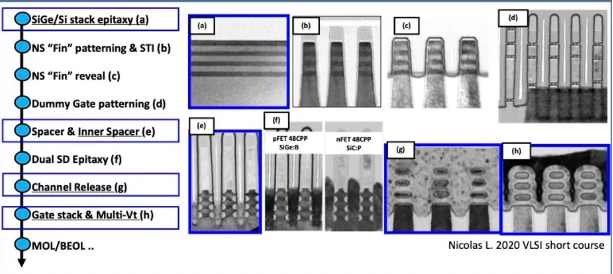

图1:在纳米片晶体管中,栅极在所有侧面接触沟道,可实现比finFET更高的驱动电流从表面上看,纳米片晶体管类似于FinFET,但纳米片通道与基板平行排列,而不是垂直排列。纳米片晶体管制造从沉积Si/SiGe异质结构开始,与衬底隔离以防止寄生传导。

在伪栅极制造之后,内部间隔物蚀刻步骤在SiGe层中切割凹槽。内部间隔蚀刻步骤是一个关键的工艺步骤,因为它定义了栅极长度和源/漏结重叠。

构建晶体管支柱

即使SiGe层不是成品器件的一部分,但它们的锗浓度仍然是一个重要的工艺变量,增加锗的量会增加SiGe晶格常数,这反过来又会增加硅层中的晶格应变,从而引入缺陷。另一方面,如果我们要在不损坏或侵蚀硅的情况下完全去除SiGe材料,则需要具有高SiGe:Si选择性的蚀刻工艺。

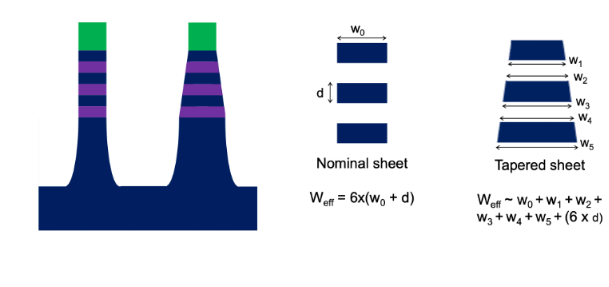

在理想情况下,英思特公司希望尽可能小化纳米片之间的间距从而减少寄生电容。因为一旦SiGe消失,纳米片之间的空间则需要容纳更多的残留物。在Si/SiGe异质结构沉积之后,各向异性蚀刻需要切割到所需宽度的柱体。

图2:蚀刻轮廓直接影响晶体管行为和器件操作的一致性定义通道

图2:蚀刻轮廓直接影响晶体管行为和器件操作的一致性定义通道定义通道

一旦纳米片柱被定义,高选择性各向同性蚀刻就会创建内部间隔凹陷,这个间隔物定义了栅极长度和结重叠,这两者都是关键的晶体管参数,有助于定义器件电阻和电容之间的权衡。湿化学蚀刻工艺往往会留下半月形轮廓,因为两个相邻的纳米片之间会形成弯月面。在沟道释放蚀刻期间去除剩余的SiGe可以暴露源极/漏极,并将它们与栅极金属直接接触。

图3:纳米片晶体管工艺流程中的关键蚀刻步骤

图3:纳米片晶体管工艺流程中的关键蚀刻步骤

虽然干法蚀刻工艺没有留下半月板,但英思特公司仍然观察到圆形蚀刻前端,并确定了其Si/SiGe柱侧壁上的富锗层。该层显然是在各向异性柱蚀刻期间形成的,其蚀刻速度更快,导致圆形蚀刻前端。

审核编辑 黄宇

-

晶体管

+关注

关注

78文章

10458浏览量

148867 -

蚀刻

+关注

关注

10文章

431浏览量

16700

发布评论请先 登录

华为IPv6+如何驱动下一代IP网络演进

FT 5000 Smart Transceiver:下一代智能网络芯片的卓越之选

DirectScan 技术解析:下一代半导体电子束检测的创新路径与应用

DSP Concepts与AMD助力打造下一代汽车音频

理想汽车发布下一代自动驾驶基础模型MindVLA-o1

Altera携手生态伙伴推动下一代先进无线电系统发展

英飞凌下一代电磁阀驱动器评估套件使用指南

Amphenol Aerospace高压38999连接器:满足下一代飞机电力需求

Telechips与Arm合作开发下一代IVI芯片Dolphin7

用于下一代 GGE 和 HSPA 手机的多模式/多频段功率放大器模块 skyworksinc

适用于下一代 GGE 和 HSPA 手机的多模/多频段 PAM skyworksinc

下一代晶体管有何不同

下一代晶体管有何不同

评论