4H-SiC概述(生长、特性、应用)、Bulk及外延层缺陷、光致发光/拉曼光谱法/DLTS/μ-PCD/KOH熔融/光学显微镜,TEM,SEM/散射光等表征方法。

报告详细内容

■ 介绍

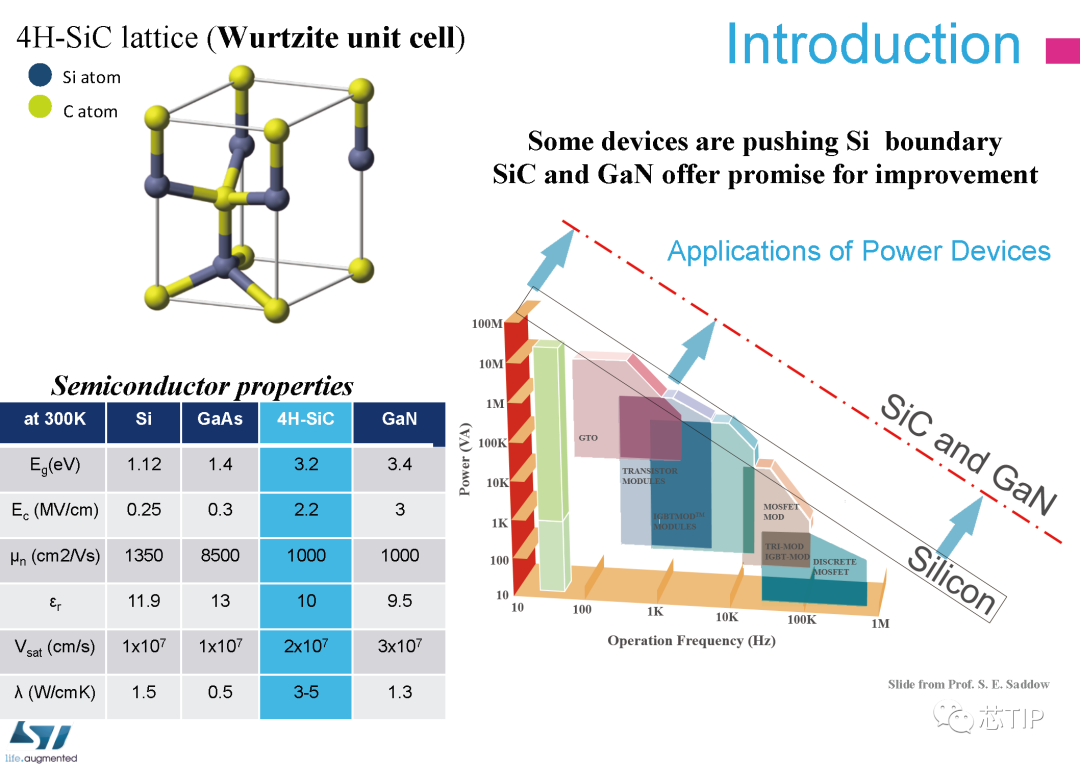

• 一些器件正在突破Si的界限,SiC和GaN提供了改进的希望。

■ 介绍

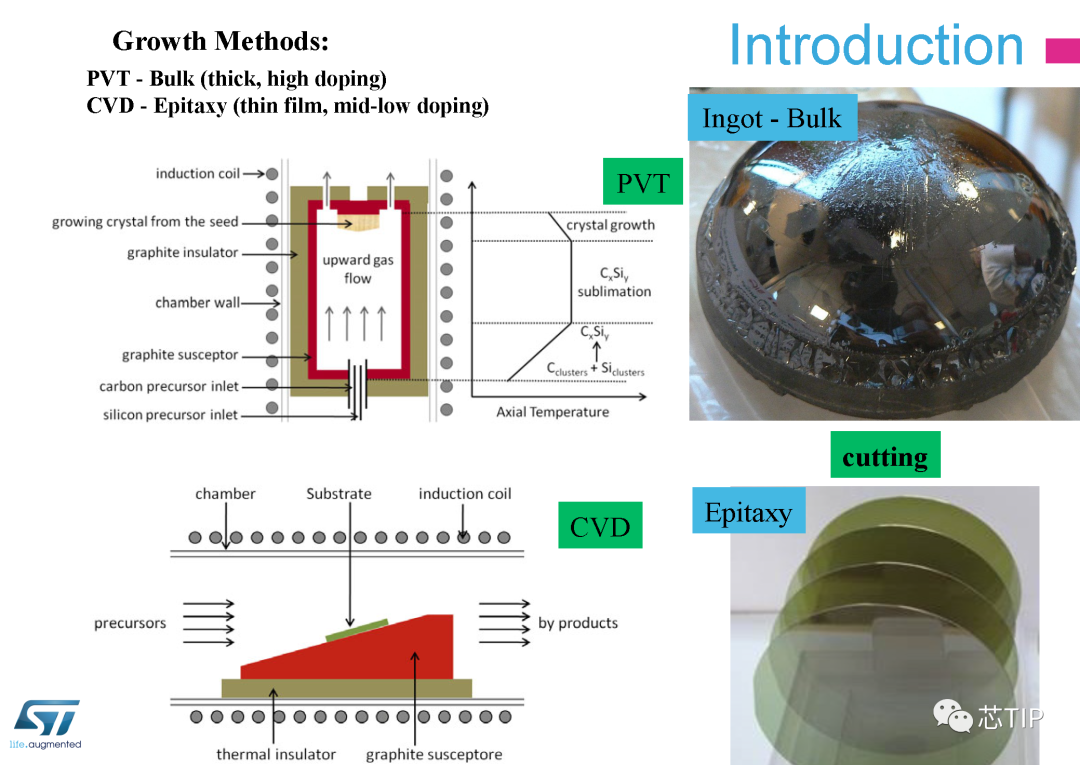

• 生长方法:

PVT - 块体(厚、高掺杂)

CVD - 外延(薄膜,中低掺杂)

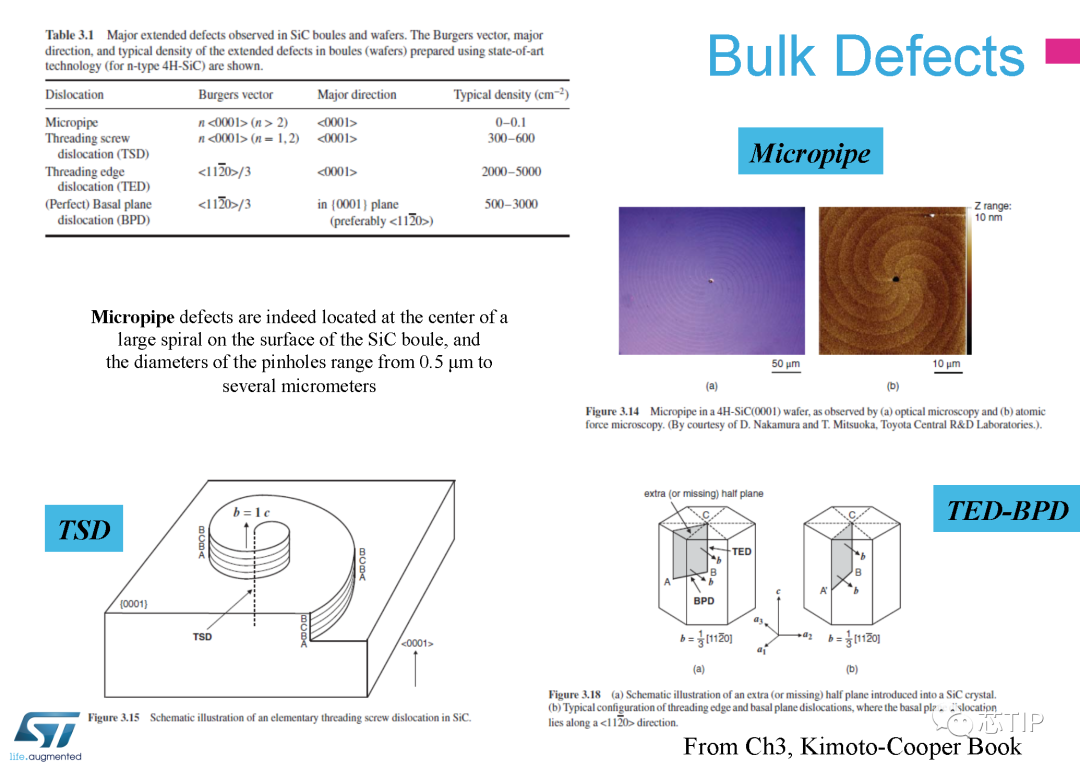

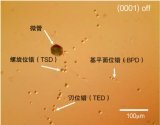

■ Bulk缺陷

• 微管

微管缺陷确实位于SiC晶锭表面一个大螺旋的中心,针孔的直径从0.5微米到几微米不等

• TSD

• TED-BPD

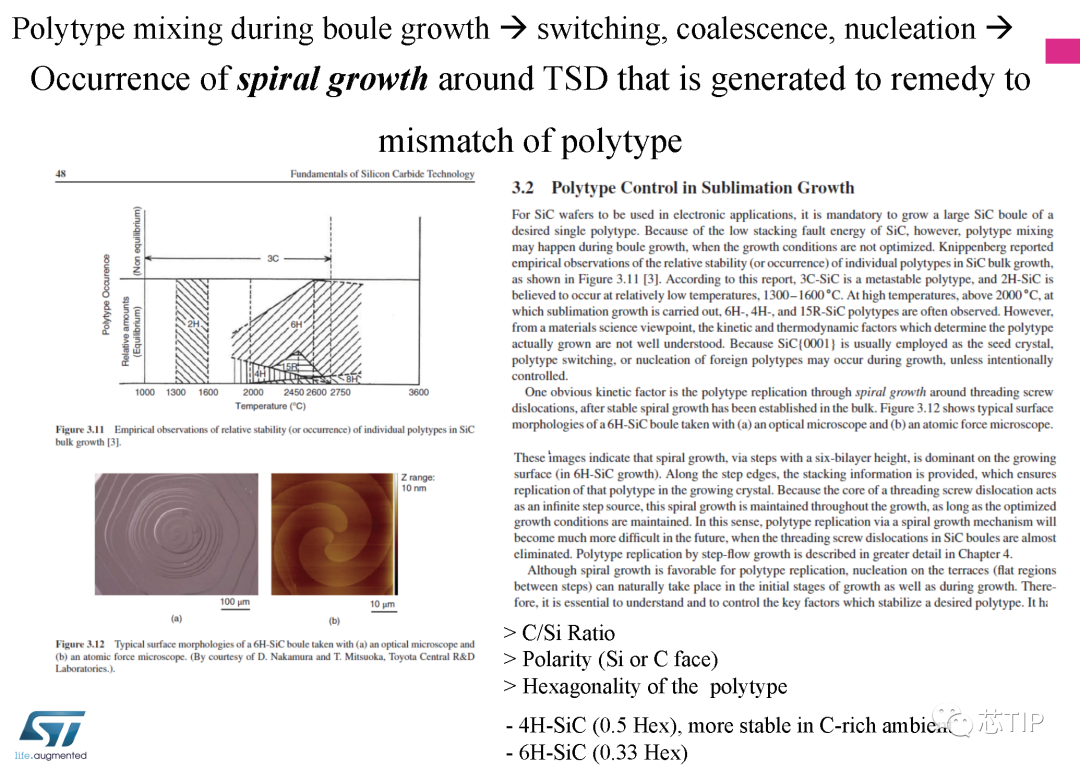

■ 升华生长的多型控制

• 晶锭生长过程中的多型体混合——转换、聚结、成核——在TSD周围发生螺旋生长,以弥补多型体的不匹配

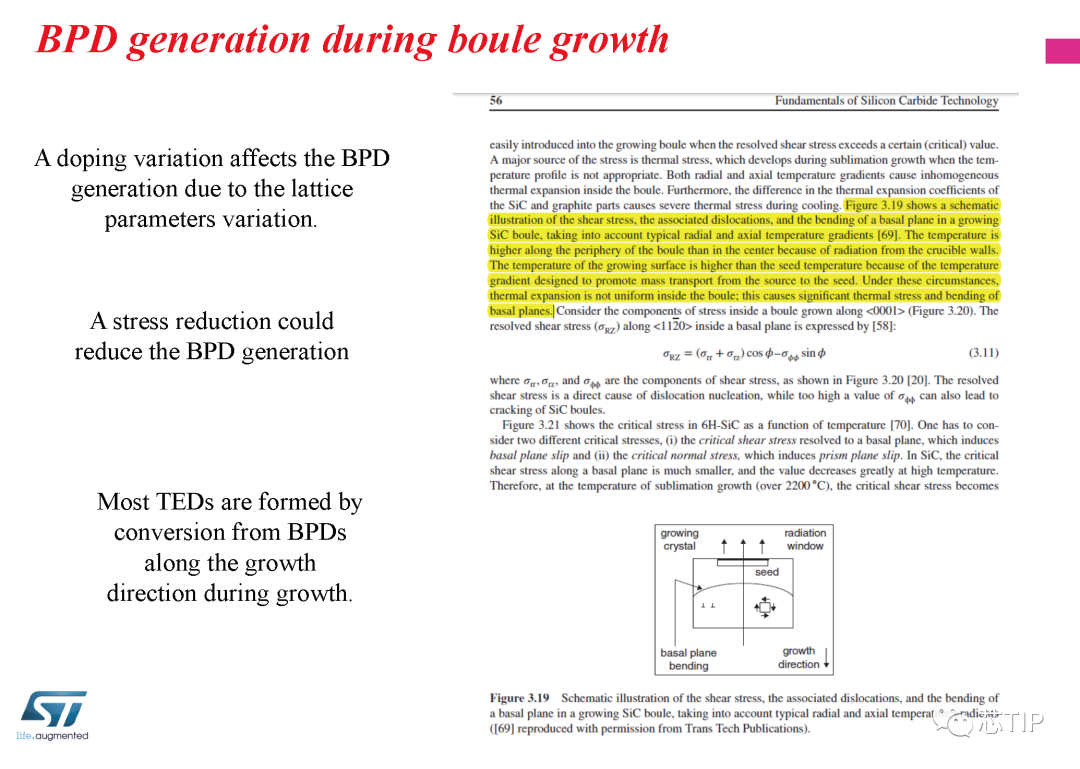

■ 晶锭生长过程中的 BPD 生成

• 由于晶格参数的变化,掺杂物的变化会影响BPD的产生

• 减少应力可以减少BPD的产生

• 大多数TED是由生长过程中沿生长方向的BPD转化而形成的

■ TSD的产生和消除

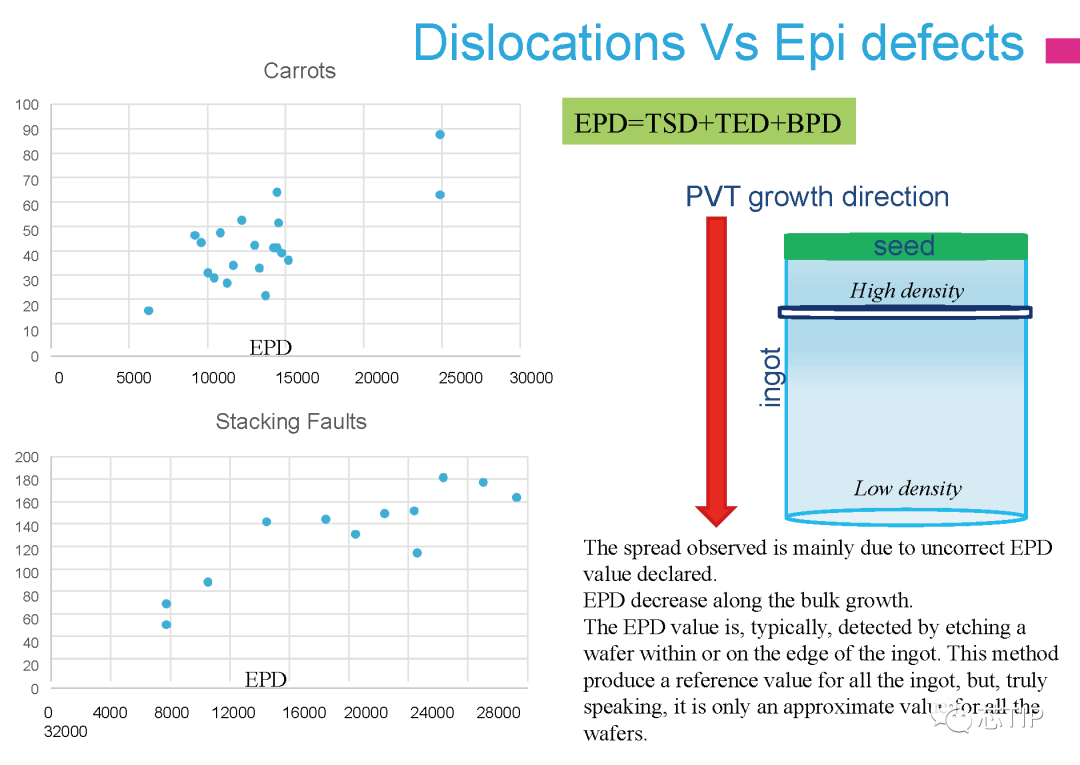

• EPD = TSD+TED+BPD

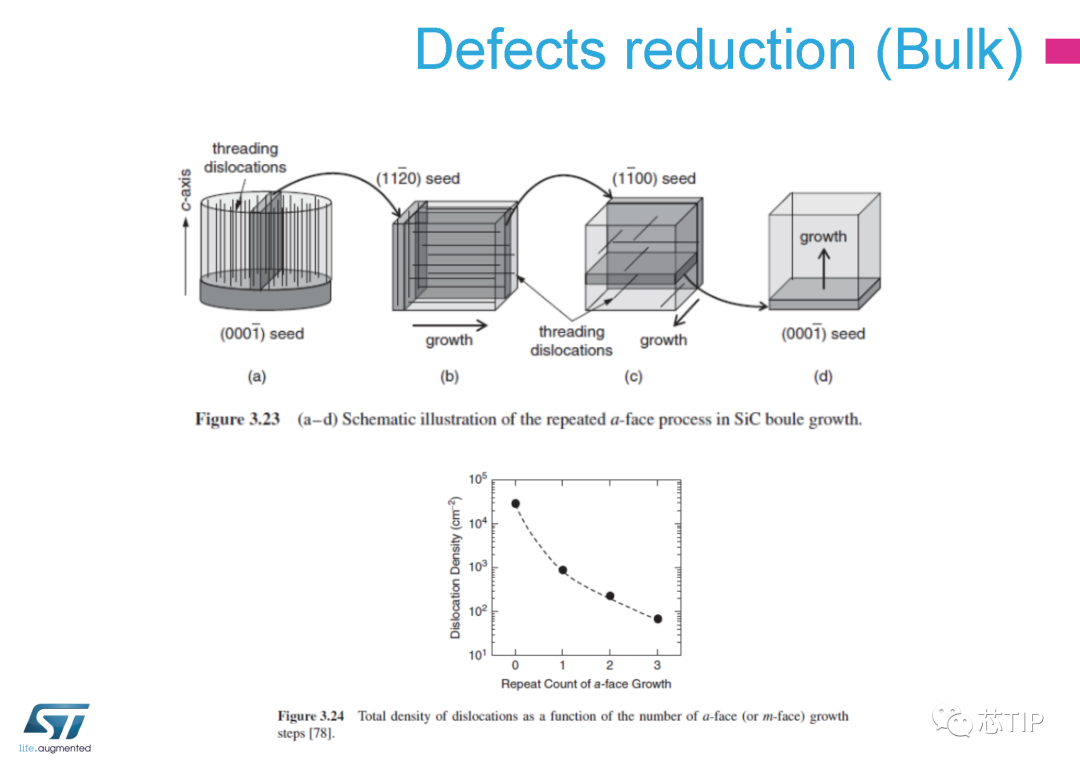

■ 减少缺陷(Bulk)

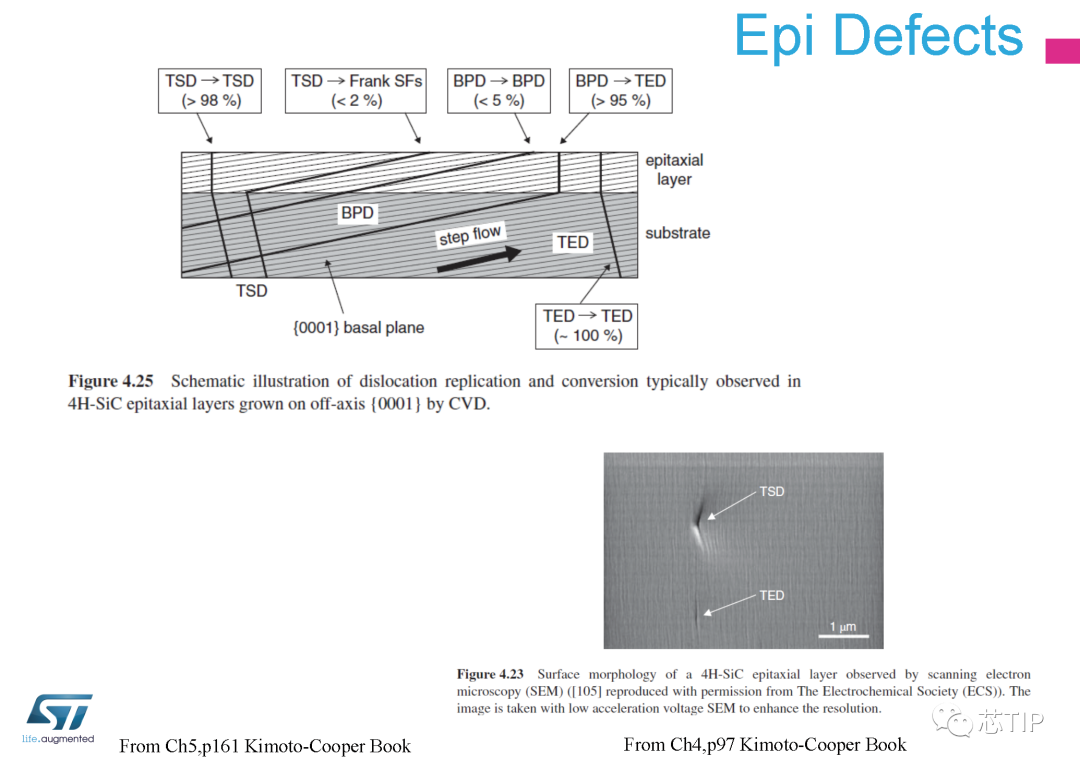

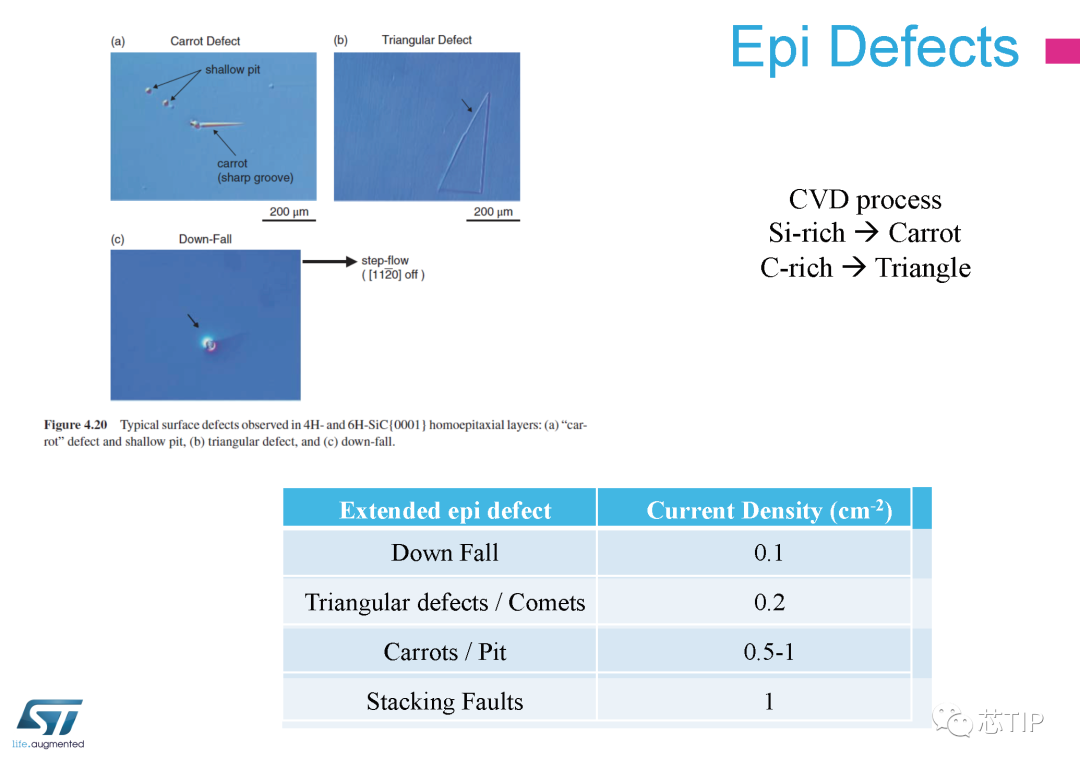

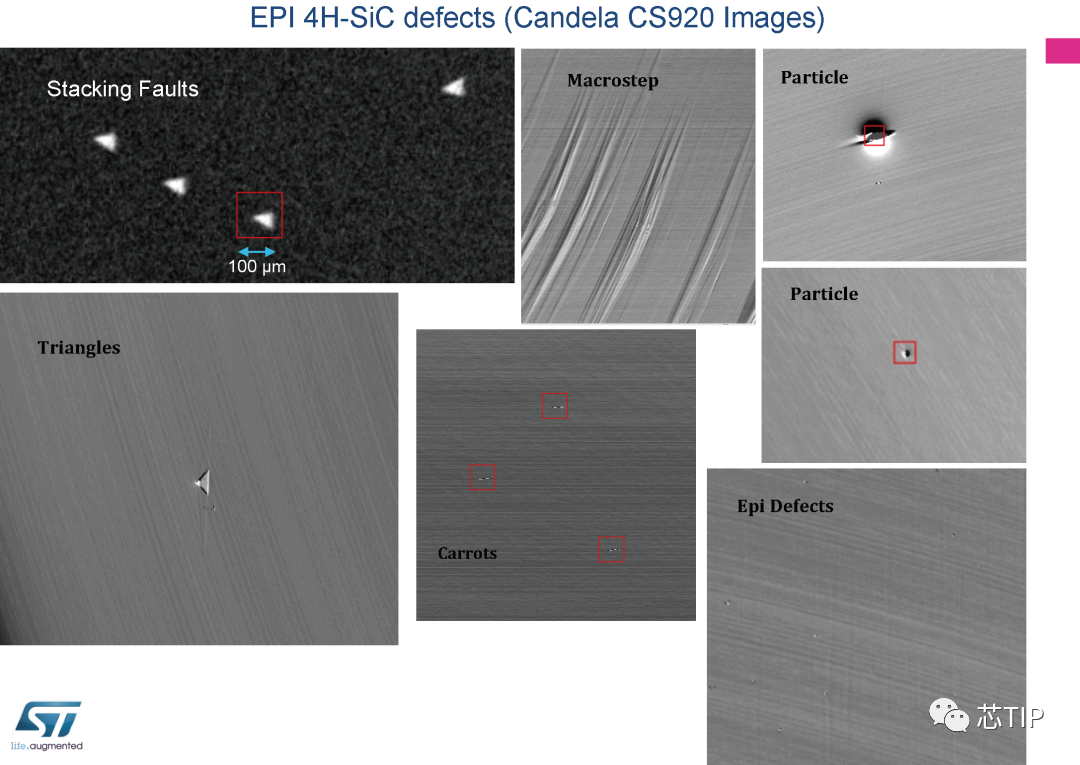

■ 外延缺陷

■ 外延缺陷

• 化学气相沉积工艺

富Si——胡萝卜缺陷

富C——三角缺陷

■ 位错与外延缺陷

• EPD随体量增长而减少

• EPD 值通常通过在晶锭内部或边缘上蚀刻晶片来检测。

• 这种方法对所有的晶锭产生了一个参考值,但实际上,它只是对所有晶片的一个近似值

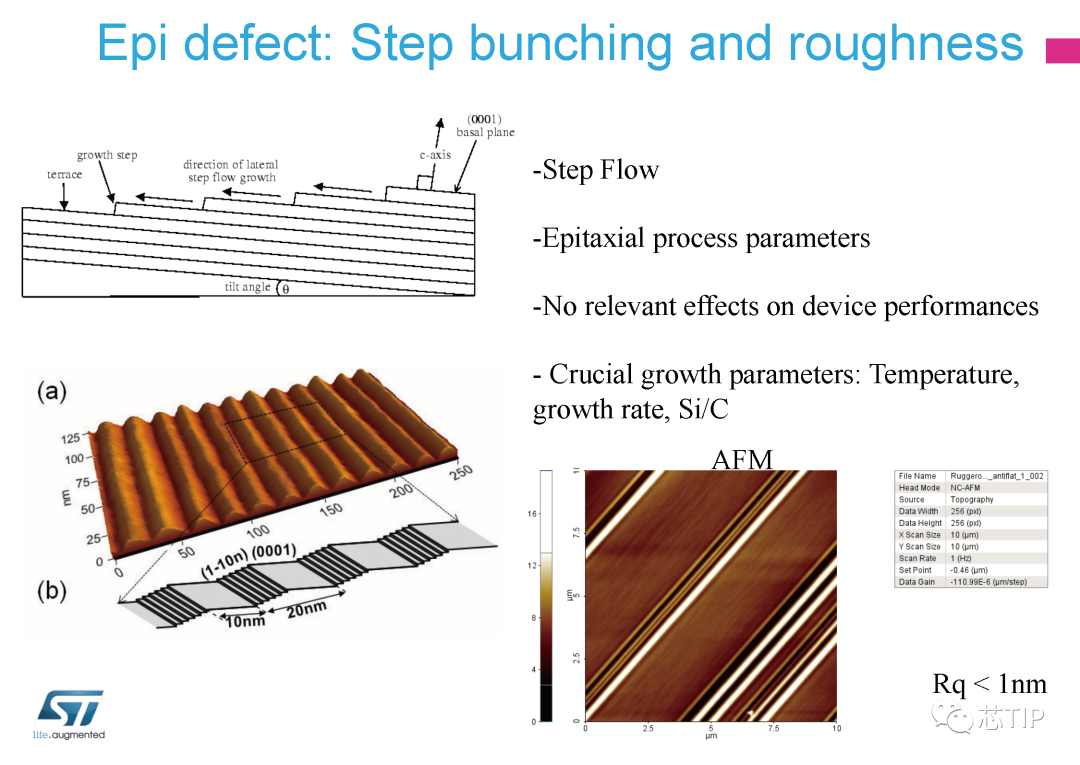

■ 外延缺陷:台阶聚集和粗糙度

• 外延工艺参数

• 对设备性能没有相关影响

• 关键生长参数:温度、生长速率、Si/C

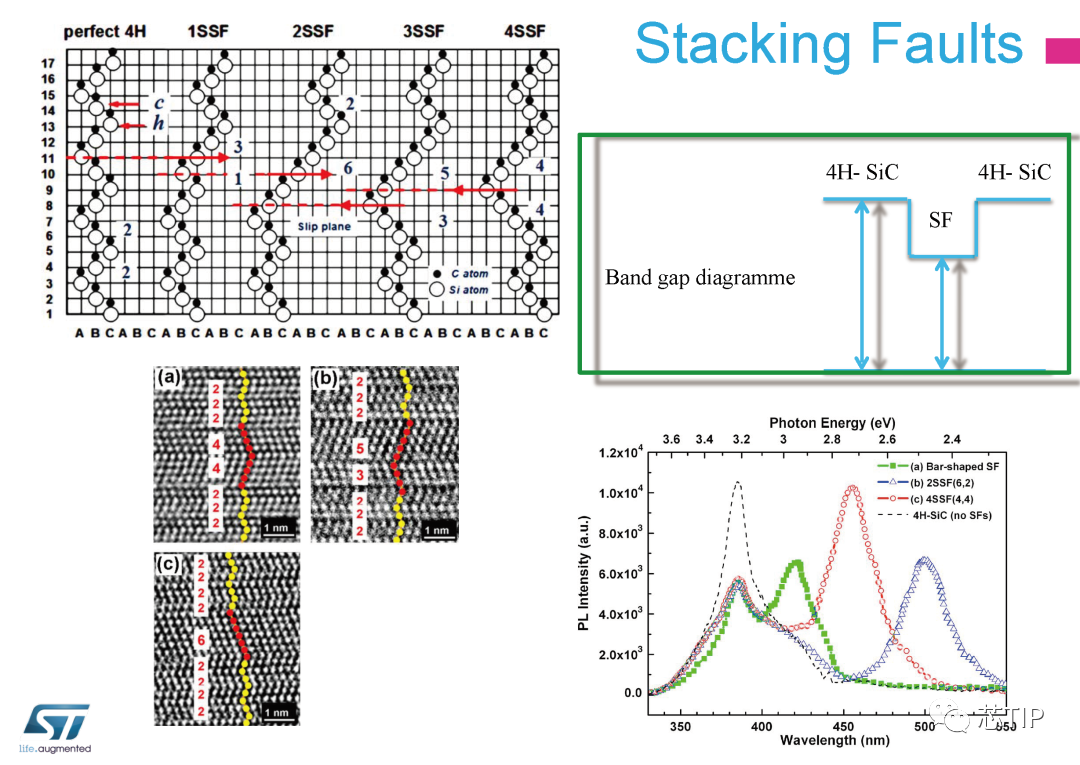

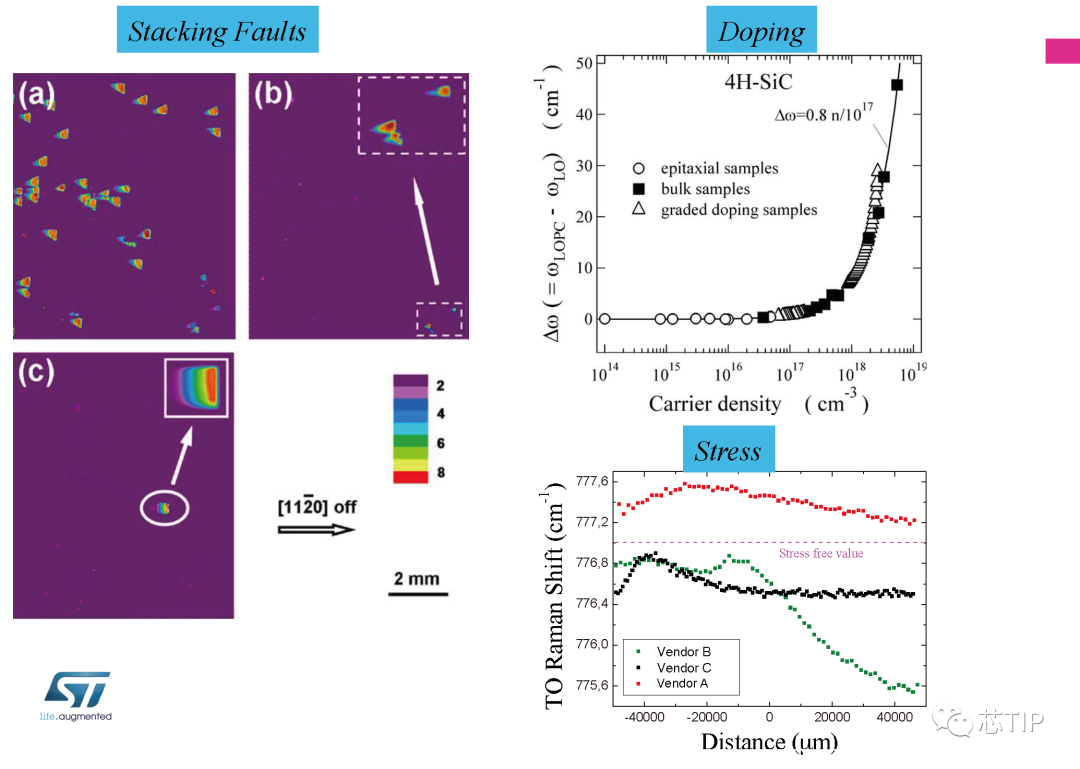

■ 堆垛层错

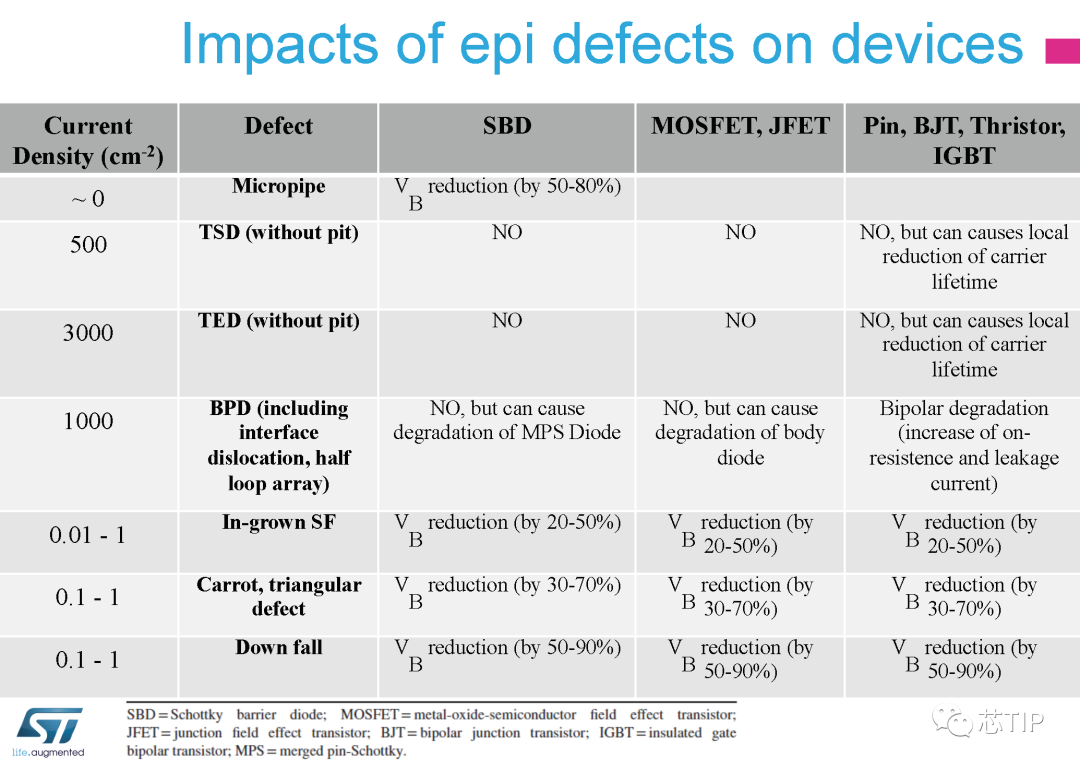

■ 外延缺陷对器件的影响

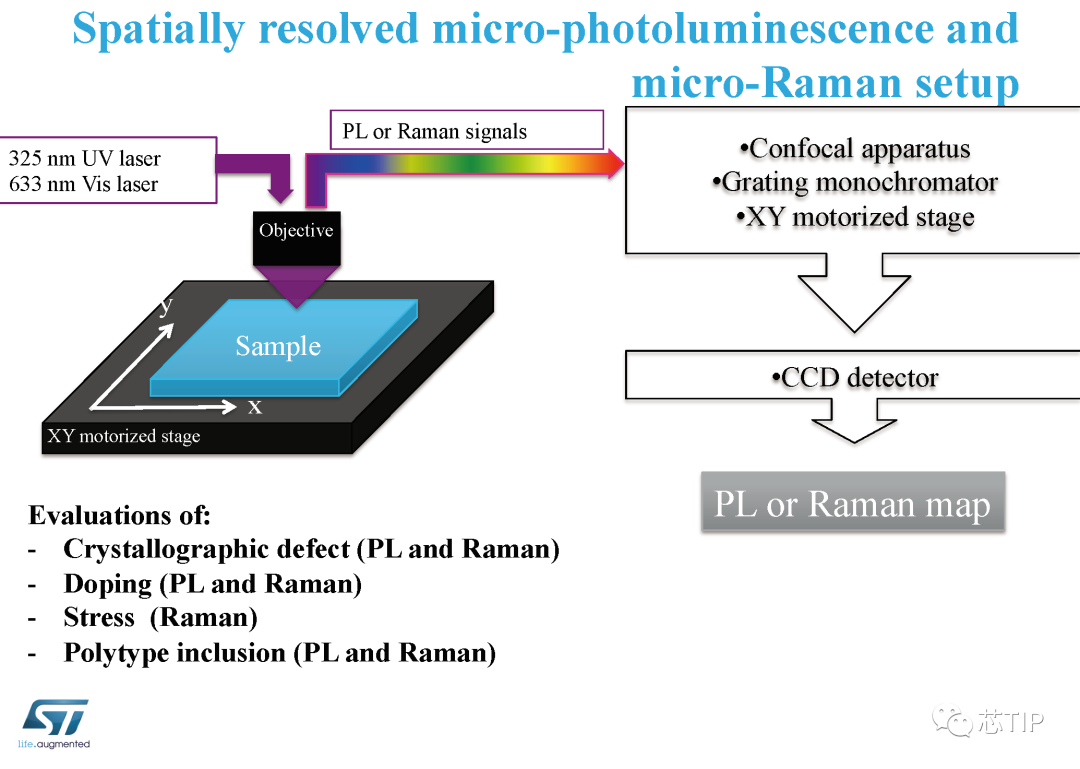

■ 微型光致发光和微型拉曼设置

• 晶体缺陷(PL 和拉曼)

• 掺杂(PL 和拉曼)

• 应力(拉曼)

• 多型夹杂物(PL 和拉曼)

■ 堆垛层错/掺杂/应力

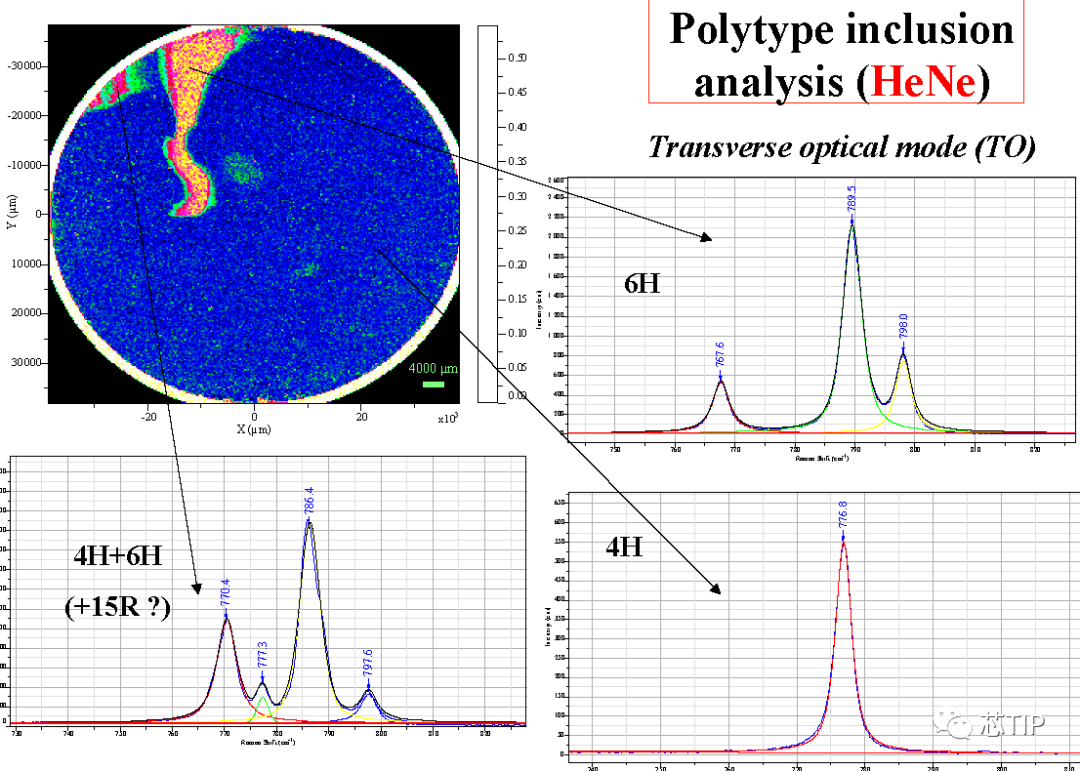

■ 多型夹杂物分析 (HeNe)

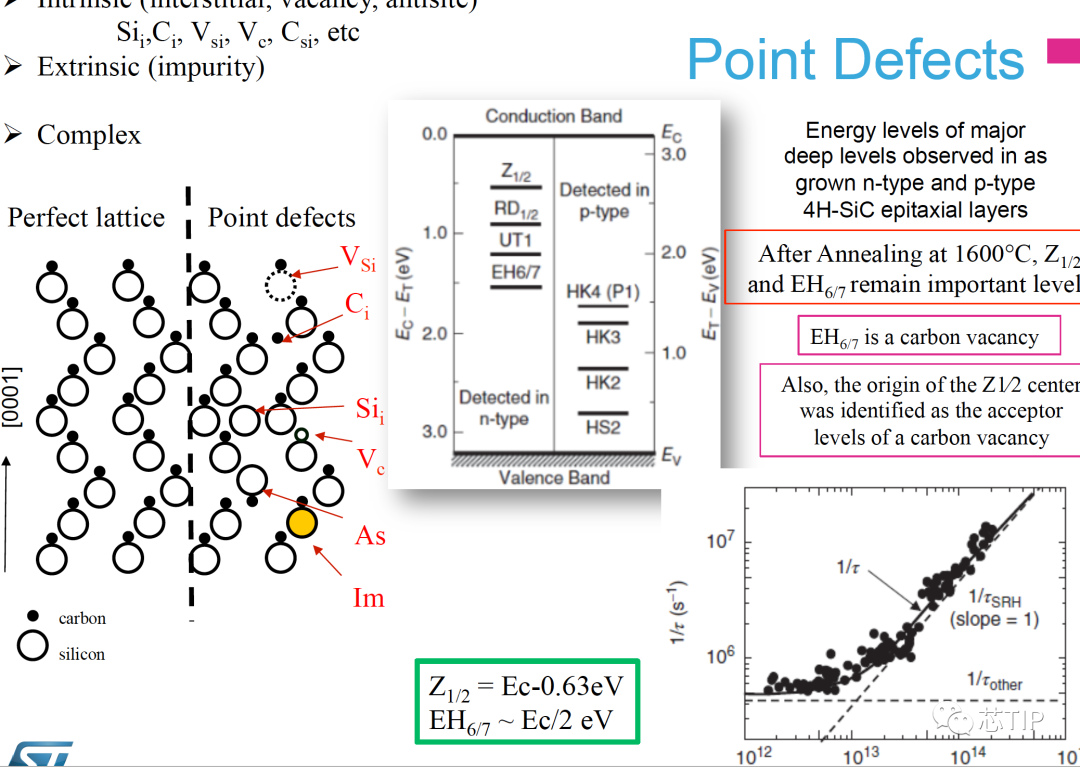

■ 点缺陷

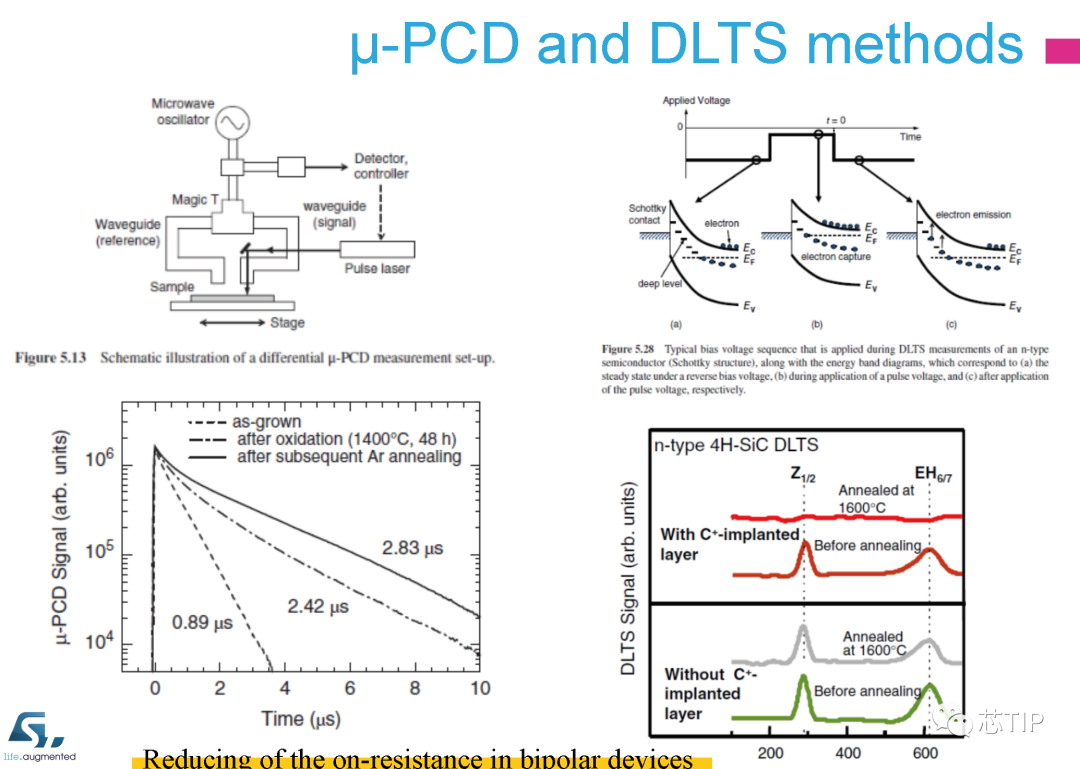

■ μ-PCD 和 DLTS 方法

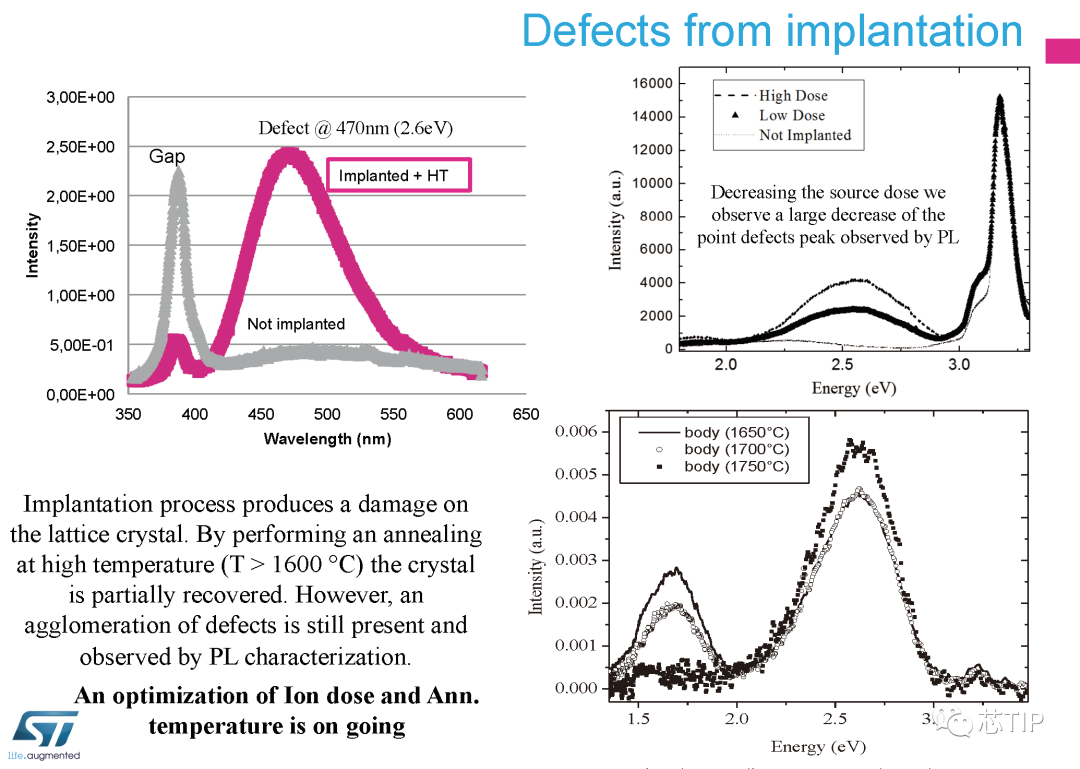

■ 离子注入致缺陷

• 离子注入过程对晶格产生损伤

• 通过在高温 (T > 1600 °C) 下进行退火,晶体被部分回收

• 然而,缺陷的聚集仍然存在并通过 PL 表征观察到

• 正在对离子剂量和退火温度进行优化

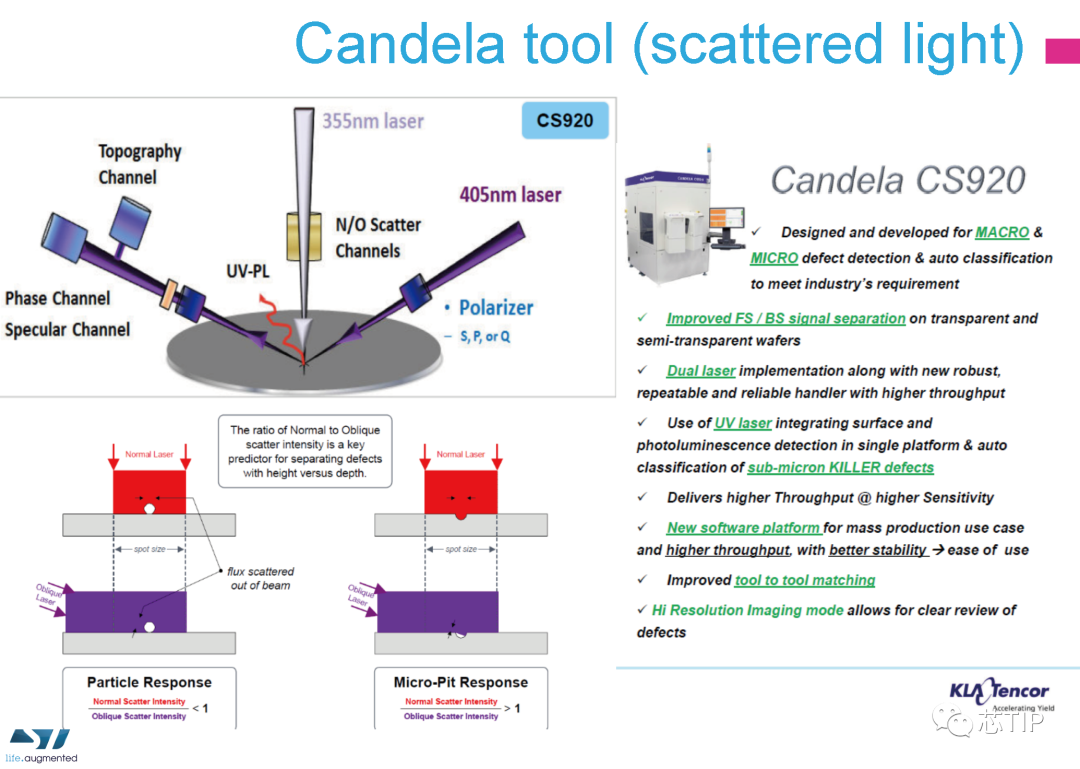

■ 坎德拉工具(散射光)

■ 总结

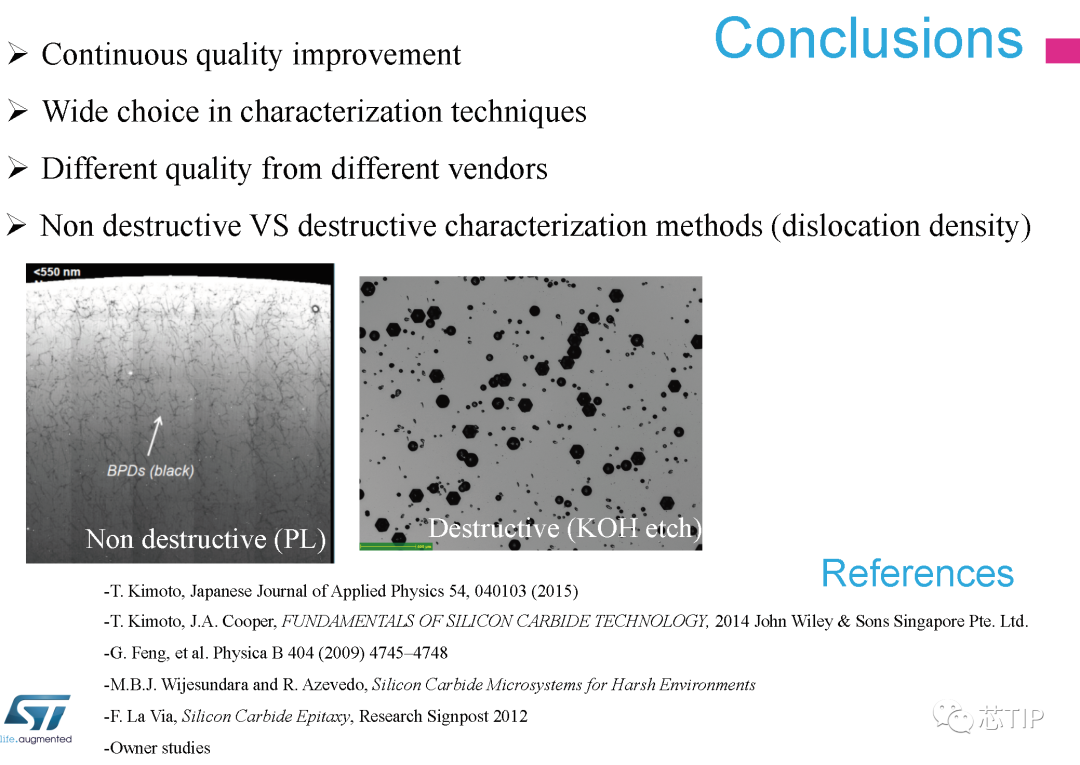

• 持续的质量改进

• 表征技术的广泛选择

• 来自不同供应商的不同质量

• 非破坏性 VS 破坏性表征方法(位错密度)

审核编辑:刘清

-

SEM

+关注

关注

0文章

237浏览量

14526 -

SiC

+关注

关注

30文章

2915浏览量

63064 -

TEM

+关注

关注

0文章

90浏览量

10479 -

拉曼光谱

+关注

关注

0文章

86浏览量

2787

原文标题:「芯报告」4H-SiC缺陷(cr.意法半导体)

文章出处:【微信号:CloudBrain-TT,微信公众号:云脑智库】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

改善4H-SiC晶圆表面缺陷的高压碳化硅解决方案

SiC功率器件性能和可靠性的提升

4H-SiC离子注入层的欧姆接触的制备

SiC器件中SiC材料的物性和特征,功率器件的特征,SiC MOSFET特征概述

基于简单的支架多片4H-SiC化学气相沉积同质外延生长

8英寸导电型4H-SiC单晶衬底制备与表征

天科合达谈八英寸SiC

SiC的物性和特征

如何降低SiC/SiO₂界面缺陷

国产CVD设备在4H-SiC衬底上的同质外延实验

控制多晶硅(poly-Si)/4H-SiC异质结二极管能垒高度(ΦB)的方法

合盛新材料8英寸导电型4H-SiC衬底项目全线贯通

磨料形貌及分散介质对4H碳化硅晶片研磨质量有哪些影响

4H-SiC缺陷概述

4H-SiC缺陷概述

评论