近日,翼辉信息发布了最新的 SylixOS V3.4.0操作系统。在 SylixOS V3.4.0中,已正式加入了对申威 SW64 自主指令集架构的支持。

2016 年,超级计算机神威.太湖之光,搭载着首个采用国产自研指令集架构 SW64 且性能强大的计算机芯片 SW26010,取代“天河二号”登上全球超算榜首,算力排名全球第一,让申威处理器,全球瞩目。

SW64 自主指令集架构是我国在处理器领域的一项重要突破,其知识产权完全可控、自主性更高、安全性更强,核心技术可自主迭代发展。目前,SylixOS 已完成 SW64 架构的 SW831 处理器适配,成为全球首个支持 SW64 架构处理器的大型实时操作系统,填补了 SW64 自主指令集架构在实时操作系统领域的空白。

SW64 指令系统

SW64 是申威研发的自主指令系统,有以下特点:

1.“申威 64”指令系统,32 位定长指令,64 位字长

2.整数:支持8 位、16 位、32 位、64 位和部分 256 位整数运算

3.浮点:支持 IEEE 754 单精度和双精度浮点运算,支持浮点除法和浮点平方根运算

4.向量:支持 256 位的整数短向量、浮点短向量运算

5.密码:支持 AES、SHA、SM3、SM4 等密码运算

基于 SW64 指令系统的申威 831 处理器

申威 831 处理器是基于第三代“申威 64”二次优化版核心(C3B)的国产高性能多核处理器,主要面向中低端服务器和高端桌面计算机等应用。

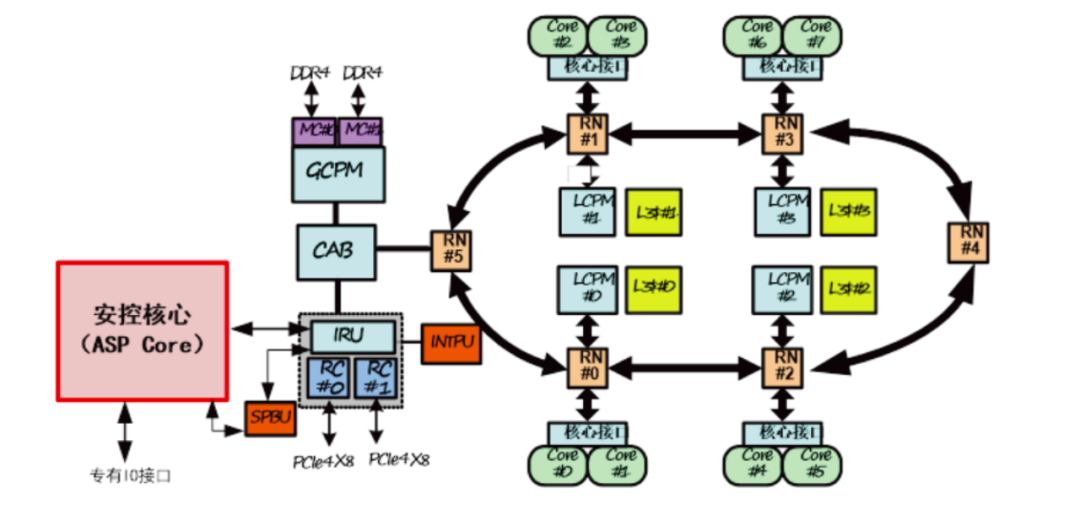

申威 831 采用 CC-NUMA 多核结构和 SoC 技术,单芯片集成了 8 个 64 位 RISC 结构的申威处理器核心、1 个主动安全管理核心(ASP)、2 路 DDR4 存储控制器接口、16 lane PCI-E 4.0 标准 I/O 接口。最高工作频率可达 2.5GHz。

1.采用“申威 64”自主指令系统

2.基于第三代“申威 64” 二次优化版核心(C3B)的 8 核 64 位通用处理器

3.采用 SoC 集成结构,片内包含 2 路 DDR4 存储控制器接口以及 16lane 的 PCI-E 4.0 标准 I/O 接口

4.安全防护:内置主动安全管理核心,与计算处理器之间单向物理隔离,具有最高访问权限,负责计算资源可信执行及防御未知特征攻击

5.计算性能:双精度浮点性能可高达 320 GFlops,整数性能可达 220 Gops

6.访存性能:最大传输率为 25.6 GB/s,最大总存储容量 64 GB

7.I/O 性能:双向聚合有效带宽可达到 64 GB/s,支持 I/O 虚拟化

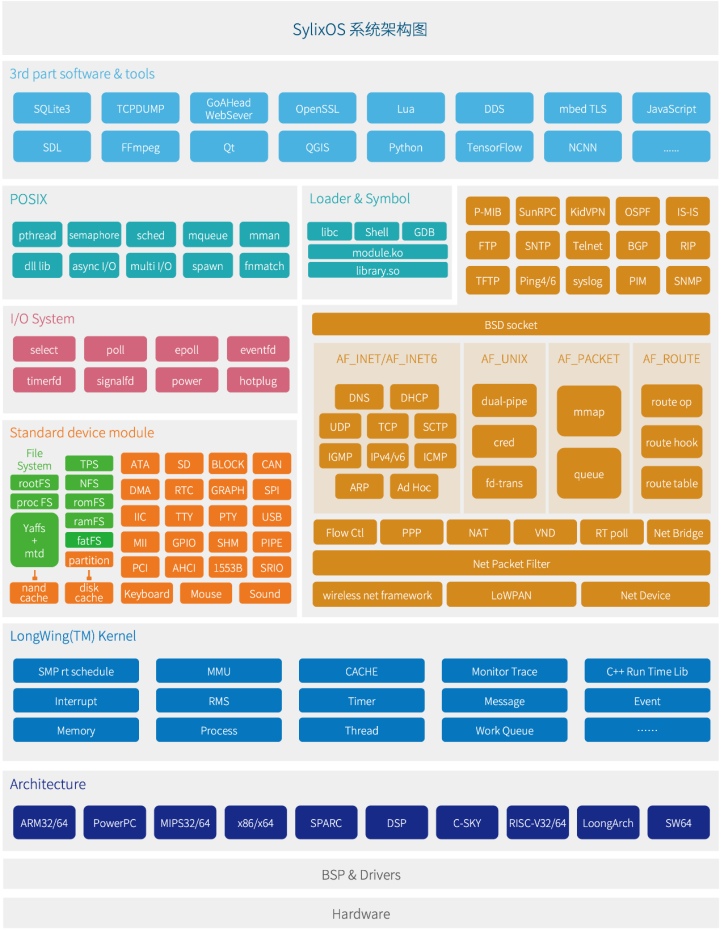

国产大型实时操作系统 SylixOS

SylixOS 经过多年的持续开发与改进,现已被广泛应用于航空航天、电力电网、轨道交通、机器人、新能源等国家重要领域,是各个领域智能装备的基础核心软件,SylixOS 具有如下优势:

1.SylixOS 内核自主化率达到 100% (依据工信部评估报告),拥有完全自主可控的技术能力,满足国产化需求

2.SylixOS 支持对称多处理器(SMP)平台,并且具有实时进程及动态加载机制,满足多部门分布式软件开发需求,支持各部门应用软件在操作系统上的集成

3.处理器跨平台支持,支持 ARM、MIPS、PowerPC、x86、SPARC、DSP、RISC-V、C-SKY、LoongArch、SW64 等架构处理器,支持如飞腾、龙芯、中天微、兆芯、全志、瑞芯微、M78 、复旦微、申威等主流国产处理器,便于用户在升级硬件平台的时候,进行应用程序的移植,减少移植的工作量

4.SylixOS 产品成熟,编程简便,系统架构简洁,配合专用的集成开发环境 RealEvo-IDE 及硬件模拟器 RealEvo-Simulator ,便于系统开发与调试,加快软件研发速度,缩短产品研制周期

5.针对不同的处理器提供优化的驱动程序,提高系统整体性能

6.硬实时内核,调度算法先进高效,性能强劲

7.SylixOS 应用编程接口符合 GJB、IEEE、ISO、IEC 相关操作系统编程接口规范,用户已有应用程序可方便的迁移到 SylixOS 上

8.POSIX 兼容度高达 98%

9.支持国家标准可信计算

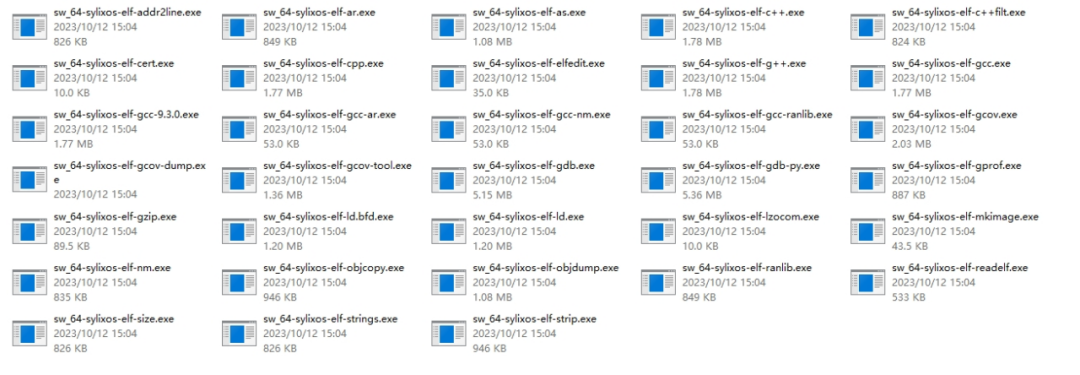

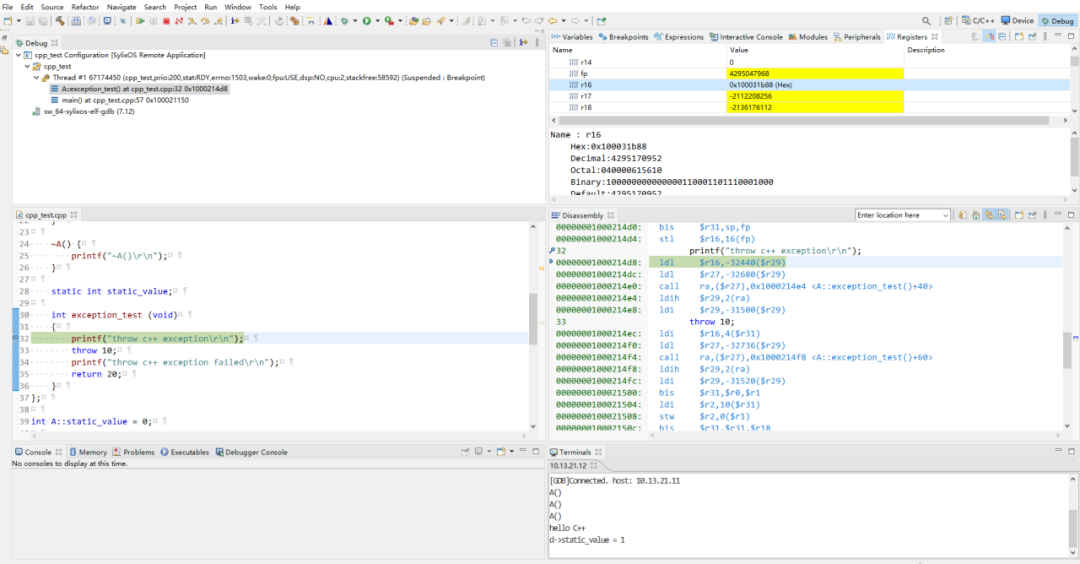

RealEvo-IDE 6.0 已加入 SW64 编译器

翼辉信息为开发者们提供了一套功能强大的 SylixOS 集成开发套件,包括集成开发环境 RealEvo-IDE、仿真环境 RealEvo-Simulator、编译器 RealEvo-Compiler、Qt 图形开发包 RealEvo-Qt5SylixOS、TpsFs 掉电安全文件系统访问工具 RealEvo-TpsFs-Explorer 等。

RealEvo-IDE 6.0 已经加入了最新的 SW64 体系结构 GCC 9.3.0 编译器和 GDB 7.12 调试器:

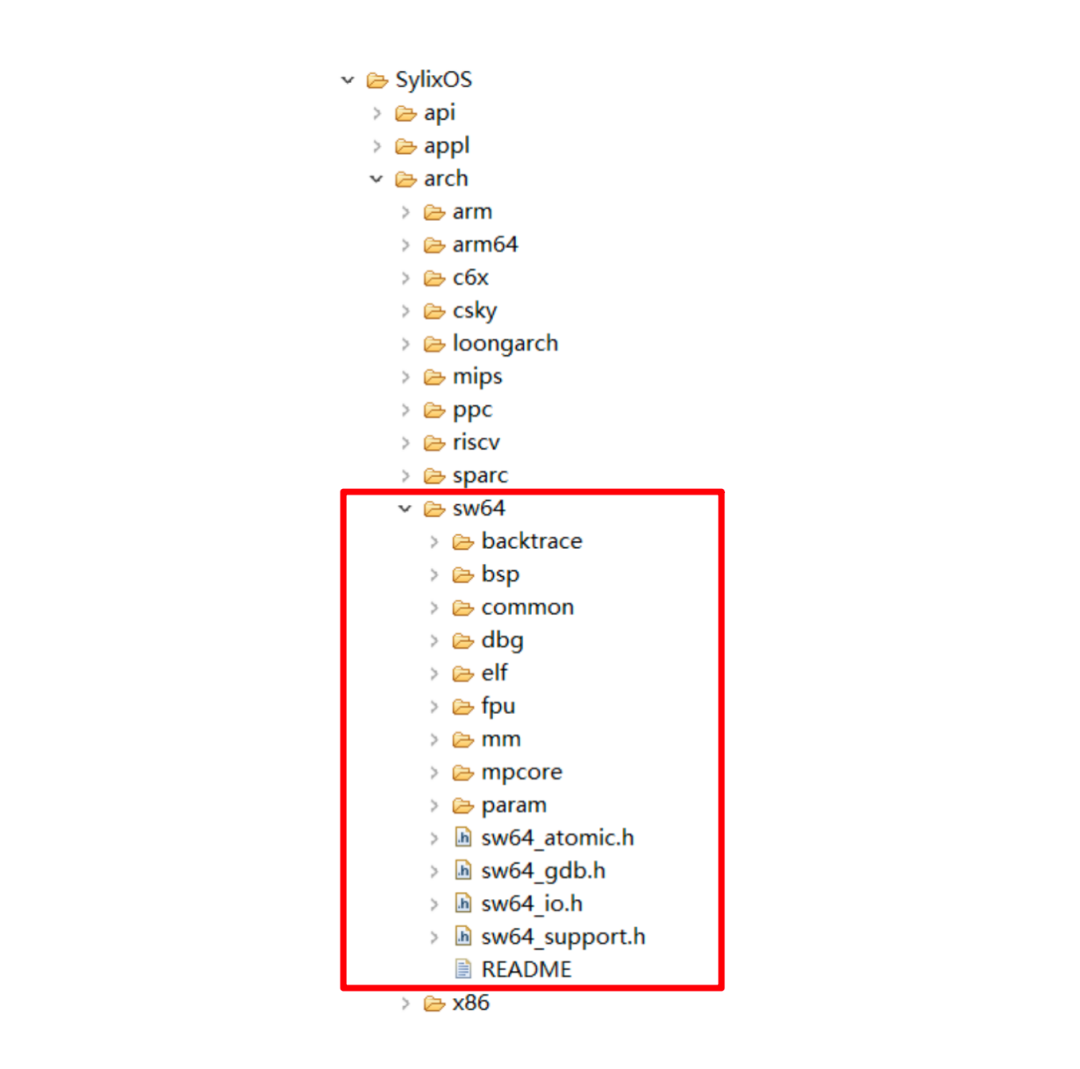

SylixOS 支持 SW64 体系结构

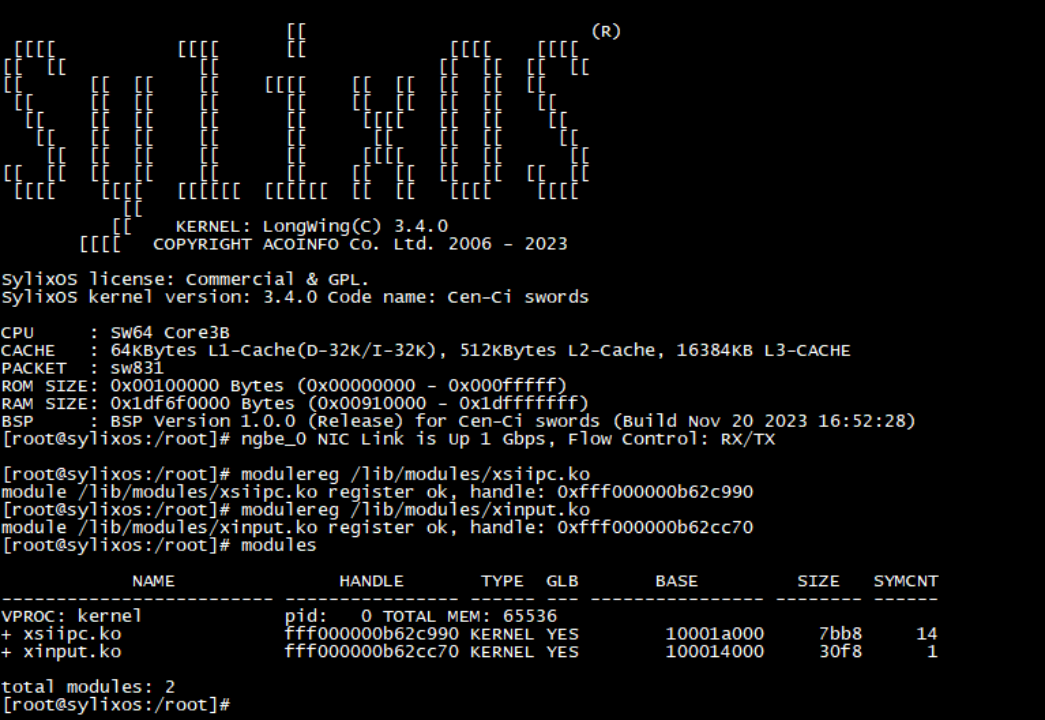

最新的 SylixOS V3.4.0 操作系统已加入 SW64 体系结构代码:

SylixOS SW64 体系结构代码有着如下的功能特性:

1.支持多核 SMP 和 AMP

2.根据 hmcode 接口规则优化任务寄存器上下文保存,使得任务切换、中断响应更为迅速

3.全面接管 CPU 异常并进行处理,用户无须关心如何处理 CPU 异常

4.支持硬浮点协处理器,支持浮点异常处理

5.支持 MMU 和 CACHE,支持 8K 页面大小

6.实现非对齐内存访问仿真处理以支持非对齐内存访问

7.支持内核模块、应用程序、共享库动态加载功能

8.支持应用程序调试和调用栈回溯

9.支持 OpenMP 并行计算、GCOV 代码覆盖率分析

SylixOS 支持内核模块、应用程序、共享库动态加载功能,SylixOS SW64 体系结构代码实现了 ELF(Executable and Linkable Format,可执行可链接文件格式)节区的加载和重定位,动态加载功能可以满足多部门分布式软件开发需求,支持各部门应用软件在操作系统上的集成:

SylixOS 内建了 C/C++ 应用程序调试服务器,SylixOS SW64 体系结构代码实现了获取、设置寄存器的接口、分析当前指令(特别是跳转和分支指令)计算跳转到下一条指令的位置、断点指令的异常处理等功能,开发者们可直接使用 RealEvo-IDE 提供强大的调试功能进行图形化的应用程序调试:

结语

自主创新、安全可控的 SW64 指令集架构以及多款 SW64 架构芯片的到来给中国“芯”的发展注入了强大动力。而大型国产实时操作系统 SylixOS 率先全面支持 SW64 架构和相关的芯片,给“芯”注入了“魂”。国产 OS 和 国产 CPU 百花齐放,“缺芯少魂”已经成为过去式。

当下,构建自主可控的信息技术体系和产业生态已成为共识。SW64 自主指令集架构和大型国产实时操作系统 SylixOS 的结合,可以共同面向任务关键型领域提供高可靠的自主解决方案。未来,翼辉信息将进一步与产业各方加强战略协同,深化扩展合作领域,助力产业生态快速发展!

审核编辑:刘清

-

处理器

+关注

关注

68文章

19259浏览量

229653 -

单芯片

+关注

关注

3文章

419浏览量

34572 -

DDR4

+关注

关注

12文章

321浏览量

40783 -

SHA

+关注

关注

0文章

16浏览量

8446 -

翼辉信息

+关注

关注

1文章

20浏览量

255

原文标题:翼辉 SylixOS 正式支持"申威"处理器架构

文章出处:【微信号:翼辉信息,微信公众号:翼辉信息】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

RISC-V指令集概述

RISC-V的指令集位宽的几点学习心得

指令集架构与微架构的区别

简述微处理器的指令集架构

RISC-V和arm指令集的对比分析

RISC-V指令集的特点总结

复杂指令集和精简指令集有什么区别

微处理器的指令集架构介绍

CISC(复杂指令集)与RISC(精简指令集)的区别

嵌入式系统的概念与范围开发 指令集架构要怎么选才合适?

RISC-V开源指令集全面指南与解析

什么是RISC-V?RISC-V指令集的优势

翼辉信息已正式加入对申威SW64自主指令集架构的支持

翼辉信息已正式加入对申威SW64自主指令集架构的支持

评论