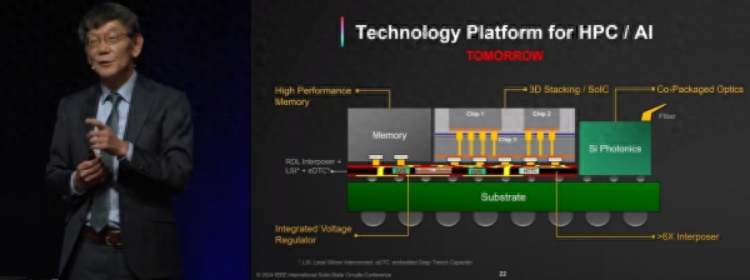

据报道,台积电在近期举行的IEDM 2023会议上制定了芯片封装计划,其中包括提供拥有万亿晶体管能力的封装产品,该计划与早前英特尔所披露的规划相似。然而,需要注意的是,这个万亿晶体管并非指单个芯片封装的总量,而是源于多个3D封装小芯片。尽管如此,台积电仍在全力以赴提高单片芯片的制造潜能,争取开发出含有两千亿晶体管的封装芯片。

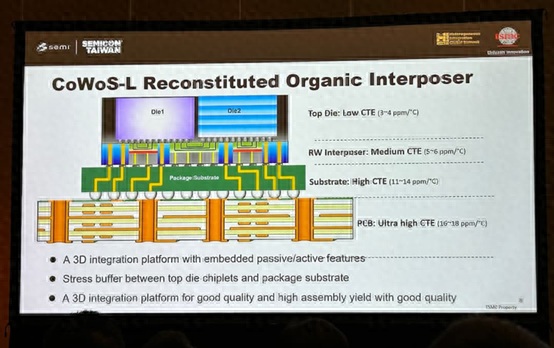

为达成此目标,公司正加紧推进N2和N2P级别的2nm制造节点研究,并同步发展A14和A10级别的1.4nm加工工艺,预计到2030年可以实现。此外,台积电预计封装技术,如CoWoS、InFO、SoIC等会不断优化升级,使他们有望在2030年前后打造出超万亿晶体管的大规模封装解决方案。

值得一提的是,台积电在本次会议中还透露他们已全面启动1.4nm级制作流程研发工作。同样,该公司再次确认,按照原定计划,2nm级制造流程将从2025年起进入大规模商业化。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

台积电

+关注

关注

44文章

5685浏览量

166970 -

封装技术

+关注

关注

12文章

553浏览量

68032 -

晶体管

+关注

关注

77文章

9744浏览量

138819

发布评论请先 登录

相关推荐

台积电2025年起调整工艺定价策略

近日,据台湾媒体报道,随着AI领域对先进制程与封装产能的需求日益旺盛,台积电计划从2025年1月起,针对其3nm、5nm以及先进的CoWoS

台积电市值近万亿美元大关,年内股价猛涨近九成

10月14日美股开盘后,台积电的股价持续攀升,最高触及194.25美元(折合约1377元人民币),再度创下股价新高。在交易过程中,台积

OpenAI CEO提7万亿美元建36座晶圆厂计划遭台积电质疑

在2023年的寒冬季节,OpenAI的首席执行官Sam Altman开启了一场东亚的旋风式访问,与台积电、三星及SK海力士等业界巨头的高管进行了会面。然而,他的初次亮相并未赢得人们的青睐。据传,

新思科技发布1.6纳米背面布线技术,助力万亿晶体管芯片发展

近日,新思科技(Synopsys)宣布了一项重大的技术突破,成功推出了1.6纳米背面电源布线项目。这一技术将成为未来万亿晶体管芯片制造过程中的关键所在。

台积电封装,新规划

来源:半导体芯闻综合 台积电高效能封装整合处处长侯上勇3 日在Semicon Taiwan 2024 中举行专题演讲,表示被视为是三种CoWoS 产品中,能满足所有条件的最佳解决方案,

谷歌Tensor G5芯片转投台积电3nm与InFO封装

近日,业界传出重大消息,谷歌手机的自研芯片Tensor G5计划转投台积电的3nm制程,并引入台积

台积电布局FOPLP技术,推动芯片封装新变革

近日,业界传来重要消息,台积电已正式组建专注于扇出型面板级封装(FOPLP)的团队,并规划建立小型试产线(mini line),标志着这家全

台积电跨制程整合晶体管架构并引入CFET,发布新一代芯片技术

张晓强强调,半导体产业的黄金时代已然来临,未来AI芯片的发展几乎99%都依赖于台积电的先进逻辑技术和先进封装技术。

台积电创新推出万亿晶体管封装平台,专注于高性能计算和AI芯片应用

台积电高级研发副总裁张晓强指出,本项新技术主要针对AI芯片性能增强。新型HBM高带宽存储器与Chiplet架构小芯片的引入需求大量组件及IC

台积电:规划1万亿晶体管芯片封装策略

台积电:规划1万亿晶体管芯片封装策略

评论