电子发烧友网报道(文/周凯扬)随着 AI、自动驾驶等应用的兴起,SoC 的设计变得愈发复杂,绝大多数走上自研芯片的公司都将绝大部分精力放在了计算单元上,比如自研核心、异构计算等等。毕竟计算单元的算力决定了其性能上限,高性能产品也更容易收获来自 AI、HPC、汽车等领域客户的订单。

打造这样一个高性能SoC,尤其是面向数据中心和自动驾驶的高性能 SoC,高速接口同样少不了,然而这一领域的自研壁垒就比较高了,往往需要组建专门的团队。所以绝大多数厂商会选择获取第三方高速接口 IP的授权或者直接购买 Chiplet,从而缩短芯片的上市时间。

高速接口 IP

在数据中心,若想要发挥最新的 800Gbps 以太网的全部速度,就必须使用一个高速串行总线接口来匹配,为此不少 NIC/DPU和交换机厂商都在基于112G 以太网PHY IP开发支持 PAM-4 的 800Gbps 产品。诸如 Alphaware、新思、Cadence等厂商,都基于新的工艺节点推出了 112G 的IP。据统计,112G 以太网的部署将在 2025 年达到峰值,这是因为要想进一步控制功耗,此类 IP 也已经过渡到 3nm 工艺,而 2025 年 3nm 也将成为主流节点之一。

此外,未来的 1.6Tbps 以太网也已经在规划中了,接口 IP 厂商们也迅速开启了新一轮的布局和研发。以新思为例,在今年的TSMC Symposium上,新思成功展示了在背板通道上实现 224G 以太网 PHY IP 的互操作,支持 PAM-4/6,可以与下一代可插拔近封装光学(NPO)和共封装光学(CPO)应用完美匹配。

数据到达服务器上后,仍需要利用高速接口,为存储和加速器提供高速连接的支持,比如 PCIe 和 CXL 等,这才是 PCIe 6.0早早就被下一代 AI 芯片设计纳入考量的原因,不少大厂和初创公司的产品路线图上,都能看到 PCIe 6.0 的身影。

新思也在今年开启了 PCIe 6.0 IP 的进程,Intel Innovation 2023大会上,新思在英特尔的PCIe 6.0 测试芯片上,展示了其 PCIe 6.0 IP在 FPGA 实现与测试芯片的互操作。这也与英特尔开启 IDM 2.0 路线后的 EDA/IP 合作紧密相关,今年 8 月,新思与英特尔宣布在英特尔未来的先进工艺节点上拓展合作关系,所以未来新思的一众标准化高速接口 IP,也会对英特尔的Intel 3 和 Intel 18A 等节点提供支持。

当然,要说从商业角度来看,目前新思的高速接口 IP 还是在与台积电的合作中取得了最大的成功。如果你对今年推出的各种高性能 AI 芯片有所关注的话,就会发现其中不少都用到了新思的DesignWare高速接口 IP。

在台积电每年举办的OIP生态系统论坛上,新思往往是年度接口IP 合作伙伴这一奖项的常胜者。比如今年,除了N2、N3P 设计架构、毫米波解决方案、3Dblox 设计原型解决方案以及与 Ansys、是德科技在 RF 参考设计流上的合作获奖外,新思在 N3E 工艺节点上提供的接口 IP 方案,也获得了台积电的接口 IP 大奖,这些也都体现了新思在高速接口 IP 上的整体实力。

Chiplet互联

早在数年前Chiplet就已经面世了,但介于当时有限的互联接口生态,几乎是只有半导体巨头独享,也没有公开的市场供设计公司购买现成的 Chiplet并用于先进封装中。这与 Chiplet 的数据互联标准有关,要想在封装内不同的 Chiplet 之间实现数据传输,就必须确定下标准。

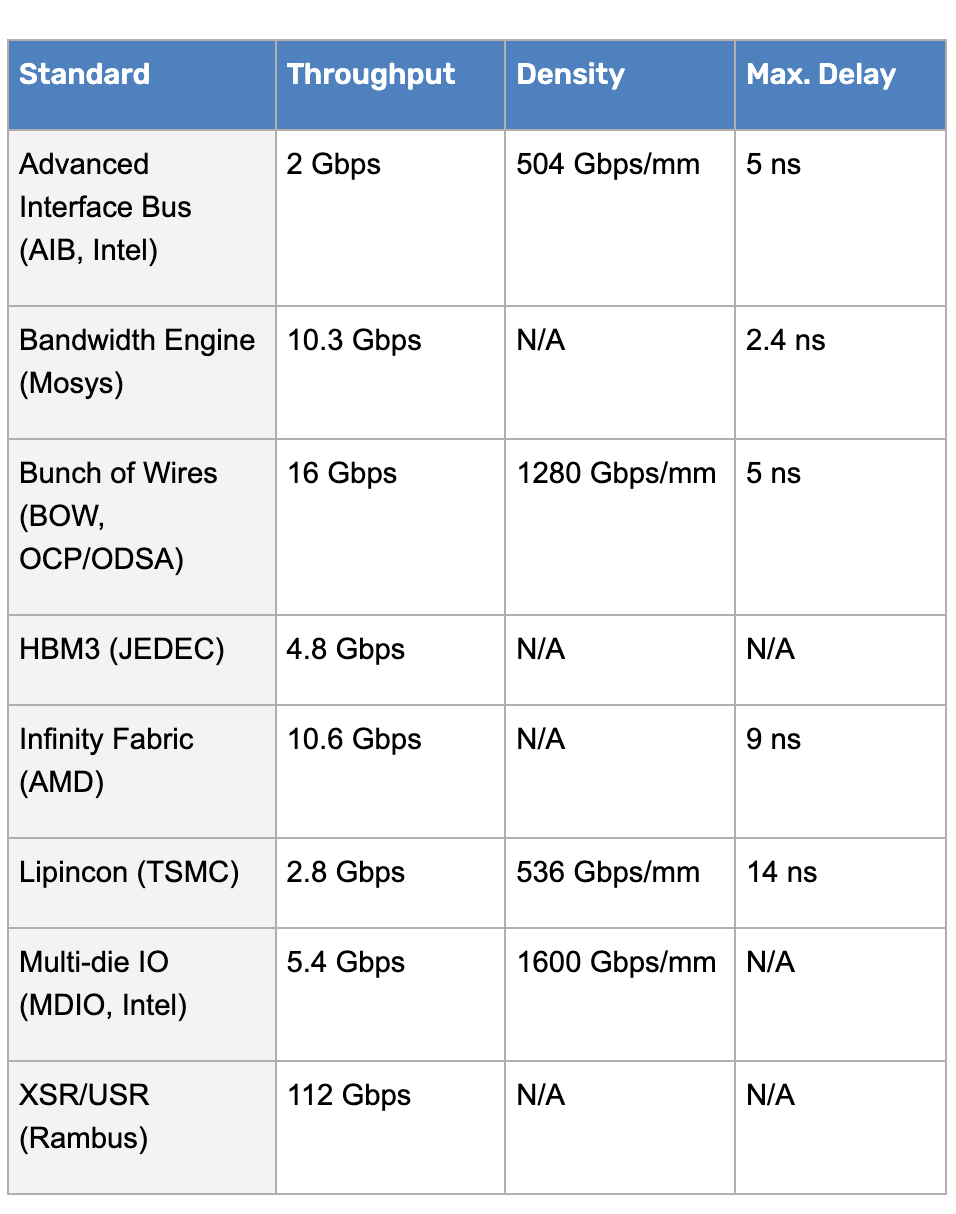

不同标准的吞吐量、密度和时延 / Cadence

如果我们来看上图所示的互联标准就会发现,除了 BOW 和 HBM 以外,Chiplet 可用接口几乎都是大厂开发的专有标准。如此一来,不仅设计受限,还必须获得 IP 授权才能为自己的产品选用合适的接口,这也就是 UCIe 标准的成立如此重要的原因。

采用并行总线架构的UCIe 可以看作是性能更高的 BOW,且不像 HBM 一样只局限于 DRAM,追求的是通用 Chiplet 之间的高速互联互通,也支持 PCIe 和 CXL 等协议。在 Chiplet 技术逐渐成熟的当下,芯粒接口标准和相关的统一生态已经初具雏形,为此产业链上下游都在跟进这一新的设计路线。但由于与 Chiplet设计紧密相关的先进封装方案成本高、产能低,所以基于 Chiplet 设计 SoC的更大规模量产还未实现。

为此国内 IP 厂商奎芯科技也提出了自己的解决方案,作为国内领先的高速接口 IP 和 Chiplet 厂商,其在 2023 年成功研发了 LPDDR5X、LPDDR4X和 ONFI 5.1接口 IP,也推出了基于 UCIe 标准的 D2D 接口 IP 以及 M2Link 系列接口芯粒产品。

而 M2LINK,就是奎芯科技为解决 HBM 互联提供的 UCIe Chiplet解决方案,实现HBM 与 SoC 的解耦。从不少采用 HBM 方案的芯片设计中可以看出,主 SoC 是与 HBM 紧紧相连且对齐的,SoC 的设计中也必须把HBM IP 占用面积和所用工艺考虑在内,这样一来SoC 的设计就频繁受限了,更不用说追求大容量 HBM必须考虑的成本和产能问题。

而奎芯科技的 M2LINK D2D 则利用一颗额外的 Chiplet 将 HBM 接口协议,转换成 UCIe 接口协议,这样主 SoC 的设计上只需将原来的 HBM IP 替换为 UCIe IP。根据奎芯科技提供的数据,这样的改动可以让 SoC 可利用面积增大 44%,最大芯片尺寸扩大两倍,SoC 与 DRAM 模组之间的距离可以拉远至 25mm。且其M2Link D2D产品支持 2D 封装,只需基于台积电 12nm 工艺节点即可实现。

写在最后

随着越来越多的厂商跨界加入自研芯片的行列,尤其是云服务厂商和互联网厂商,IP 市场还将迎来新一轮的增长。而在他们加大投入的过程中,我们也能清楚地看到,接口 IP 营收的复合增长率开始高过处理器 IP,尤其是PCIe、DDR 内存控制器与 SerDes 相关的产品。

而 Chiplet 作为更为简单快捷的设计路线,在 UCIe 生态壮大后,也势必会成为新的主流。至于国产IP 和 Chiplet 厂商,还需要在更先进的工艺节点上尽快获得硅验证,也不能止步于提供单一的解决方案,因为一站式的解决方案在不少设计厂商看来或许更有吸引力。

-

高速接口

+关注

关注

1文章

44浏览量

14774 -

chiplet

+关注

关注

6文章

433浏览量

12598

发布评论请先 登录

相关推荐

宜科FX20系列分布式I/O再添两位新成员

浅谈如何克服FPGA I/O引脚分配挑战

双向4Tbps、兼容PCIe5.0!英特尔光学I/O chiplet再突破

便携储能中种类丰富的I/O接口芯片

加速科技突破2.7G高速数据接口测试技术

BACnet/IP 智慧楼宇扩展分布式I/O

Ethernet/IP 协议分布式I/O系统

FANUC外部I/O点数不够用了怎么办?可以扩展I/O点数吗?

光I/O接口革命:4Tb/s超高速传输引领未来

什么是Chiplet技术?

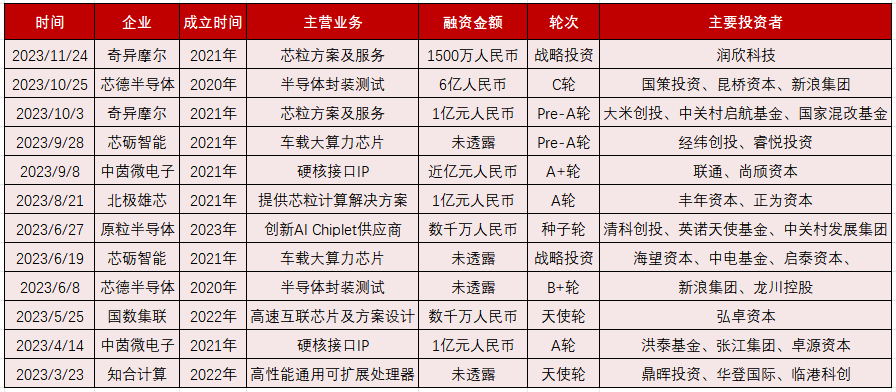

2023年Chiplet发展进入新阶段,半导体封测、IP企业多次融资

打破I/O 墙,还得靠高速接口IP和 Chiplet

打破I/O 墙,还得靠高速接口IP和 Chiplet

评论