1,带宽

示波器带宽的定义没有变,就是输入一个正弦波,保持幅度不变,增加信号频率,当示波器上显示的信号是实际信号幅度的70.7%(即3dB衰减)的时候,该对应的频率就等于示波器带宽。100MHz的带宽在测量100MHz的正弦波时,幅度会下降到原来的0.7,但是100mhz带宽的示波器不能测100mhz的方波,因为方波由基波和奇次谐波组成,5次以下的谐波对方波波形影响很大,所有要较好的看清楚方波,示波器带宽至少要比待测波形频率大5倍。

2.采样率

每秒采样多少个样点。根据香农定理,为了避免波形混叠,采样率应该大于波形频率的2倍。一般来说采样率是带宽的5倍即可,比如200M带宽的示波器,配1G采样率就可以了。追求更高的采样率无非为了抓小毛刺,但是这些高频毛刺在带宽层已经被滤掉了,更高的采样率并不能带来很好的收益。

3.存储深度

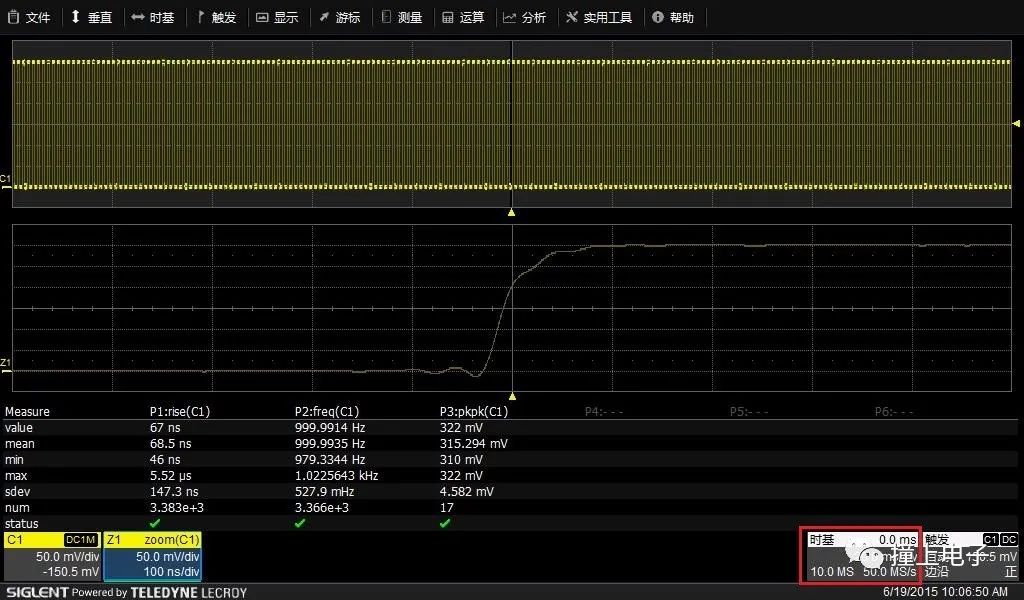

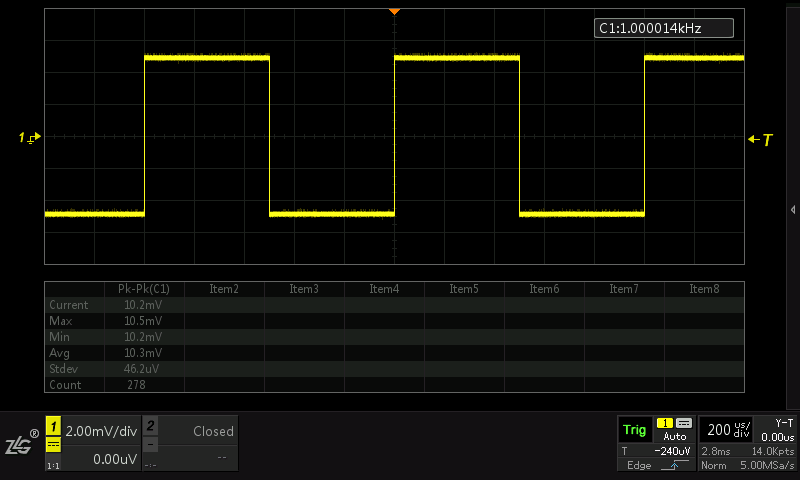

表示示波器可以保存的采样点的个数。存储深度=采样率*采样时间。我一直执着地将它称为示波器中的第一关系式,因为很多工程师在使用示波器过程中因为忘记这个关系式而产生错误。如下图为鼎阳科技SDS3000示波器的显示界面。右下方红色方框中,右边两个数值50MS/s和20ms/div相乘,再乘以10,就等于左边的数10MS。当前采样率为50MS/s,当前时基为20ms/div,因为水平轴是10格(有些示波器是12格或14格),因此采样时间为200ms, 50MS/s * 200ms = 10MS。就是说以50MS/s的采样率捕获200ms的波形,需要示波器的存储深度是10MS。

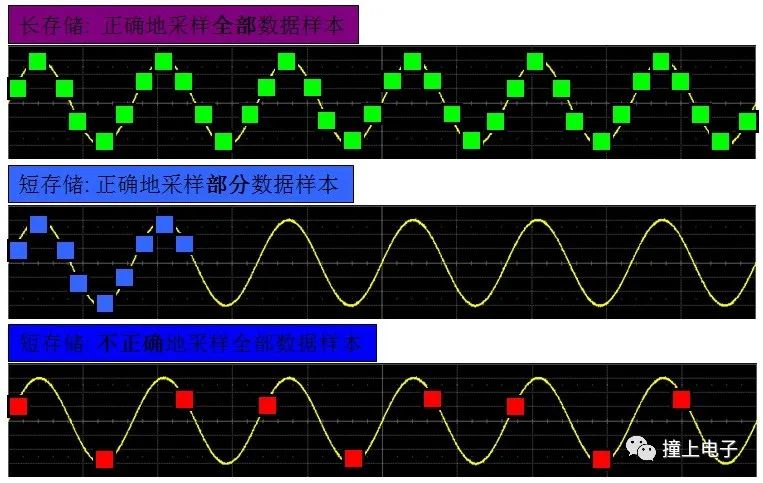

下面的示意图也清晰地演绎了这个关系式的重要性。第一个图形表明在采样率足够的前提下观察多个周期的样本,需要的存储深度深度很长,图示中需要36个采样点。第二个图形采样率依然保持不变,但存储深度变小,只有9个采样点,因此只能采样一个周期多点的波形。第三个波形仍然是存储深度很小,只有9个采样点,但仍然要采样和第一个图形一样多个周期的波形,其结果是采样率变小,测量得到的波形就会失真。

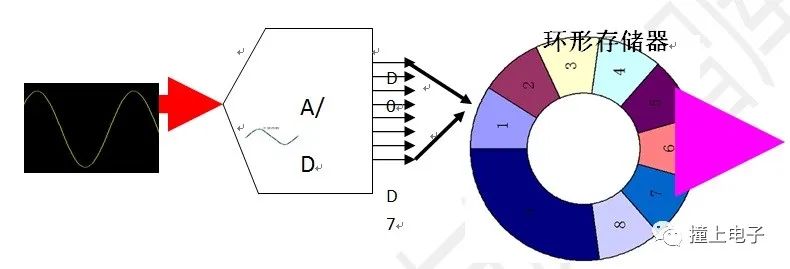

假如存储深度是“1千万个采样点”,示波器厂商写作10Mpts,10MS或10M的都有。这里,pts可以理解为points的缩写,S理解为Samples的意思。存储器保存满了,达到存储深度的极限之后怎么办?我们可以将示波器的存储器理解为环形存储器。示波器不断采样得到新的采样点会填充进来,老的采样点会自动地溢出,这样周而复始的过程直到示波器被“触发信号”“叫停”或者间隔一定长的时间被强迫“叫停”为止。“叫停”一次,示波器就将存储器中保存的这些采样点“搬移”到示波器的屏幕上显示。这两次“搬移”之间等待的时间相对于采样的时间极其漫长,被称为“死区时间”。

对于高端示波器,存储器芯片一直是核心技术,对于里面的技术细节笔者知之甚少。示波器中的ADC速率太快,普通的存储介质根本来不及在这么短的时间内“吞吐”那么大量的数据量。还是用具体的数字来理解高速ADC的超大数据量对存储器“吞吐量”提出的要求。譬如ADC的采样率是20GS/s,也就是说每秒钟要采样20G个点,而每个点是由8个0和1组成。如果ADC的输出是完全按照串行数据的传输到存储器中,那么传输速率就是160Gbps。这是什么概念?现在的PCI-Express 3.0的速率是 8Gbps,最高速的高速芯片在单板上传输速率能达到25Gbps,但还不成熟,也没有用到示波器上。高速ADC的采样点怎么传输到存储器中,这是一个难题! 其实这么高速的ADC也不可能是单芯片设计的,内部是由很多2.5GS/s或1.25GS/s,250MS/s的“小的”ADC“交织拼接”实现的。既然不完全是串行的方式实现,采用并行传输之后,传输到存储器的数据又怎么校准、对齐,再通过触发机制规整地显示到示波器屏幕上呢?这是示波器厂商的一点点小秘密。示波器发展到今天这方面门槛谈不上多高,但还是有那么一点点的。一个示波器的带宽是40Mhz,40MHZ是指示波器能测量标准正弦波的能力.但因为平时用示波器测试时基本不是正弦波,所以我们在考虑示波器带宽时,通常会按被测信号频率的三倍来考虑,更高倍当然最好.所以一定要注意,不是40 MHZ的示波器就能测40MHZ的所有信号.如果是数字示波器要,注意存储深度、采样率等都是很重要的。

-

示波器

+关注

关注

113文章

6243浏览量

184877 -

存储

+关注

关注

13文章

4308浏览量

85826 -

带宽

+关注

关注

3文章

927浏览量

40919

发布评论请先 登录

相关推荐

泰克公司推出三个用于示波器的安卓应用程序

示波器不可忽略的一个重要参数

“三个张江”的概念

EMC三个重要规律

示波器的两个最重要参数之示波器宽带和采样率详解

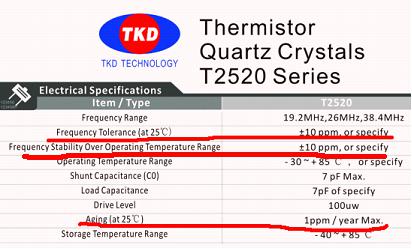

晶振选型时必须考虑的三个重要参数

示波器最重要的三个参数

示波器最重要的三个参数

评论