CPU的核心功能包括数据运算和指令控制。CPU运算的数据和执行的指令全部存储在CPU的寄存器中,这些数据和指令又都来自于CPU高速缓存。

最早的计算机系统存储由主存储和外部存储两部分组成,主存储即是插在主板上的内存,外部存储是内存以外的所有存储设备。早期的计算机“系统”内置在主板的ROM(一种断电后数据不会丢失的内存)中,而不是存储在硬盘里,数据处理的方式也是将数据都加载到主存中进行处理。所以硬盘驱动器与软盘驱动器、光盘驱动器等一样都是外部存储设备。主存是CPU和外部存储之间的一个缓冲区,为高效的运算处理提供了保障。

随着CPU性能的提升,CPU的处理速度与内存的传输速度逐渐拉开了差距。于是CPU中开始内置更高速的内存,缓解二者之间的性能差距,CPU中的内存被称作CPU缓存。

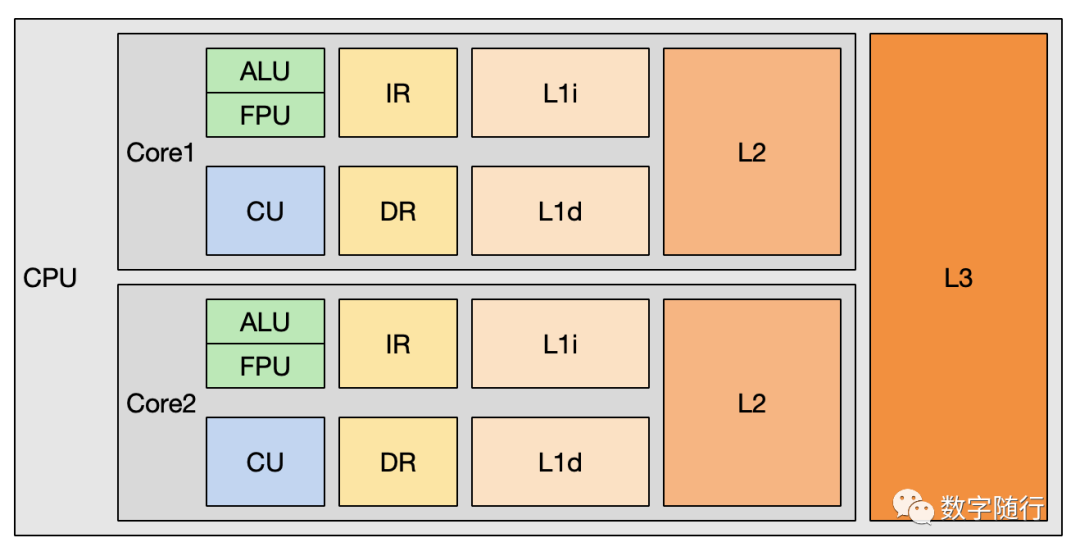

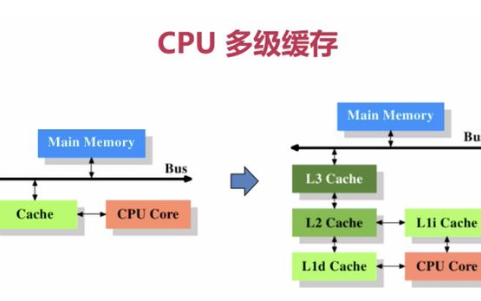

CPU缓存分为L1(一级缓存)、L2(二级缓存)、L3(三级缓存),也是随着CPU的演进逐渐发展出来。

L1缓存是针对CPU内核中寄存器存储的数据进行缓存。L1d缓存指令数据,例如变量和数组;L1i缓存二进制的指令。两个L1缓存可同时被CPU访问,避免了资源冲突,而且封装在CPU内部有很高的执行效率。

L2缓存是CPU单个核心中的“通用”缓存,存储的数据与内存中的数据一致,主要功能就是为内存提速。早期L2缓存集成在CPU的电路板或主板之上,现在与每个CPU核心独立集成在一起。L2缓存速度比内存要快很多,是提升性能的重要部件。

L3缓存是为了解决L2级别缓存容量问题而扩充的缓存。L3缓存的集成方式也是从CPU外部逐渐转移到CPU内部。到了多核CPU时代,L3缓存主要作用是实现多个核心之间的数据交换,但对CPU性能提升的帮助不大。

CPU中缓存示意图

随着技术的发展,存储器的性能越来越高,通用型的存储都逐渐统一为内存型存储设备。软盘基本已经消声灭迹(日本银行的老旧系统仍然在使用),光盘通常出现在播放器和游戏机中,个人计算机和服务器也逐渐采用固态硬盘,磁盘介质的硬盘驱动器只能应用在低成本大数据量的存储场景和备份场景。但是,速度又快、容量又大的存储永远都要付出高昂的成本。我们只能在整个系统中增加少量的高速缓存,缓解这个矛盾。

审核编辑:刘清

-

驱动器

+关注

关注

54文章

9120浏览量

156610 -

寄存器

+关注

关注

31文章

5621浏览量

130459 -

存储器

+关注

关注

39文章

7759浏览量

172284 -

二进制

+关注

关注

2文章

809浏览量

43221

原文标题:一文了解CPU缓存

文章出处:【微信号:Rocker-IC,微信公众号:路科验证】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

MRAM高速缓存的组成

高速缓存/海量缓存的设计实现

高速缓存Cache介绍

高速缓存(Cache),高速缓存(Cache)原理是什么?

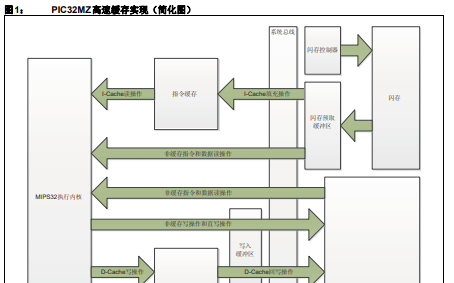

AN1600 - 在PIC32MZ器件上使用L1高速缓存

PIC32MZ器件系列中使用L1CPU高速缓存实现的风险和解决方法

在PIC32MZ器件上使用L1高速缓存

使用MPLAB Harmony v3基于PIC32MZ MCU在运行时使用高速缓存维护操作处理高速缓存一致性问题

一文了解CPU高速缓存

一文了解CPU高速缓存

评论