FPGA(可编程逻辑门阵列)是一种集成电路芯片,具有可编程的数字逻辑功能。多功能数字钟系统利用FPGA技术实现了时钟的显示、计时、报时等功能。本文将详细介绍FPGA多功能数字钟系统的原理。

一、FPGA基本原理

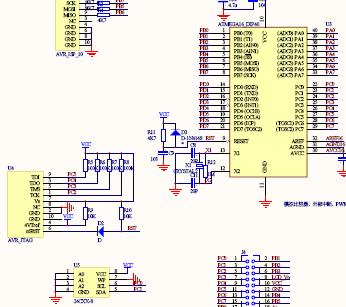

FPGA是一种基于可编程逻辑门阵列的集成电路芯片。其主要由逻辑元件和I/O(输入输出)元件组成。逻辑元件通常包括可编程门阵列(PLA)和可编程触发器阵列(PTA),用于实现数字逻辑运算和时钟处理。I/O元件用于与外部设备进行通信。

FPGA的工作原理是通过内部配置存储器存储的逻辑功能表,将输入信号转换为输出信号。这种可编程性让FPGA适用于多种应用场景,包括数字钟系统。

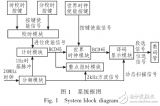

二、多功能数字钟系统组成

- 时钟模块

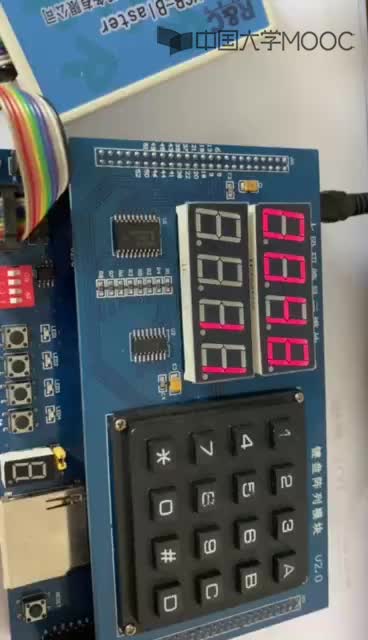

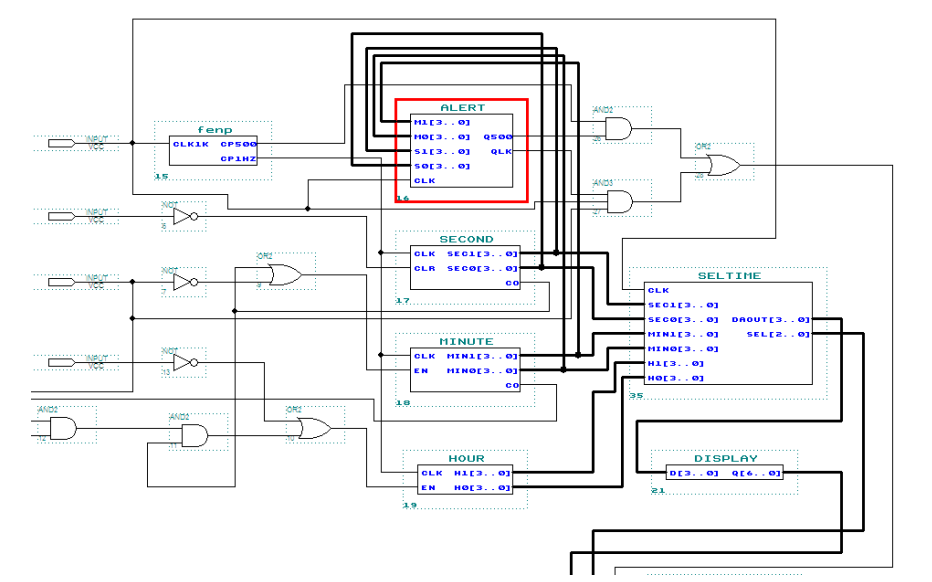

时钟模块是多功能数字钟系统的核心模块,用于控制时钟的计时和显示。时钟模块通常由一个计数器和数码管显示模块组成。

计数器用于计时,通过递增计数器的值来表示时间。计数器可以设置为24小时制或12小时制,并可以设置闹钟的时间。

数码管显示模块将计数器的值转换为数码管显示的数值。该模块通常由七段数码管驱动器和数码管组成。七段数码管驱动器将计数器的十进制值转换为对应的数码管段驱动信号,从而实现数码管的显示。

- 报时模块

报时模块用于根据当前时间进行报时。该模块通常由语音播放器和时钟控制器组成。语音播放器用于播放预存的语音报时内容,时钟控制器用于控制报时的时间间隔。 - 按键模块

按键模块用于用户对多功能数字钟系统的操作。按键模块由多个按键和按键扫描电路组成。按键扫描电路将按键状态转换为数字信号,并传递给FPGA芯片。 - 蜂鸣器模块

蜂鸣器模块用于报警和闹钟功能。蜂鸣器接收来自FPGA芯片的控制信号,当出现报警或闹钟时,发出相应的声音信号。

三、多功能数字钟系统工作流程

多功能数字钟系统的工作流程主要包括时钟显示、计时、报时和闹钟功能。

- 时钟显示

时钟显示是多功能数字钟系统的基本功能。时钟模块中的计数器根据当前时间不断递增,并将其转换为数码管显示。数码管显示模块将计数器的十进制值转换为对应的数码管段驱动信号,从而实现时钟的显示。 - 计时功能

计时功能是指可以通过多功能数字钟系统进行时间的累加和显示,通常用于计时比赛、烹饪等需要计时的场合。用户可以通过按键模块设置计时开始和结束时间,并将计时结果显示在数码管上。 - 报时功能

报时功能是多功能数字钟系统的一个重要功能。报时模块会根据设置的时间间隔,定时进行语音报时。报时模块会根据当前时间判断是否需要进行报时,若需要报时,则会触发语音播放器播放预存的报时内容。 - 闹钟功能

闹钟功能是多功能数字钟系统的常见功能。用户可以通过按键模块设置闹钟的时间,当时间到达设置时间时,蜂鸣器模块会发出声音信号作为提醒。

四、总结

FPGA多功能数字钟系统是利用FPGA技术实现的,具有时钟显示、计时、报时和闹钟等功能。时钟模块用于计时和显示,报时模块用于定时播放报时内容,按键模块用于用户的操作,蜂鸣器模块用于报警和闹钟功能。通过这些组件的精密配合,多功能数字钟系统能够满足用户对时间的显示和管理需求。

本文详细介绍了FPGA多功能数字钟系统的原理和工作流程,并通过对每个组件的分析,说明了其功能和作用。通过对FPGA多功能数字钟系统的原理了解,可以更好地了解其工作原理和应用场景,进一步提高其性能和功能。

-

FPGA

+关注

关注

1629文章

21729浏览量

602986 -

逻辑运算

+关注

关注

0文章

56浏览量

9758 -

数字钟

+关注

关注

9文章

160浏览量

31343 -

集成电路芯片

+关注

关注

0文章

62浏览量

9503

发布评论请先 登录

相关推荐

如何设计基于FPGA的多功能数字钟?

怎样去设计一种多功能数字钟

基于FPGA和Quartus II的多功能数字钟设计与实现

基于fpga的数字钟设计的两款方案(含程序)

基于Quartus II平台的多功能数字钟的设计

FPGA多功能数字钟系统原理

FPGA多功能数字钟系统原理

评论