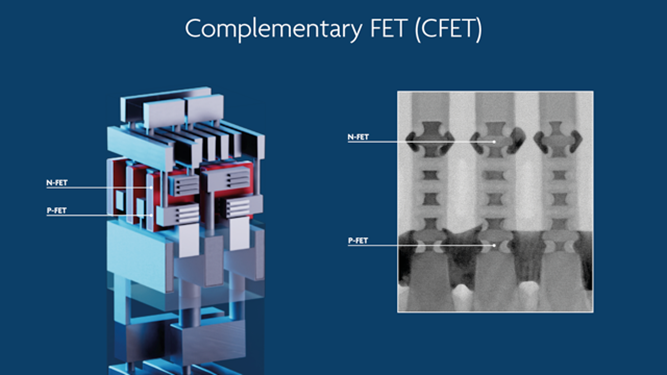

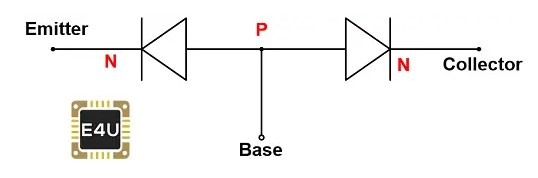

互补场效应晶体管(CFET)晶体管结构采用晶体管垂直堆叠结构,能够缓解关断状态下的漏电和晶体管阈值随栅长变化带来的问题,也使得晶体管能够在更小的空间内实现更佳的性能。下面来介绍CFET的技术进展以及未来的机遇与挑战。 在刚刚落下帷幕的2023年IEEE国际电子器件会议(IEDM2023)上,台积电、三星和英特尔各自秀出了在下一代晶体管结构领域的尖端技术。图中这款被称为“互补场效应晶体管(CFET)”的晶体管结构,被视为1nm以下制程的关键要素,是继FinFET和GAA之后的新一代的晶体管技术。它的出现,将为半导体行业带来哪些不一样的图景?

CFET示意图(图片来源:imec)

CFET将开启三维晶体管结构新纪元?

据了解,CFET与此前晶体管结构的最大不同之处,在于采用晶体管垂直堆叠结构,这或将开启三维晶体管结构新纪元。

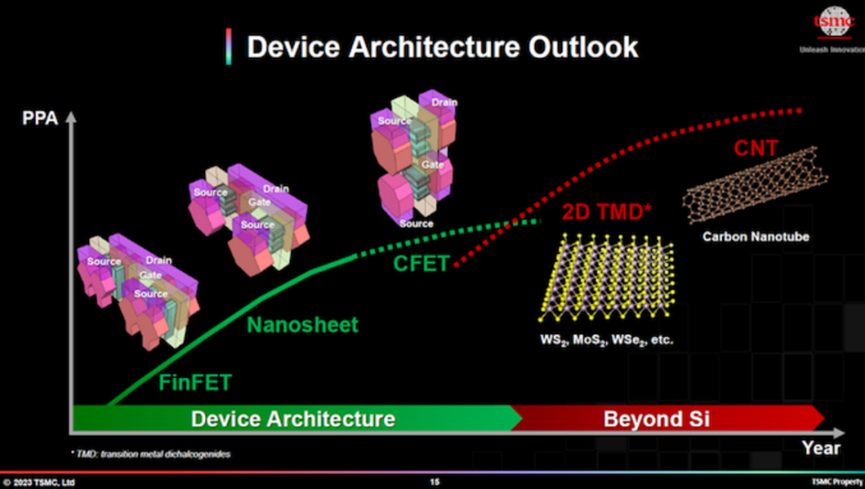

在FinFET和GAA架构出现以前,芯片晶体管结构采用的是平面MOSFET,这种结构可以通过等比例缩小器件尺寸来提高器件性能,增大芯片上器件数量。但是,当沟道长度小于一定值时,栅极对于沟道的控制能力会下降,出现短沟道效应。为了解决这个问题,业界提出了FinFET和GAA两种新型晶体管结构。前者通过将沟道向上延展形成立体结构,后者采用栅极环绕沟道的结构,来缓解关断状态下的漏电和晶体管阈值随栅长变化带来的问题,也使得晶体管能够在更小的空间内实现更佳的性能。

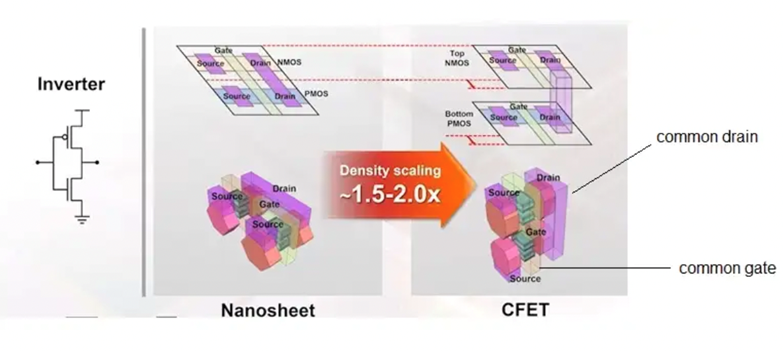

然而,由于晶体管结构从平面转换到了立体结构,难以继续通过等比例缩小晶体管尺寸来增加芯片上器件密度。随着摩尔定律的不断发展,芯片制程也愈发接近物理极限,为了能够进一步增加单位面积上的器件数量,业内开始尝试将原本的立体结构晶体管再进行堆叠,提出了采用垂直堆叠结构的CFET。

台积电最新资料显示,采用CFET垂直堆叠架构的芯片,相较采用Nanosheet(GAA)架构的器件,面积最多能缩小50%。

采用CFET架构的器件面积最多能够缩小50%(图片来源:台积电)

三大家集体公布CFET相关技术进展

基于此,先进制程的三大头部玩家台积电、三星、英特尔都在密切关注CFET相关技术。

台积电指出,CFET晶体管现已在台积电实验室中进行性能、效率和密度测试,并已经实现了48nm的栅极间距。此外,台积电还介绍了在CFET晶体管方面独特的设计和制造方法:在顶部和底部器件之间形成介电层以保持它们的隔离,这种设计可以减少漏电和功耗。为了进一步实现更好的性能和更高的集成度,台积电在其CFET晶体管工艺中,尝试将纳米片中硅和硅锗的交替层进一步隔离。例如,台积电通过特定的蚀刻方法去除纳米片中的硅锗材料,从而释放硅纳米线。为了能将纳米片中硅和硅锗的交替层进一步隔离,台积电使用了锗含量异常高的硅锗。这种材料比其他SiGe层蚀刻得更快,因此可以在释放硅纳米线之前构建隔离层。

台积电在最新的架构迭代介绍中加上了CFET结构(图片来源:台积电)

三星将CFET晶体管结构称为3DSFET,目前的栅极间距为45/48nm。在技术创新方面,三星实现了对堆叠式pFET(P沟道场效应管)和nFET(n沟道场效应管)器件的源极和漏极进行有效的电气隔离。这种隔离可以有效地减少漏电流,提高器件性能和可靠性。此外,三星还通过将湿化学物质的刻蚀步骤替换为新型干法刻蚀,以此让芯片中CFET器件的良率显著提升。

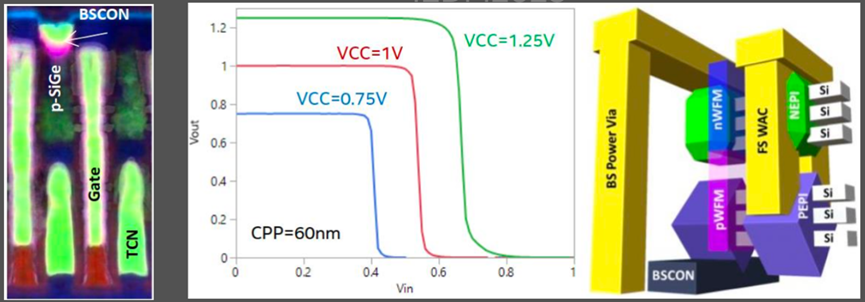

英特尔展示了将CFET晶体管结构与背面供电技术相结合的新技术,并利用该技术实现了60nm的栅极间距。英特尔表示,此次在CFET方面的创新之处,在于将PMOS(P型金属氧化物半导体)和NMOS(N型金属氧化物半导体)结合在了一起,使得开关速度和驱动能力具有互补性,从而提升了晶体管的整体性能。将PMOS和NMOS与其PowerVia背面供电器件触点相结合,以此更好地控制电流的流动,提高电源效率。

英特尔CFET示意图(图片来源:英特尔)

虽然,三家均未透露将在具体哪个制程节点中采用该晶体管结构,但公开资料显示,台积电或将在其2032年量产的A5工艺中,采用CFET架构。

台积电或将在其2032年量产的A5工艺中采用CFET架构(图片来源:imec)

平衡成本和性能问题是关键

CFET结构“初露端倪”,让业界看到了晶体管结构新的发展前景。然而,业内专家预估,CFET结构需要7~10年才能投入商用。

为何不能短时间内在现有的芯片制程中采用三维晶体管结构?目前CFET制程需要解决多层堆叠带来的大量的技术挑战。

目前,CFET拟采用的工艺路径是一次外延生长PFET和NFET两种器件的多层结构,再分别在两种外延层上制造FET。这大幅增加了器件制造的工艺复杂度,过去在FinFET和GAA中行之有效的工艺方法大部分不再适用。以FET源漏模块为例,不能再采用离子注入工艺对源漏进行掺杂,需要用杂质在线外延的办法把掺杂元素带到源漏区附近,再扩散达成掺杂。这些改变,需要从头开发新工艺,并逐渐使之成熟。类似的改变还有很多,需要大量和长周期的工艺研发,才能解决存在的全部技术挑战。

在CFET所需要的新工艺中,多层堆叠热退火问题是CFET面临的最大挑战之一。据了解,半导体材料在晶体生长和制造过程中,由于各种原因会出现缺陷、杂质、位错等结构性缺陷,导致晶格不完整,施加电场后的电导率较低。通过热退火处理,可以使材料得到修复,结晶体内部重新排列,去除大部分缺陷和杂质,恢复晶格完整,提高电导率和电学性能。

半导体热退火需要在1050℃的高温下进行,在进行热退火操作后,还需要在芯片内部用铜和铝等金属进行互联。在以往的非堆叠晶体管结构中,仅进行一次热退火即可,而在堆叠结构中,每堆叠一层就要再多进行一次热退火。此外,芯片内部的很多金属互联材料难以在1050℃的高温中保持稳定。这也导致在第二层晶体管结构中,无法采用传统方式来进行整体的热退火,需要采用激光进行局部退火从而效避开金属连接处。而采用激光退火不仅会增加工艺难度,还会因设备成本高而提升整体芯片制造成本。

“这就好比,原本用毛笔写的字,现在要用签字笔来写。字的大小没变,但需要用签字笔一点点地描绘。因此,采用CFET结构的芯片,需要先解决用激光进行热退火带来的成本问题,才能加快商用的步伐。” END 转载内容仅代表作者观点 不代表中国科学院半导体所立场

审核编辑:黄飞

-

英特尔

+关注

关注

61文章

9978浏览量

171855 -

场效应管

+关注

关注

47文章

1163浏览量

63985 -

台积电

+关注

关注

44文章

5647浏览量

166593 -

晶体管

+关注

关注

77文章

9698浏览量

138322

原文标题:下一代晶体管结构:小荷已露尖尖角

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

NMOS晶体管和PMOS晶体管的区别

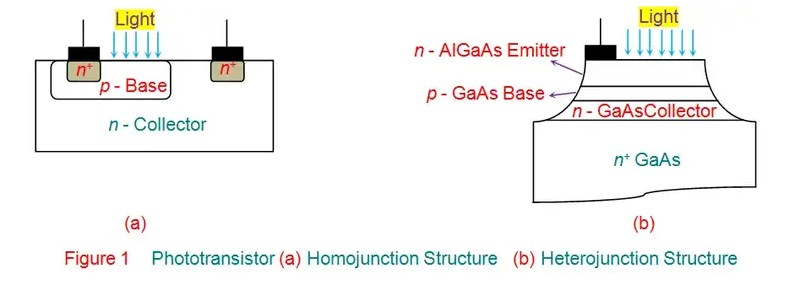

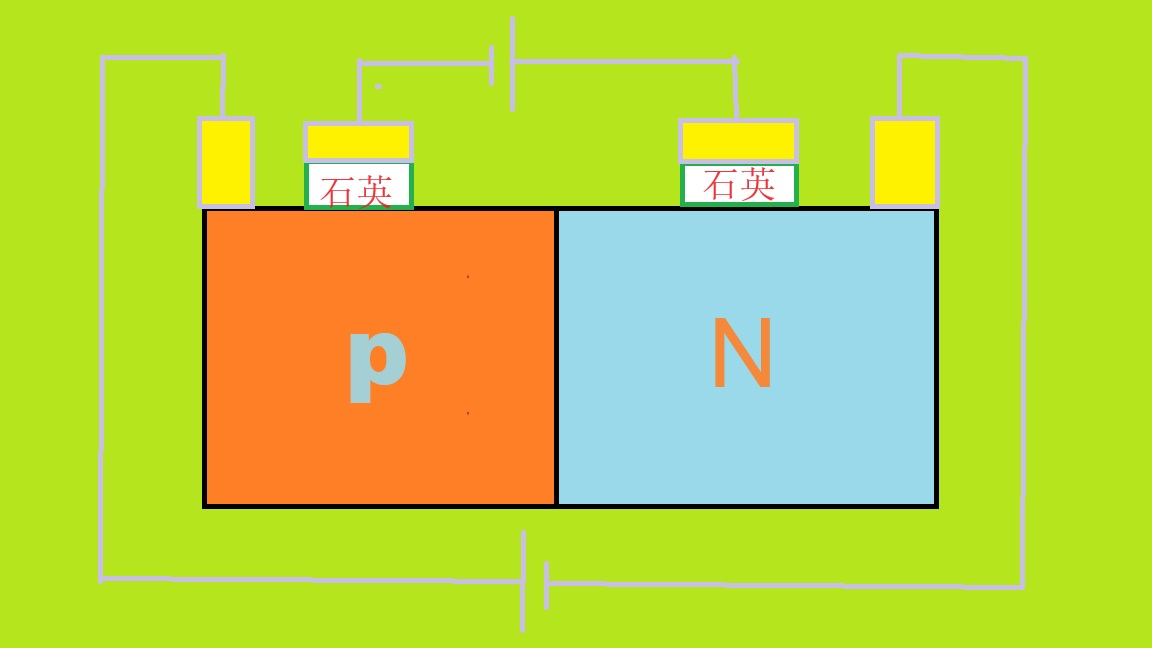

什么是光电晶体管?光电晶体管的工作原理和结构

PNP晶体管的工作原理和结构特性

探索管材加工的未来-高速三维激光切管机

泰来三维|文物三维扫描,文物三维模型怎样制作

什么是达林顿晶体管?达林顿晶体管的基本电路

CFET将开启三维晶体管结构新纪元?

CFET将开启三维晶体管结构新纪元?

评论