AHB(先进高性能总线)

随着深亚微米工艺技术日益成熟,集成电路芯片的规模越来越大。数字IC从基于时序驱动的设计方法,发展到基于IP核复用的设计方法,并在SOC设计中得到了广泛应用。在基于IP核复用的SoC(System on Chip的缩写,称为系统级芯片,也有称片上系统)设计中,片上总线设计是最关键的问题。为此,业界出现了很多片上总线标准。其中,由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结构。AMBA规范主要包括了AHB(Advanced High performance Bus)系统总线和APB(Advanced Peripheral Bus)外围总线。

AHB

AHB=Advanced High Performance Bus,高级高性能总线。如同USB(Universal Serial Bus)一样,也是一种总线接口。

AHB主要用于高性能模块(如CPU、DMA和DSP等)之间的连接,作为SoC的片上系统总线,它包括以下一些特性:单个时钟边沿操作;非三态的实现方式;支持突发传输;支持分段传输;支持多个主控制器;可配置32位~128位总线宽度;支持字节、半字和字的传输。AHB 系统由主模块、从模块和基础结构(Infrastructure)3部分组成,整个AHB总线上的传输都由主模块发出,由从模块负责回应。基础结构则由仲裁器(arbiter)、主模块到从模块的多路器、从模块到主模块的多路器、译码器(decoder)、虚拟从模块(dummy Slave)、虚拟主模块(dummy Master)所组成。针对Soc设计中IP复用问题提出了一种新的解决办法。传统的方法是将特定功能模块的非标准接口标准化为AHB主/从设备接口。本文提出了一种新的基于ARM的Soc通用平台设计寄存器总线标准接口,这种设计使整个系统的结构清晰,增强系统的通用性与系统中功能模块的可移植性。

AMBA

AMBA 2.0规范包括四个部分:AHB、ASB、APB和Test Methodology。AHB的相互连接采用了传统的带有主模块和从模块的共享总线,接口与互连功能分离,这对芯片上模块之间的互连具有重要意义。AMBA已不仅是一种总线,更是一种带有接口模块的互连体系。

APB

APB主要用于低带宽的周边外设之间的连接,例如UART、1284等,它的总线架构不像AHB支持多个主模块,在APB里面唯一的主模块就是APB 桥。其特性包括:两个时钟周期传输;无需等待周期和回应信号;控制逻辑简单,只有四个控制信号。

1)系统初始化为IDLE状态,此时没有传输操作,也没有选中任何从模块。2)当有传输要进行时,PSELx=1,PENABLE=0,系统进入SETUP状态,并只会在SETUP 状态停留一个周期。当PCLK的下一个上升沿时到来时,系统进入ENABLE 状态。

3)系统进入ENABLE状态时,维持之前在SETUP 状态的PADDR、PSEL、PWRITE不变,并将PENABLE置为1。传输也只会在ENABLE状态维持一个周期,在经过SETUP与ENABLE状态之后就已完成。之后如果没有传输要进行,就进入IDLE状态等待;如果有连续的传输,则进入SETUP状态。

转换

大多数挂在总线上的模块(包括处理器)只是单一属性的功能模块:主模块或者从模块。主模块是向从模块发出读写操作的模块,如CPU,DSP等;从模块是接受命令并做出反应的模块,如片上的RAM,AHB/APB 桥等。另外,还有一些模块同时具有两种属性,例如直接存储器存取(DMA)在被编程时是从模块,但在系统读传输数据时必须是主模块。如果总线上存在多个主模块,就需要仲裁器来决定如何控制各种主模块对总线的访问。虽然仲裁规范是AMBA总线规范中的一部分,但具体使用的算法由RTL设计工程师决定,其中两个最常用的算法是固定优先级算法和循环制算法。AHB总线上最多可以有16个主模块和任意多个从模块,如果主模块数目大于16,则需再加一层结构(具体参阅ARM公司推出的Multi-layer AHB规范)。APB 桥既是APB总线上唯一的主模块,也是AHB系统总线上的从模块。其主要功能是锁存来自AHB系统总线的地址、数据和控制信号,并提供二级译码以产生APB外围设备的选择信号,从而实现AHB协议到APB协议的转换。

DMA

直接内存访问(DMA,Direct Memory Access)是一些计算机总线架构提供的功能,它能使数据从附加设备(如磁盘驱动器)直接发送到计算机主板的内存上。

通常会指定一个内存部分用于直接内存访问。在ISA总线标准中,高达16兆字节的内存可用于DMA。EISA和微通道架构标准允许访问全套内存地址(假设他们可以用32位寻址)。外围设备互连通过使用一个总线主控器来完成直接内存访问。直接内存访问的另一个选择是程控输入输出(PIO)接口。在程控输入输出接口中,设备之间所有的数据传输都要通过处理器。ATA/IDE接口的新协议是Ultra DMA,它提供的突发数据传输速率可达33兆字节每秒。具有Ultra DMA/33的硬盘驱动器也支持PIO模式1、3、4和多字DMA模式2(每秒16.6兆字节)。

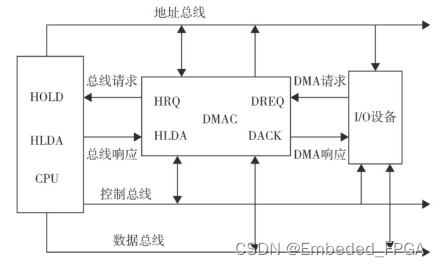

外设与存储器之间以及存储器与存储器之间的数据传输,通常采用程序中断方式、程序查询方式和DMA控制方式。程序中断方式和程序查询方式都需要CPU发出输入/输出(In/Out,I/O)的指令,然后等待I/O设备完成操作之后返回,期间CPU需要等待I/O设备完成操作。DMA在传输存储器和I/O设备的数据时,无须CPU来控制数据的传输,直接通过DMA控制器(direct memory access controller,DMAC)完成外设与存储器之间以及存储器与存储器之间的数据高速传输。 [3]DMA传输原理一个完整的DMA传输包括DMA请求、DMA响应、DMA传输和DMA结束4个步骤。DMA传输原理如图1所示,图中I/O设备为源端设备,由I/O设备向目的端设备(存储器)传输数据,其DMA的基本传输过程如下:①CPU对总线控制器进行初始化,制定工作内存空间,读取DMAC中的寄存器信息,了解DMAC的传输状态[1];②I/O设备向DMAC发送DMA请求(DMA request,DREQ),DMAC收到此信号后,向CPU发出总线保持信号(HOLD); ③CPU当前总线周期执行结束后发出总线响应信号保持确认(hold acknowledgment,HLDA); ④DMAC收到总线授权后,向I/O设备发送DMA响应信号DMA确认(DMA acknowledgment,DACK),表示允许I/O设备进行DMA传送;⑤开始传输时,DMAC首先从源地址读取数据并存入内部缓存中,再写入目的地址,完成总线数据从源地址到目的地址的传输[1];⑥DMA传输完成后,DMAC向CPU发出结束信号,释放总线,使CPU重新获得总线控制权。一次DMA传输只需要执行一个DMA周期,相当于一个总线读/写周期,因而能够满足外设数据高速传输的需要。

DMA是所有现代电脑的重要特色,它允许不同速度的硬件设备来沟通,而不需要依于中央处理器的大量中断负载。否则,中央处理器需要从来源把每一片段的数据复制到寄存器,然后把它们再次写回到新的地方。在这个时间中,中央处理器对于其他的工作来说就无法使用。DMA传输常使用在将一个内存区从一个设备复制到另外一个。当中央处理器初始化这个传输动作,传输动作本身是由DMA控制器来实行和完成。典型的例子就是移动一个外部内存的区块到芯片内部更快的内存去。像是这样的操作并没有让处理器工作拖延,使其可以被重新调度去处理其他的工作。DMA传输对于高性能嵌入式系统算法和网络是很重要的。 举个例子,个人电脑的ISADMA控制器拥有8个DMA通道,其中的7个通道是可以让计算机的中央处理器所利用。每一个DMA通道有一个16位地址寄存器和一个16位计数寄存器。要初始化数据传输时,设备驱动程序一起设置DMA通道的地址和计数寄存器,以及数据传输的方向,读取或写入。然后指示DMA硬件开始这个传输动作。当传输结束的时候,设备就会以中断的方式通知中央处理器。“分散-收集”(Scatter-gather)DMA允许在一次单一的DMA处理中传输数据到多个内存区域。相当于把多个简单的DMA要求串在一起。同样,这样做的目的是要减轻中央处理器的多次输出输入中断和数据复制任务。 DRQ意为DMA要求;DACK意为DMA确认。这些符号一般在有DMA功能的电脑系统硬件概要上可以看到。它们表示了介于中央处理器和DMA控制器之间的电子信号传输线路。

DMA会导致缓存一致性问题。想像中央处理器带有缓存与外部内存的情况,DMA的运作则是去访问外部内存,当中央处理器访问外部内存某个地址的时候,暂时先将新的值写入缓存中,但并未将外部内存的数据更新,若在缓存中的数据尚未更新到外部内存前发生了DMA,则DMA过程将会读取到未更新的数据。相同的,如果外部设备写入新的值到外部内存内,则中央处理器若访问缓存时则会访问到尚未更新的数据。这些问题可以用两种方法来解决:

1.缓存同调系统(Cache-coherent system):以硬件方法来完成,当外部设备写入内存时以一个信号来通知缓存控制器某内存地址的值已经过期或是应该更新数据。

2.非同调系统(Non-coherent system):以软件方法来完成,操作系统必须确认缓存读取时,DMA程序已经开始或是禁止DMA发生。第二种的方法会造成DMA的系统负担。

除了与硬件交互相关外,DMA也可为昂贵的内存耗费减负。比如大型的拷贝行为或scatter-gather操作,从中央处理器到专用的DMA引擎。Intel的高端服务器包含这种引擎,它被称为I/O加速技术。

在电脑运算领域,远程直接内存访问(英语:remote direct memory access,RDMA)是一种直接存储器访问技术,它将数据直接从一台计算机的内存传输到另一台计算机,无需双方操作系统的介入。这允许高通量、低延迟的网络通信,尤其适合在大规模并行计算机集群中使用。

RDMA支持零复制网络传输,通过使网络适配器直接在应用程序内存间传输数据,不再需要在应用程序内存与操作系统缓冲区之间复制数据。这种传输不需要中央处理器、CPU缓存或上下文交换参与,并且传输可与其他系统操作并行。当应用程序执行RDMA读取或写入请求时,应用程序数据直接传输到网络,从而减少延迟并实现快速的消息传输。

但是,这种策略也表现出目标节点不会收到请求完成的通知(单向通信)等相关的若干问题。

-

mcu

+关注

关注

146文章

17316浏览量

352382 -

dma

+关注

关注

3文章

566浏览量

100873 -

AHB

+关注

关注

0文章

23浏览量

9817 -

AHB总线

+关注

关注

0文章

18浏览量

9520

发布评论请先 登录

相关推荐

ZYNQ基础---AXI DMA使用

DMA是什么?详细介绍

在rtt studio使用qspi dma就是进不了中断,为什么?

经验分享 | DMA助力实时控制

stm32f4 I2S DMA中断进不去的原因?

STM32F205使定时器8的TIM_DMA_Update事件循环触发DMA2,dma不起作用是为什么?

stm32F429串口采用DMA方式发送,数据流使能失败的原因?

stm32H750VB LL库串口DMA空闲中断接收不到数据的原因?怎么解决?

STM32G070CB TIM1使用DMA 方式来产生PWM不同duty的波形,无法进入中断的原因?

Xilinx高性能PCIe DMA控制器IP,8个DMA通道

什么是DMA?DMA究竟有多快!

雅特力AT32F423 DMA使用指南

AHB与DMA详细解读

AHB与DMA详细解读

评论