摘要:

共晶芯片焊接平台因具有高效、低热阻、低成本等优势,被广泛用于表面贴装半导体分立器件的芯片焊接。随着移动消费电子产品的大量使用,越来越多的 IC 芯片被放置到小型表面封装中。对于底部没有金属化的小型 IC 芯片,经比较证明共晶焊接工艺优于聚合物粘接剂粘接,将低噪声放大器 IC 芯片以共晶焊接的方式组装到 SC88 封装中,并通过可靠性测试,成功实现量产。

1 引言

随着移动消费电子市场的快速增长,手机、智能手表、手环等移动电子产品需要大量低成本、小型化封装的 IC。主流 IC 用的芯片粘接材料是聚合物粘接剂,聚合物粘接剂粘接 IC 芯片在小型化方面普遍适用,但在成本、热传递方面还有改善的空间。

芯片的材料主要是 Si、GaAs 等,芯片与基板或引线框架的连接主要有 2 类,即聚合物粘接和钎料焊接。聚合物粘接剂有导电和非导电的,在聚合物粘接剂中掺加银粉 [1] ,称为银浆,即导电材料;非导电材料则没有掺加银粉。钎料焊接是通过高温熔化钎料把 2 种金属焊接在一起,普通钎料焊接是将钎料放置在芯片和引线框架中加热熔化,共晶焊接是钎料焊接的另外一种形式,是预先制备金属到 2 个被焊接物的接触表面,如芯片底部和引线框架表面,再在高温下将 2 个物体接触面的金属熔化,冷却后达到焊接目的。文献[2]中连接的陶瓷基片底层预先电镀了 3 μm 的金,在真空共晶炉里实现了金锡共晶焊接。

为了进一步降低成本、提高热传递能力,本文介绍了用于小型化 IC 产品的共晶焊接方法,从工艺、设备等方面解释了低成本、低热阻的原因,以实例阐述了实现过程和可靠性结果,证明小型 IC 芯片的共晶焊接在成本和热传递方面要优于聚合物粘接剂粘接。

2 共晶焊接及现状

芯片共晶焊接是瞬态液相焊接(TLPB)的一种称谓,共晶焊接预先把芯片底部金属化,芯片底部金属和引线框架金属都有自己独特的晶格排列,芯片切割后,单颗芯片底部金属和引线框架上的金属在特定比例、温度(共晶温度)下熔化成液态,冷却后芯片和引线框架被共熔合金连接在一起,达到焊接的目的。共晶焊接省略了每次焊接放置钎料的动作,其效率要高于普通钎料焊接。

共晶焊接涉及的设备形态较多,有真空共晶炉 [2] ,有实现 LED 芯片共晶焊接 [3] 的激光局部加热炉,有对Au 基共晶材料(金锡、金锗)进行焊接 [4] 的隧道炉。这些设备自动化程度不高,焊接时间为秒级,文献[5]研究了 GaAs 芯片和 Mo70Cu30 合金片的共晶焊接,GaAs 芯片底部镀金,Mo70Cu30 合金片上镀了厚度为5 μm 的 Ni-Au-Sn,在 310 ℃通过摩擦芯片 25 s 左右完成共晶焊接。以上这些形式的共晶焊接在自动化、焊接时间方面制约了器件的大规模生产,且不能满足高效率、低成本的市场需求。

3 银浆和共晶工艺设备比较

本研究在 SC88(SOT363)封装上进行共晶焊接和银浆焊接的 IC 验证,并比较工艺设备。银浆平台主流设备配置为芯片焊接机、烘箱、铜线键合机。3 个独立设备完成芯片焊接和铜线键合工序,物料在设备之间的转运需人工完成。理论上完成 1 片框架(大约 1000粒产品)的时间是 136 min(4 min+120 min+12 min)。共晶设备配置及工序流程为芯片焊接机→芯片焊接机→铜线键合机→铜线键合机,4 个步骤 1 套联机设备一气呵成,物料转运由联机设备自动完成,无需人工操作,理论上完成 1 片框架的时间是 10 min,2 种工艺平台的效率高下立判。也有少数公司将共晶设备改造成银浆设备,在芯片焊接机后加一个快速加热平台,同时连接铜线键合机,这样理论上完成 1 片框架的时间是 17 min(4 min+1 min+12 min)。使用快速加热设备需要定期清理轨道里固化的银浆残渣,否则银浆残渣会堵塞轨道,故这类设备维护效率低,会导致设备利用率低,产品成本上升。

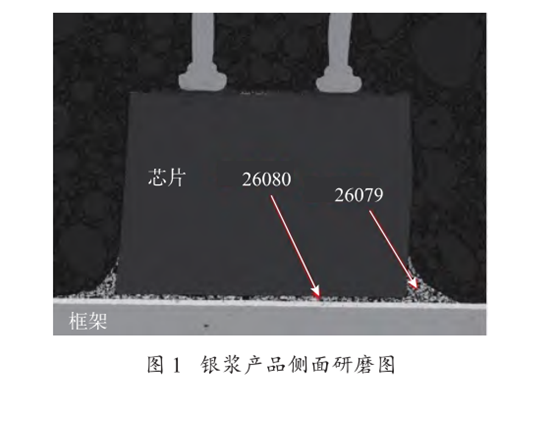

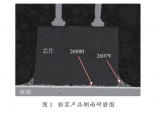

IC 芯片在银浆工艺平台上封装,银浆芯片焊接机完成点银浆、芯片吸取并放置到银浆上,需人工把芯片焊接机出料的产品送入烘箱完成银浆固化,固化后的芯片再人工送入键合机进行焊线。完成焊线后的产品侧面研磨如图 1 所示,图 1 中标记为 26079、26080的黑白掺杂物质是固化后的银浆,用 EDX 测试其元素,主要是银,26079 处显示芯片侧面有银浆爬升的情况。

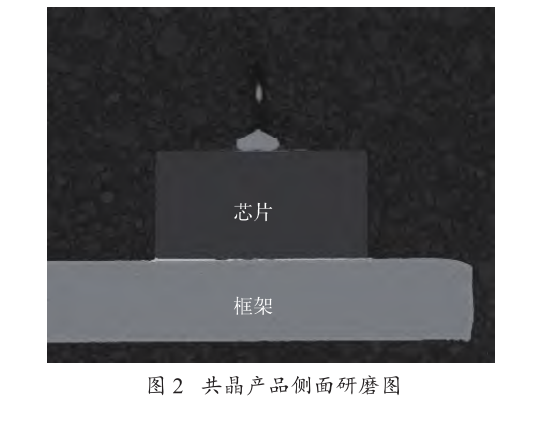

图 2 是共晶焊接、铜线键合后产品侧面研磨图,可以看出芯片与框架结合面比银浆焊接的产品侧面干净,芯片侧面没有类似银浆爬升的情况。

银浆焊接设备自动化程度低,需要在芯片焊接机、烘箱、铜线键合机之间人工转运物料,设备速度慢,并额外有银浆耗材的费用,导致总的生产运营成本较高。共晶焊接设备自动化程度高,物料从芯片焊接机到铜线键合机全自动转运,设备没有更换银浆等动作,设备停顿时间短,运行效率高,总的生产运营成本低。本文验证的芯片共晶焊接设备自动化程度高,每颗芯片从吸取到完成焊接只需 200 ms,其中共晶焊接时间在10 ms 左右,可实现产品封装的低成本、高质量焊接。

4 共晶工艺实现小尺寸 IC 封装

半导体芯片共晶焊接常用的金属有金-铜、金-锡、铜-锡等。金-铜的优点是焊接后芯片粘接强度大,可靠性高,缺点是工艺复杂,芯片底部金属和引线框架金属化工艺窗口窄。金-锡和铜-锡的优点是芯片底部金属和引线框架金属化工艺窗口宽,缺点是焊接后芯片粘接强度要弱于金-铜。粘接强度的差别源于金-铜液相温度要高于金-锡和铜-锡的液相温度。

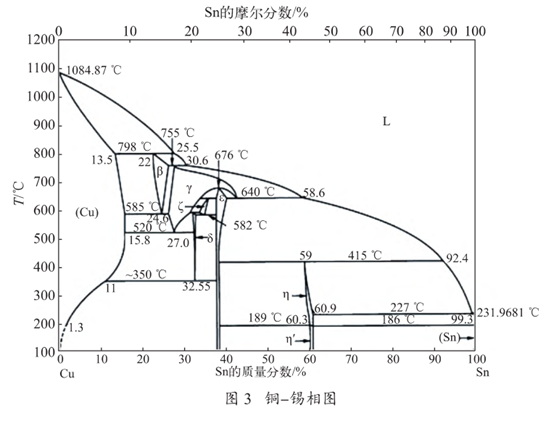

选用铜-锡金属工艺在 SC88 框架上共晶焊接低噪声放大器 IC 芯片,即芯片底部金属主要是锡,引线框架表面做铜的金属化。图 3 是铜-锡相图 [6-7] ,从图 3可知锡的质量分数分别为 99.3%和 92.4%时,铜-锡合金液相温度分别为 227 ℃和 415 ℃。

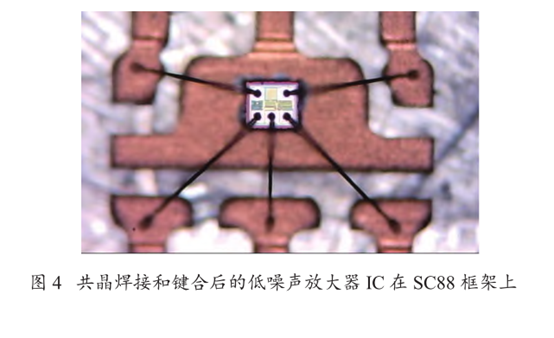

芯片底部金属经过验证确定是 Ti-Ni-Ag-Sn 合金,主要成分是锡。锡的熔点为 231.89 ℃,铜锡合金液态线温度范围为 2271085 ℃,理论上焊接设备温度在2271085 ℃均可行,考虑到焊接时间、加热轨道及引线框架结构,焊接设备温度经试验确定为 370 ℃,共晶焊接和铜线键合后的低噪声放大器 IC 在 SC88 框架上的外观如图 4 所示。

参考美国 MIL-STD- 883 的 Method 2019.9 标准判断芯片焊接质量是否合格,这款 IC 的最小推力根据标准是 100 g,实测最小推力是 416 g,即满足要求。

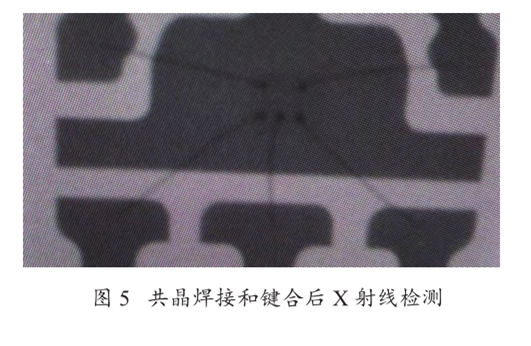

通过 X 射线检测芯片焊接后的情况如图 5 所示,未见芯片焊接空洞,满足要求。

采用共晶工艺生产的 SC88 封装低噪声放大器 IC经高温蒸煮、温度循环、高温存储、高加速应力测试等可靠性测试后没有失效,这说明共晶平台用铜-锡合金生产小尺寸 IC 芯片在技术上可行。

5 共晶焊接的优劣势

共晶平台工艺设备效率的优势是产品的封装测试成本低于银浆平台。以 SC88 和 SOT23 等封装为例,银浆平台产品除去芯片封装测试外的成本是共晶平台(考虑了芯片底部金属化的额外费用)的1.5~1.6倍。

共晶焊接可以理解为芯片级的钎料焊接,但大规模生产效率要高于普通钎料焊接。普通钎料焊接设备的芯片焊接机把钎料如 Pb95Sn2Ag2.5 放置在芯片与引线框架之间,高温熔化钎料达到连接芯片与引线框架的目的;共晶焊接把钎料(如金、锡)预先做到芯片底部和引线框架上,芯片焊接机省略了放置钎料的动作,故设备能以毫秒级的时间完成每个芯片与引线框架的焊接。另外普通钎料焊接对芯片尺寸是有要求的,太小的芯片无法使用钎料焊接,因为太小的芯片放置在未完全融化的钎料上会有倾斜、旋转等问题。

共晶设备可以焊接小至 0.20 mm×0.20 mm 的芯片。共晶焊接与银浆焊接相比在导热性方面优势明显,以 84-1LMIT1 为例,普通导电银浆的导热系数是 3.6 W/ (m·K),而 Au80Sn20 共晶的导热系数是57 W/(m·K)。

共晶焊接的缺点是需要在芯片和框架上制备共晶金属材料 [8] ,技术门槛高。业界在金-铜规模化共晶焊接上做得好的厂家不多。另外共晶焊接需要匹配芯片、引线框架的热膨胀系数,防止热应力导致的芯片裂纹。

6 结论

在 IC 芯片底部进行金属化并在共晶平台上生产是提高效率、降低成本的方法之一,通过 SC88 封装在共晶平台完成低噪声放大器 IC 的新品开发,确认背面金属为 TiNiAgSn 的 IC 可以满足大规模生产及可靠性质量要求,为分立器件生产设备平台切换成 IC 生产平台提供了一种参考方案。

来源:半导体封装工程师之家

审核编辑:汤梓红

-

芯片

+关注

关注

458文章

51403浏览量

428483 -

半导体

+关注

关注

335文章

27863浏览量

224084 -

封装

+关注

关注

127文章

8052浏览量

143576 -

焊接

+关注

关注

38文章

3248浏览量

60240

原文标题:【光电集成】共晶平台开发IC新产品的探讨

文章出处:【微信号:今日光电,微信公众号:今日光电】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ECEC推出超小型化宽温贴片封装石英晶振

电路中晶振注重超小型化空间的选择方案

请问晶振对小型汽车起了什么作用?

电源的小型化轻量化设计方案

使分立结构集成为IC实现高精度、高效率、小型化

SJ MOSFET的效率改善和小型化

一种新颖的天线小型化技术及其应用介绍

小型化晶振对电路设计的影响

爱普生32.768kHz晶振FC-135:小型化为高端产品带来的卓越优势

用于小型化IC产品的共晶焊接方法

用于小型化IC产品的共晶焊接方法

评论