FPGA (Field Programmable Gate Array) 是一种可编程逻辑器件,它可以被重新配置以执行特定的功能。CRC (Cyclic Redundancy Check) 是一种常用的校验方法,用于检测和校正数据传输中的错误。在FPGA设计中,CRC故障指的是与CRC相关的错误或问题。

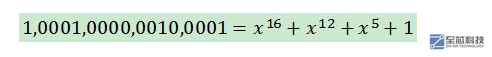

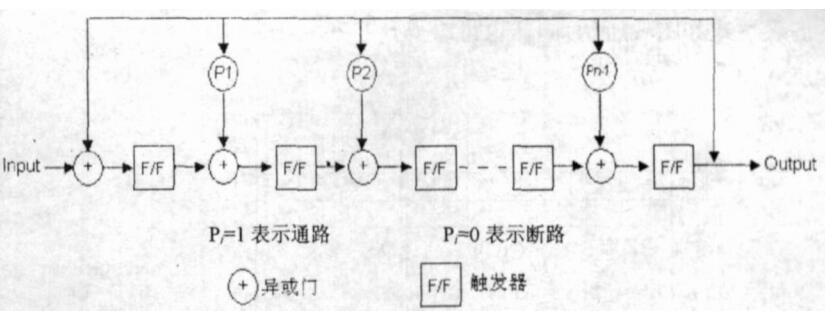

首先,让我们了解CRC是什么以及它在数据传输中的作用。CRC是一种基于二进制算法的校验方法,通过对发送的数据进行计算并附加到数据末尾,接收方能够使用相同的校验算法来检测传输中的错误。CRC可以检测多种不同类型的错误,如单比特错误、传输顺序错误、丢失的数据位等。它广泛应用于网络通信、存储系统以及数字电路等领域。

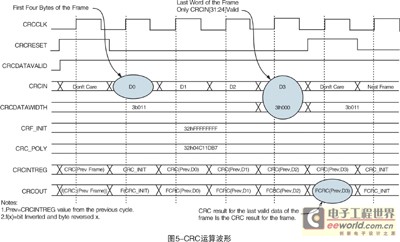

在FPGA设计中,CRC通常用于确保数据传输的可靠性。例如,在以太网通信中,发送方将数据包附加CRC校验码,并将整个包发送给接收方。接收方在接收到数据包后,使用相同的CRC算法进行计算,并校验接收到的数据与附加的CRC校验码是否匹配。如果不匹配,接收方可以确定数据包存在错误,并请求重新传输。

然而,与任何其他系统或组件一样,FPGA在实际运行中也可能出现故障。CRC故障可能由多种原因引起,包括硬件故障、设计错误或软件错误等。当CRC故障发生时,可能会出现以下情况:

- 误码率增加:CRC故障可能导致发送的数据包的错误率增加。接收方在进行CRC计算时可能无法正确验证数据的完整性,从而导致错误被接受而无法检测。

- 数据丢失:CRC故障可能导致数据包丢失。接收方无法正确验证数据以及附加的CRC校验码,因此可能会丢弃接收到的数据包,从而导致数据的丢失。

- 数据错误:CRC故障可能导致数据包中的数据位被改变。接收方在进行CRC计算时可能无法正确验证数据的准确性,从而导致数据错误。

为了解决CRC故障,需要进行仔细的故障分析和排查。以下是一些可能的排查步骤:

- 硬件调试:检查FPGA的连接和电路板上的物理连接,确保没有松动的连接或损坏的部件。

- 监测和分析:通过监测CRC错误的发生频率和模式,可以获得更多的信息来帮助分析问题。例如,如果CRC错误只出现在特定的数据传输路径上,可能是由于电磁干扰或线路问题引起的。

- 设计验证:检查FPGA设计中是否存在错误或不一致的部分。可能需要使用仿真工具对设计进行验证,以确保CRC校验算法的正确性和完整性。

- 版本控制:如果FPGA设计是基于先前版本的设计进行更新的,可能需要回滚到之前的版本或与前一版本进行比较,以确定更改是否导致了CRC故障。

- 软件分析:分析与CRC相关的软件代码,查找可能导致故障的错误。这可能需要检查CRC算法的实现是否正确,以及数据传输过程中是否存在其他并发问题。

总而言之,CRC故障指的是与FPGA设计中的CRC校验相关的错误或问题。在FPGA设计中,CRC用于确保数据传输的可靠性。如果CRC故障发生,可能会导致误码率增加、数据丢失或数据错误。为了解决CRC故障,需要进行仔细的故障分析和排查,包括硬件调试、监测和分析、设计验证、版本控制以及软件分析等步骤。通过这些步骤,可以找出CRC故障的根本原因,并采取相应的措施来解决问题。

-

FPGA

+关注

关注

1664文章

22508浏览量

639431 -

数据传输

+关注

关注

9文章

2230浏览量

67745 -

crc

+关注

关注

0文章

206浏览量

30967 -

可编程逻辑器

+关注

关注

0文章

19浏览量

4626

发布评论请先 登录

如何禁用CRC

FPGA配置CRC错误

CRC原理

Xilinx FPGA中的CRC模块

并行CRC在FPGA上的实现研究

CRC基本原理及其两个重要性质的介绍及FPGA实现

基于FPGA的并行CRC算法的UART控制器

荐读:基于FPGA 的CRC校验码生成器

CRC算法原理和CRC编码的实现方式与使用Verilog对CRC编码进行描述

CRC校验码并行计算的FPGA实现

FPGA学习之CRC校验

7系列FPGA中的POST_CRC错误检测与恢复策略

fpga报告crc故障是什么意思

fpga报告crc故障是什么意思

评论