光互连CPU技术

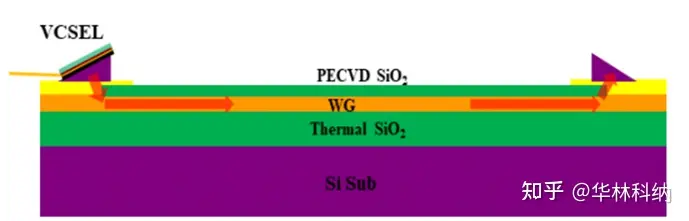

实验演示了三种可以实现与集成在光网络芯片(ONC)上的CPU核心的光互连的技术。该粘合剂技术具有>99%的透明度、高达400℃的耐高温性、耐清洗溶剂性以及GaP棱镜与波导之间的折射率匹配的特性。

聚酰亚胺微透镜具有准直25Gbps VCSEL的输出光束以将光耦合到光波导中的特性。VCSEL或光电二极管的封装尺寸具有0.4mm2的面积和0.64mm的高度,可以连接到棱镜。除了棱镜处的反射损耗外,从VCSEL到波导的净耦合损耗被测量为0.855dB。通过腔型波导的传播损耗被测量为0.258dB/cm。要与8核CPU芯片集成的光学设备的面积比可用面积174mm2小得多,<30mm2,该可用面积是根据台式CPU的当前管芯面积估计的。

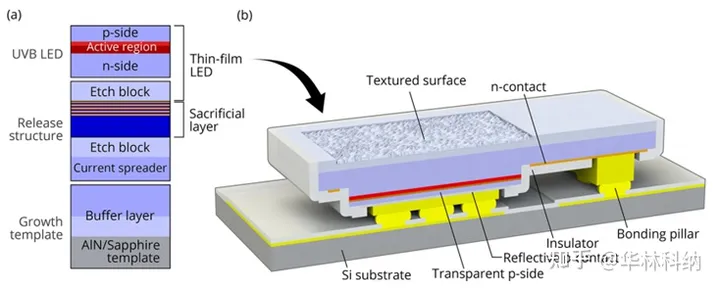

通过表面纹理化增加薄膜倒装UVB发光二极管的光提取

紫外线发光二极管(LED)的壁插效率较低,这在很大程度上受到较差的光提取效率(LEE)的限制。具有粗糙的N极性AlGaN表面的薄膜倒装芯片(TFFC)设计可以显著改善这一点。我们在这里展示了一种实现在UVB范围(280−320 nm)内发射TFFC LED的使能技术,其中包括标准LED处理与电化学蚀刻相结合以去除衬底。

电化学蚀刻的集成通过外延牺牲层和蚀刻阻挡层与LED的封装相结合来实现。当TFFC LED的N极性AlGaN侧被化学粗糙化时,LEE增强了约25%,达到2.25%的外量子效率。通过进一步优化表面结构,我们的光线追踪模拟预测TFFC LED比倒装芯片LED的LEE更高,从而获得更高的壁插效率。

晶硅片各向异性表面制绒工艺实验分析

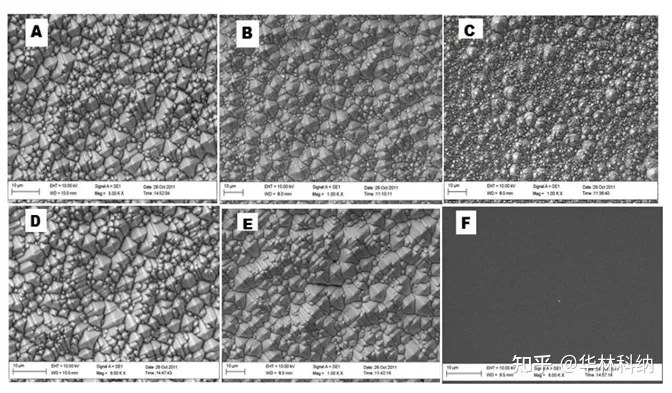

本研究报告了使用氢氧化钾(KOH)水溶液和异丙醇(IPA)的混合物作为络合剂来增强光吸收并降低可见光谱中的光学反射率的硅片表面纹理化的实验研究。实验中使用了直径100 mm、2“<100>取向、n型、电阻率(Ωcm)为7-21、表面抛光和研磨的Crochralski(CZ)硅片。所研究的工艺变量包括温度(60–90)°C,蚀刻时间(30–60)分钟,KOH和IPA的浓度分别为(1–4)mg/l和(2–8)mg/l。

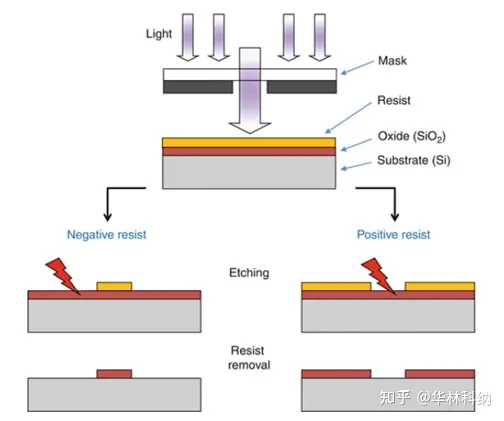

基于氢氧化钾各向异性刻蚀的高固硅微针制备

本文研究了基于KOH各向异性刻蚀的高固体硅微针的制备,旨在找到一种可控的方法来制备具有良好高度均匀性和尖端锐度的500μm高微针。在本研究中,使用200nm低应力LPCVD SiNx作为KOH蚀刻掩模;掩模形状为正方形,其侧面沿着硅片的<100>方向;在29wt%的KOH溶液中,在79℃下进行湿法刻蚀

关键词:光子集成电路、光互连、硅光子学、光接收器、垂直腔面发射激光器、发光二极管,AlGaN,电化学蚀刻,表面纹理,光提取,表面制绒工艺,氢氧化钾,各向异性刻蚀

审核编辑 黄宇

-

集成电路

+关注

关注

5388文章

11554浏览量

361914 -

二极管

+关注

关注

147文章

9647浏览量

166566 -

cpu

+关注

关注

68文章

10870浏览量

211874

发布评论请先 登录

相关推荐

半导体资料丨光子集成电路,发光二极管,制绒工艺,氢氧化钾

半导体资料丨光子集成电路,发光二极管,制绒工艺,氢氧化钾

评论