串扰(Crosstalk)是信号完整性(Signal Integrity)中的核心问题之一,尤其在当今的高密度电路板设计中,其影响愈发显著。当电路板上的走线密度增大时,各线路间的电磁耦合增强,串扰问题愈发严重。当受害线路上有信号传输时,串扰产生的噪声会叠加在该信号上,导致信号畸变。这种畸变可能会导致信号的幅度噪声增加或眼图(Eye Diagram)宽度发生变化。

眼图是数字信号的统计特性在时间域和频率域的表示,用于评估信号的总体质量。更为严重的是,当串扰噪声叠加在信号的跳变沿(Transition Edge)时,会导致信号边沿抖动(Edge Jitter)。这种抖动会严重影响信号的时序精度,甚至可能导致建立/保持时间违例(Setup/Hold Time Violations)。对于高速数字系统而言,时序精度是至关重要的,因为微小的偏差都可能导致数据错误或系统不稳定。

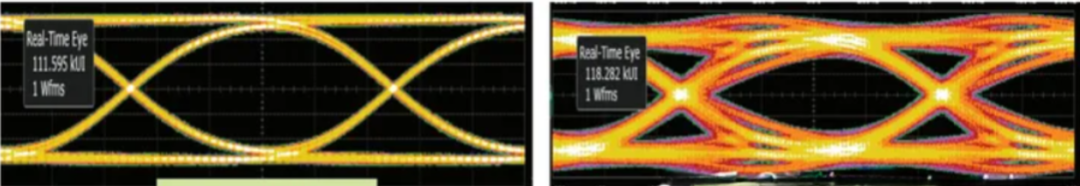

串扰对眼图的影响如下图所示:

左边的图是无串扰影响的,右边的图是有串扰影响时候的眼图。

如何进行高速信号串扰仿真

接下来我们使用SigXplorer来学习如何进行高速信号串扰仿真。Cadence SigXplorer软件是用于高速信号完整性分析和优化的重要工具。它专注于电子产品的设计和验证,尤其是高速信号传输线路的设计。SigXplorer通过电磁仿真分析,全面考虑了影响信号传输的各种因素,如反射、传输线损耗和散射参数等。利用SigXplorer,设计师可以深入了解信号传输的特性,例如延迟、振幅、眼图和时域波形等。这有助于评估信号的可靠性和稳定性,确保满足高速系统设计的要求。通过仿真和优化,SigXplorer帮助设计师调整信号传输线路的工程参数,如线路几何形状、终端阻抗匹配、负载和驱动器配置等。这有助于降低潜在问题,如反射、串扰和眼图闭合等。

串扰的形成根源在于导体间的耦合作用。在多导体的系统中,导体之间通过电场和磁场相互影响,发生能量传递。这种能量传递会将信号的一部分传递给临近的导体,从而在受害线路上产生噪声,影响信号的完整性。因此,串扰是由于导体间的耦合作用,将信号能量传递给临近导体而形成的噪声。我们将构建一个信号传输链路,以探讨线距对串扰的影响。在搭建链路的过程中,我们将观察线距的变化如何影响信号传输的稳定性,以及串扰的程度。通过这一分析,我们将更好地理解线距与串扰之间的关联,并为实际的高速电路设计提供有益的指导。

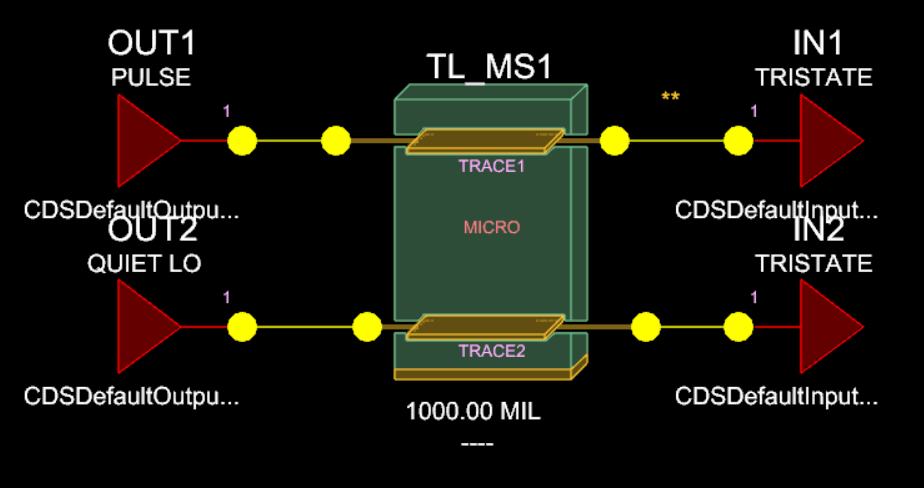

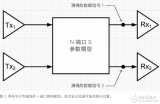

首先搭建一个串扰仿真模型

设置激励信号

我们将激励信号设置为OUT1,使其在0V至3.3V范围内变化。同时,将OUT2设为0V低电平。为了观察串扰现象,我们使用一根长度为1000mil的微带传输线,并对线间距进行5mil、10mil、15mil、20mil和25mil的参数扫描。通过观察IN2端受到的串扰,我们可以深入了解线间距对信号完整性的影响。

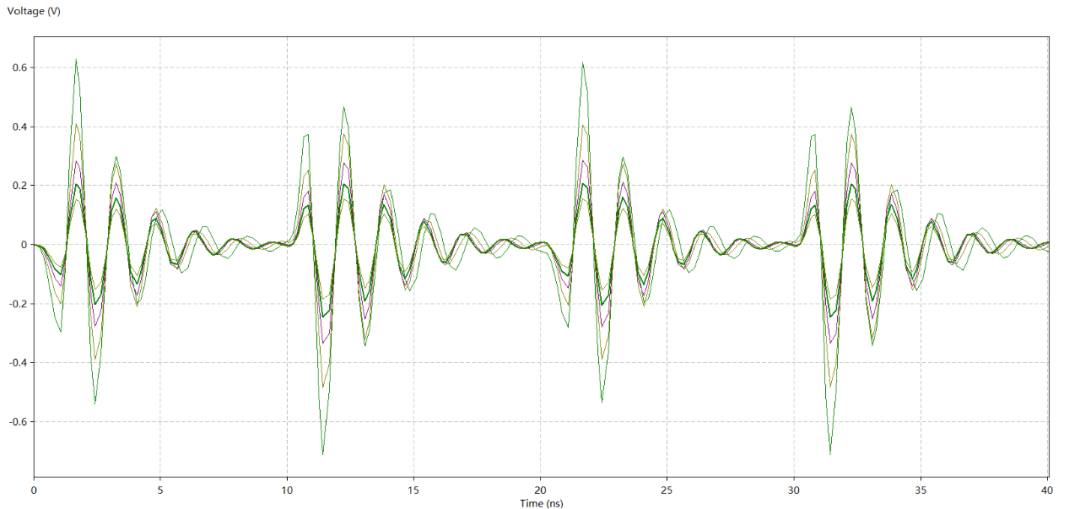

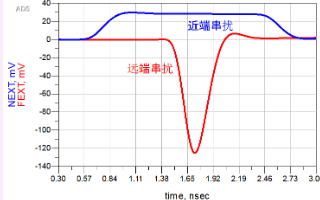

上图展示了IN2接收端的信号波形,为远端串扰波形,整体呈现一个尖峰状态。观察结果显示,随着线间距的增大,耦合在IN2端上的噪声逐渐减小。当线间距为5mil时,串扰噪声最大可达到约0.6V。然而,当线间距增加到25mil时,噪声最大值仅约为0.15V。这表明线间距对串扰具有显著影响,较大的线间距可以有效降低耦合噪声。

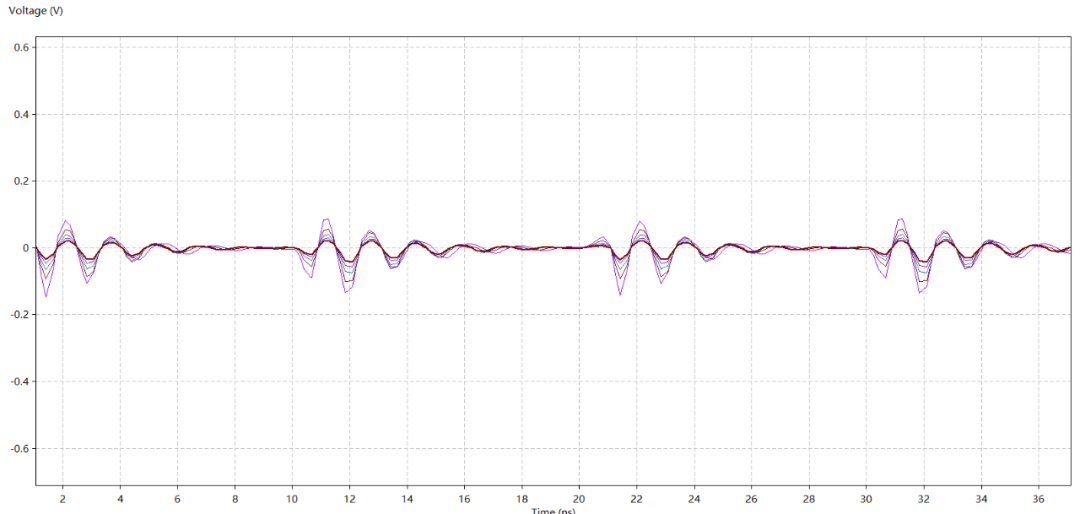

上图展示了OUT2端的信号波形,即近端串扰的情况。观察结果显示,近端串扰的波形幅度相对较小,不像远端串扰那样具有剧烈的跳变。同时,近端串扰与线间距之间也存在关联。当线间距为5mil时,近端串扰的噪声幅度为0.08V;而当线间距增加到25mil时,近端串扰下降至0.02V。这表明线间距对近端串扰也有显著影响,较大的线间距有助于降低耦合噪声。

SigXplorer是Cadence Design Systems开发的一款电磁兼容性(EMC)仿真软件,它主要用于电子系统的电磁干扰和电磁容忍仿真以及信号完整性分析。SigXplorer提供了直观的仿真和分析环境,结合了先进的仿真技术和电磁兼容性知识。它为工程师提供了一个有效的工具,用于优化电子系统的设计和性能,并且可以帮助缩短产品开发周期,提高产品质量。SigXplorer是一款能够提供高精度串扰仿真的工具,具备多种信号传输模型和分层布线分析的能力。它不仅可以帮助工程师预测和解决信号串扰问题,还提供信号完整性分析和优化的功能,为电子系统设计提供了全面的支持。

上述过程是在SigXplorer中实现的仿真过程,目前Sigrity 2021最新版本的最新工具SigrityTopology Explorer不仅具有SigXplorer的拓扑自动提取、仿真与规则管理器集成等功能,还使用了与Sigrity SystemSI相同的模块设计和交互方式,IO model也可以直接使用IBIS模型,大大优化了SigXplorer的使用体验。

-

电路板设计

+关注

关注

1文章

127浏览量

16597 -

仿真

+关注

关注

50文章

4134浏览量

134159 -

电磁

+关注

关注

15文章

1141浏览量

52017

发布评论请先 登录

相关推荐

PCB设计与串扰-真实世界的串扰(下)

使用ADS进行串扰仿真

高速差分过孔产生的串扰情况仿真分析

高速PCB中微带线的串扰分析

选择最简单易用的HyperLynx进行串扰仿真资料下载

如何使用SigXplorer进行串扰的仿真

如何使用SigXplorer进行串扰的仿真

评论