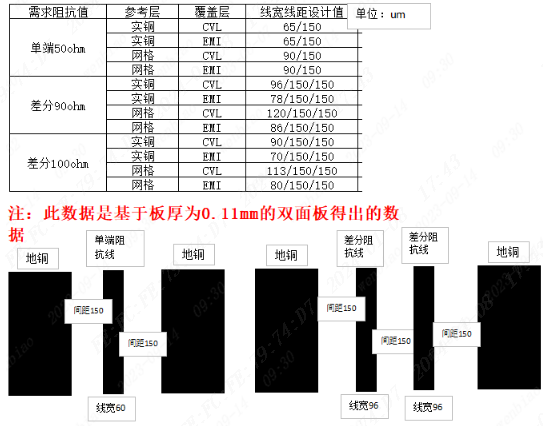

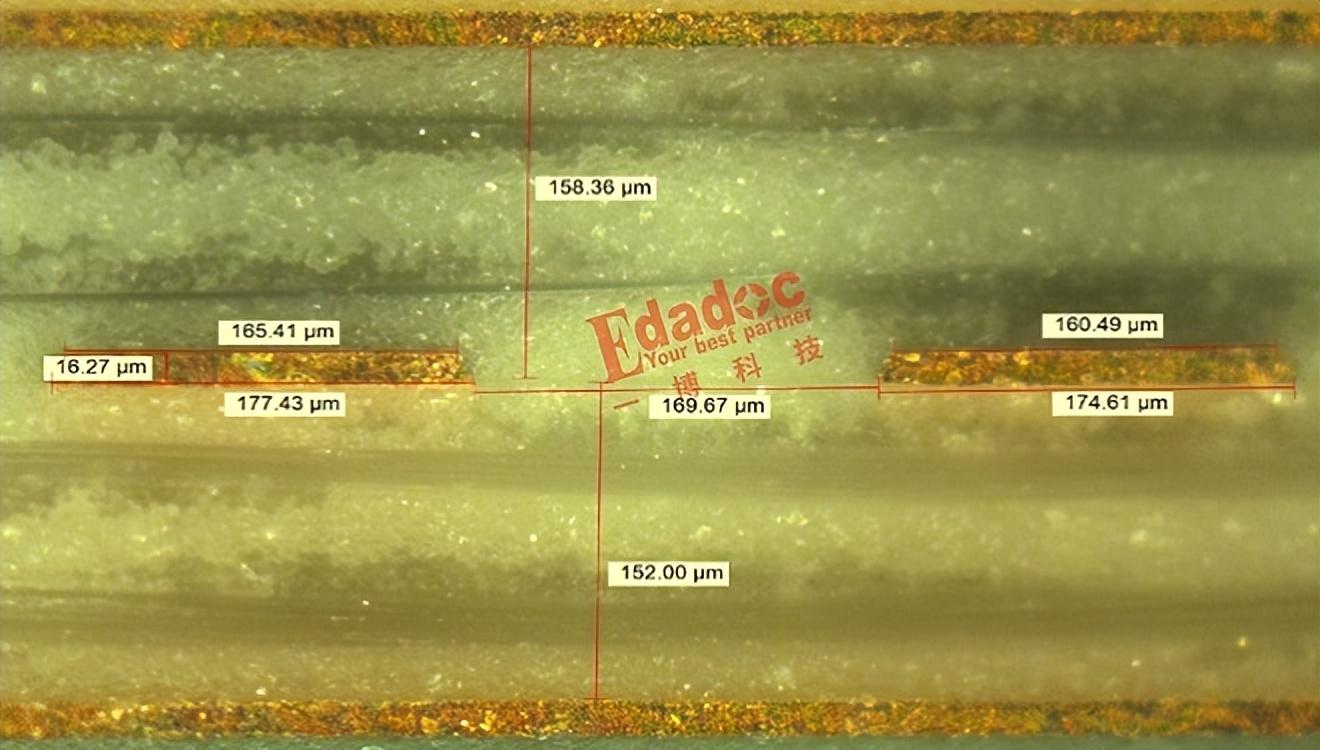

PCB一般板厂用SI9000来计算阻抗,但FPC我用SI9000模拟了几次都不准,刚好*** FPC可以免费打样了,后面就直接打样,用TDR方式测出阻抗,再打切片测量铜厚,基材厚度,线宽线距,反推再修正的方式,整了3次才把阻抗线宽及线距整出来,结果如下:

注:CVL表示只贴了阻焊膜,EMI表示是贴了屏蔽膜的,另外屏蔽膜是接了地的,如果不接地会有影响

以上数据是基于FPC板厚0.11mm,基材PI厚度25um,铜厚12um(成品铜厚15-18um)的,不同基材会有所不同,数据仅供参考,需要打样验证!

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

阻抗

+关注

关注

17文章

962浏览量

46536 -

FPC

+关注

关注

70文章

969浏览量

64183 -

PCB

+关注

关注

1文章

1891浏览量

13204

发布评论请先 登录

相关推荐

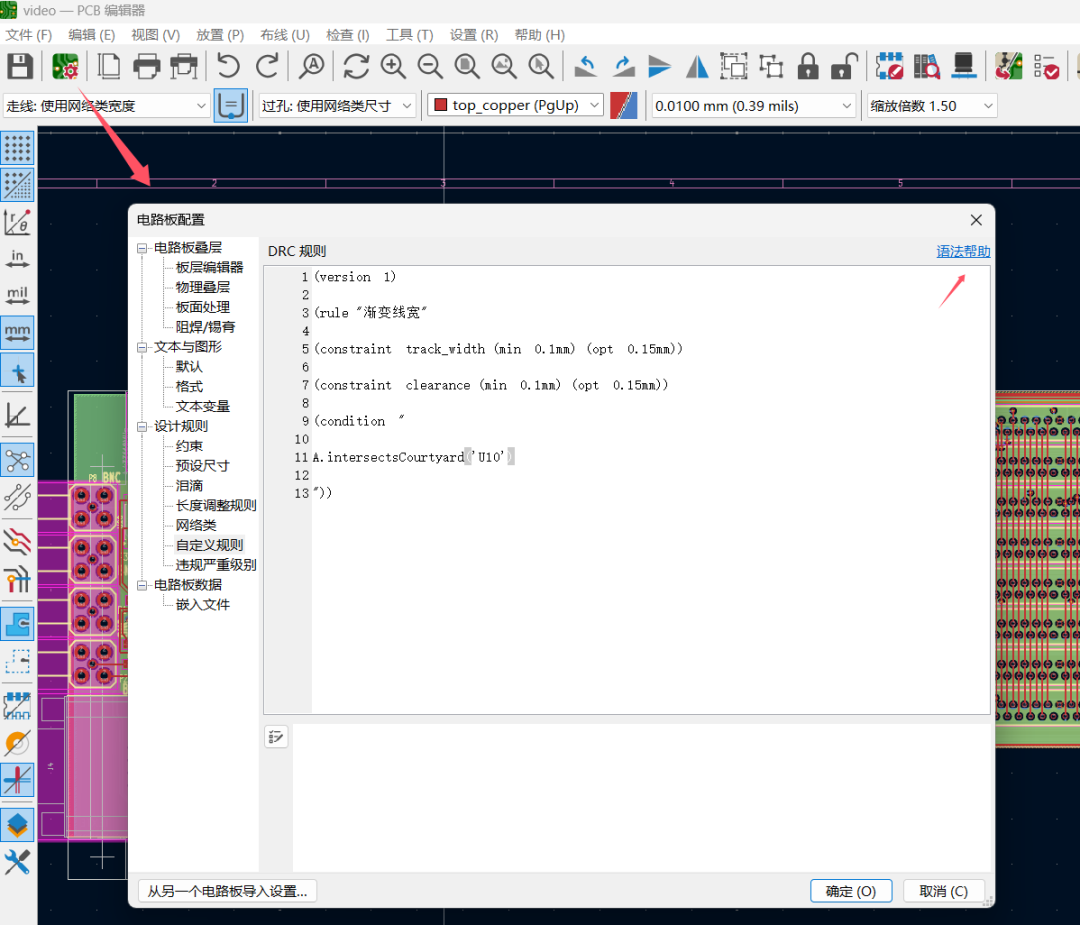

如何在特定区域设置线宽、线距规则

“ 今天偷个懒,分享一个 Hayden 大佬提供的自定义规则,非常实用。可以在特定区域(如BGA器件范围内)定义特殊的线宽、线距规则。 ” 就是下面这段自定义规则,表示 U10

PCB走线,盲目拉线,拉了也是白拉!

布置在阻抗控制层上,须避免其信号跨分割。

2、 布线窜扰控制

a) 3W原则释义

线与线之间的距离保持3倍线宽。是为了减少线间串扰,应保证线间距足够大,如果

发表于 03-06 13:53

从定位到质检:传感器如何重塑FPC裁切与AOI检测的精度边界?

生产效率和产品质量。凭借深厚的技术积累和创新能力,明治针对3C行业设备提出智能升级解决方案,旨在全面提升厂商自动化、智能化水平。↓随着FPC线宽/线距向50μm以

把ADS850的数据接口和时钟信号通过FPC线连接至FPGA,当FPC线缆大于5cm,会导致丢位,错位现象,怎么处理?

之前把ADS850的数据接口和时钟信号通过FPC线连接至FPGA,发现当FPC线缆大于5cm(10cm,12cm,15cm)时,采样值为01 1111 1111 1111到10 0000 000

发表于 02-11 07:27

TUSB8041的阻抗怎么计算?

根据官网给的手册画好了pcb连线的时候,发现USB有些需要差分信号线,但是官网数据手册上只是写了必须设计阻抗在90欧姆左右,并不是很了解怎么计算,希望大佬给点提示,线宽和线

发表于 12-16 06:05

FPC设计与制造流程 FPC与传统PCB的区别

设计与制造的基本流程: 1. 设计阶段 需求分析 :根据产品的功能需求,确定FPC的尺寸、形状、层数等参数。 布局设计 :使用专业的PCB设计软件进行电路布局,包括元器件的放置和电路的走线。 走线设计 :确保电路的电气性能,同时

技术资讯 I 如何使用 Allegro X PCB Editor 优化RF布线和阻抗

走线宽度、走线厚度以及在z轴上将走线与参考平面分隔开的介质高度。信号层下方的连续参考平面对于保持最佳阻抗也至关重要。在同一层上保持适当的走线

ROGERS高频板阻抗设计要求有哪些?

构;需要用到 双芯板结构,保证信号的稳定性,因为芯板中间的介质厚度是稳定的,保证外层阻抗线信号的稳定;下面列举两种常见的高频板阻抗设计叠层,贵司请按如下叠层去计算,设计阻抗

掌握了这个分析方法,实现传输线阻抗5%的加工公差不是梦!

,然后走线就在L2层了。由于板厚比较薄,也就是L2层的上下层介质厚度也很薄,因此我们L2层的线宽自然就设计得很细了。

叠层和L2层的线宽线距

发表于 03-25 18:05

掌握了这个分析方法,实现传输线阻抗5%的加工公差不是梦!

传输线结构很多因素都会影响阻抗,例如线宽、介质厚度、介电常数、铜厚等,那大家有没有想过到底哪个因素最影响阻抗呢?学会了本文的分析方法,或许有一天阻抗

FPC阻抗线宽线距参考

FPC阻抗线宽线距参考

评论