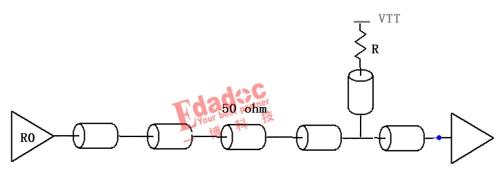

CMOS是一种常见的逻辑门电路,它使用CMOS技术来实现数字逻辑功能。在CMOS电路中,输入端接电阻后接地的情况下,一般情况下是低电平。

首先,让我们先了解一下CMOS电路的基本原理。CMOS(互补金属氧化物半导体)技术利用了两种类型的晶体管:NMOS(负极性金属氧化物半导体)晶体管和PMOS(正极性金属氧化物半导体)晶体管。NMOS晶体管只有有源端施加高电平时才能导通,而PMOS晶体管只有有源端施加低电平时才能导通。这种互补配置使得CMOS电路能够实现高噪声容忍性、低功耗和宽电源电压范围等优点。

在CMOS电路中,输入端接电阻后接地时,电阻和接地构成了一个电路路径。由于接地是一个恒定的低电平,根据CMOS的工作原理,当输入信号不受到其他因素干扰时,输入端将会是低电平。

接下来,让我们更详细地探讨一下为什么输入端会是低电平。

首先,输入端接地是指将输入信号通过电阻连接到接地点。由于接地被视为电路的参考点,其电位为零。因此,在没有任何干扰的情况下,输入端引脚处于接地电位,也就是低电平。另外,由于CMOS电路的输入电阻很高,电流通过电阻非常小,可以近似认为为零。

第二,由于CMOS电路采用了互补设计,NMOS和PMOS晶体管在输入信号的不同电平下有不同的导通状态。在输入端接地的情况下,输入信号为低电平时,NMOS晶体管导通,PMOS晶体管断开。此时,由于NMOS晶体管导通,电流会通过电阻流向接地,从而使得电源电压迫使输入端维持在地电平。因此,输入端接地的情况下,CMOS电路实现了低电平输入。

总结来说,当CMOS电路的输入端接电阻后接地时,一般情况下是低电平。这是因为接地作为电路的参考点,电势为零,而CMOS电路的输入电阻较高,电流通过电阻非常小,可以近似为零。另外,由于互补设计,NMOS晶体管在低电平输入时导通,PMOS晶体管断开,使得电源电压迫使输入端维持在地电平。

然而,需要注意的是,以上是在理想条件下的情况。实际上,电路中会存在一些因素,如电源噪声、母线电阻等,可能导致输入端不完全维持在地电平,因此在设计和实际应用中需要考虑这些因素。

-

CMOS

+关注

关注

58文章

5727浏览量

235754 -

电阻

+关注

关注

86文章

5535浏览量

172360 -

晶体管

+关注

关注

77文章

9708浏览量

138565 -

低电平

+关注

关注

1文章

115浏览量

13305

发布评论请先 登录

相关推荐

cmos输入端接电阻后接地是低电平吗

cmos输入端接电阻后接地是低电平吗

评论