1.前言

在数字电路中,逻辑输出有两个正常态:低电平状态(对应逻辑0)和高电平状态(对应逻辑1)。此外,电路还有不属于0和1状态的高阻态,高阻态常用字母 Z 表示。

高阻态可做开路理解。可以把它看作输出(输入)电阻非常大,它的极限状态可以认为悬空(开路)。也就是说理论上高阻态不是悬空,它是对地或对电源电阻极大的状态。而实际应用上与引脚的悬空几乎是一样的。或者可以理解为输出与电路是断开的。高阻抗状态将器件与电路的其余部分电路隔离。高阻态时引脚对地电阻无穷,此时读引脚电平就可以读到真实的电平值。高阻态的重要作用就是I/O口在用作输入(input)时读入外部电平。

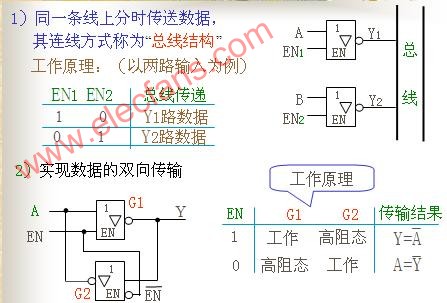

一般门与其它电路的连接,无非是两种状态,0或者1,在比较复杂的系统中,为了能在一条传输线上传送不同的信号,研制了相应的逻辑器件称为三态门。三态门是一种控制开关。

三态门主要是用于总线的连接,因为总线只允许同时只有一个器件使用。通常在数据总线上接有多个器件,每个器件通过OE/CE之类的信号选通。如果器件没有选通的话它就处于高阻态,相当于没有接在总线上,不影响其它器件的工作。三态逻辑门允许许多设备连接到相同的数据线上,例如数据和地址总线。然而,任何时候只有一个设备“连接”,所有其他设备都处于高阻抗状态,因此电气断开。

双向信号本质上是由一个三态门组成,具体细节参见后面的描述。

2. 三态门

2.1示意图、真值表

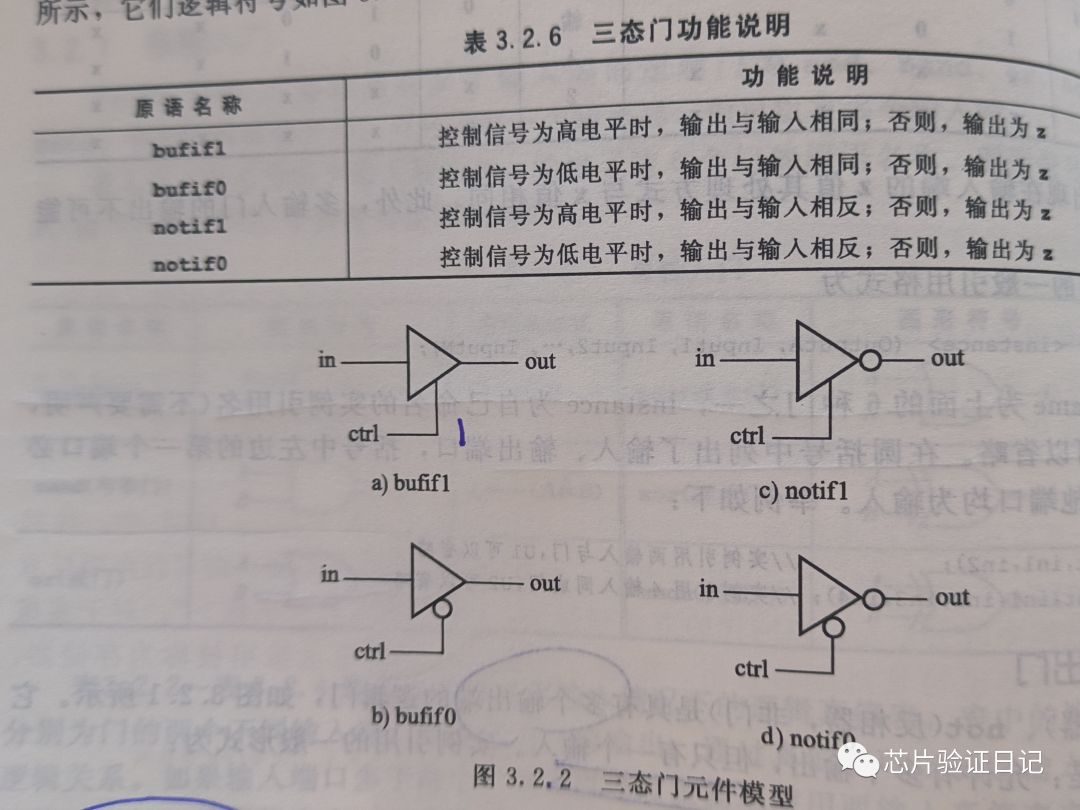

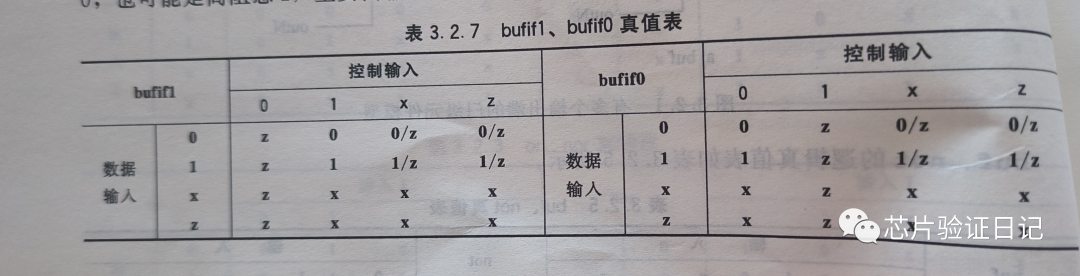

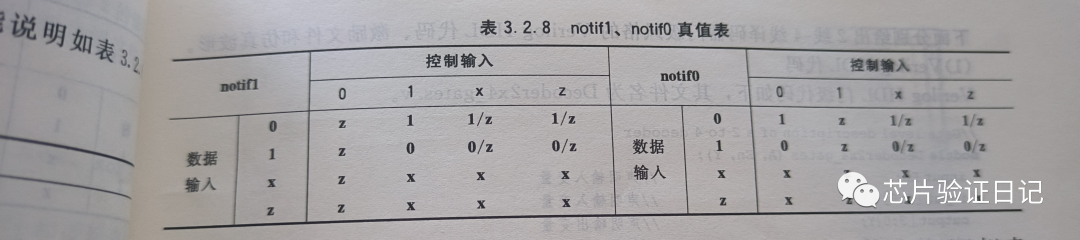

Verilog中有四个元件模型来表示三态门电路,分别是bufif1,bufif0,notif1,notif0。三态门的示意图、真值表分别如下图所示:

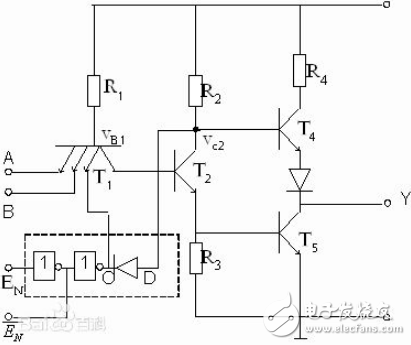

2.2 三态门结构

三态门电路的输出结构和普通门电路的输出结构有很大的不同,因为它在电路中增加了一个输出控制端。

2.2.1 单向三态门

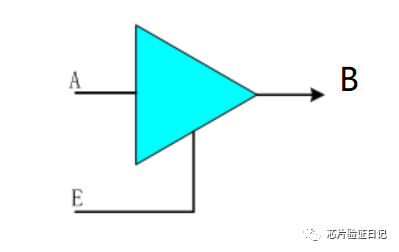

单向三态门的结构示意图如下:

由上图看出,在单向三态门中,当E为高电平时,B与A相连,数据流向是A-->B;而当E为低电平时,B的输出为高阻态,相当于B侧电路与A侧电路之间的连线断开,此时可以从外部向B驱动信号,实现相反方向的数据流向(B-->A)。

2.2.1 双向三态门

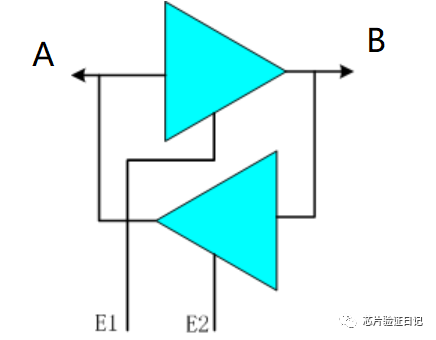

当信号线存在双向IO时,可以有两个三态门来控制,一个控制输出,一个控制输入,双向三态门的结构示意图如下:

当E1=1,E2=0时,双向三态门的电路传输方向是 A -> B;

当E1=0,E2=1时,双向三态门的电路传输方向是 B -> A;

2.3 三态门建模

三态门的RTL建模方式如下所示

//Tristate Buffer moduletristate_buffer(input_x,enable,output_x); inputinput_x; inputenable; output output_x; assign output_x = enable? input_x : 'bz; endmodule

testbench如下:

module tb();

reg r_in_x;

reg w_enable;

wire w_output_x;

initial begin $display("----------------------

Tri-State Buffer

----------------------

");

$monitor("input_x = %b, enable = %b, output_x = %b", r_in_x, w_enable, w_output_x);

// Generation of stimulus

r_in_x = 0; w_enable= 0;

# 10 r_in_x = 0;# 10 r_in_x = 1;

# 10 w_enable = 1;

# 10 r_in_x = 1;

# 10 r_in_x = 0;

end

// Tri-state buffer instantiation

tristate_buffer u_tristate_buffer(

.input_x (r_in_x),

.enable (w_enable),

.output_x (w_output_x));

endmodule

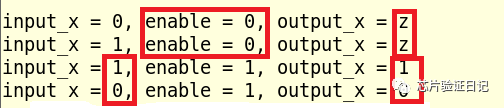

仿真结果

3. 双向信号

在芯片验证的过程中,有时候会遇到双向信号(既能作为输出,也能作为输入的信号叫双向信号)。比如,IIC总线中的SDA信号就是一个双向信号,QSPI Flash的四线操作的时候四根信号线均为双向信号。在Verilog中用关键字inout定义双向信号。

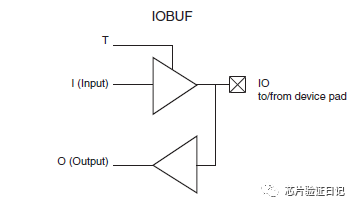

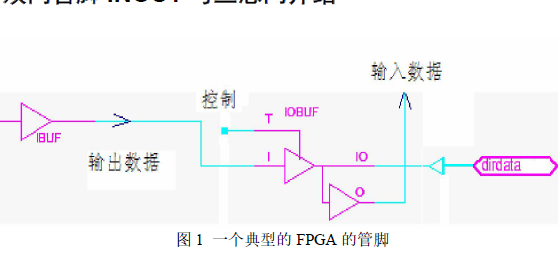

如下图所示,双向信号的本质是由一个三态门组成的,三态门可以输出高电平、低电平和高阻态三种状态,其结构大致如下图所示:

描述这个逻辑的Verilog代码如下:

module inout_top ( input I_data_in , inout IO_data , output O_data_out , input Control ); assign IO_data = Control ? I_data_in : 1‘bz ; assign O_data_out = IO_data ; endmodule

当Control为1时,IO_data为输出,输出I_data_in的值

当Control为0时,IO_data为输入,把输入的信号赋值给O_data_out。

审核编辑:汤梓红

-

Verilog

+关注

关注

28文章

1351浏览量

110077 -

逻辑器件

+关注

关注

0文章

88浏览量

20099 -

三态门

+关注

关注

1文章

34浏览量

18816 -

数字电路

+关注

关注

193文章

1605浏览量

80580

原文标题:Verilog中的三态门与双向信号

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

VERILOG关于三态门

高阻态与三态门的电路原理分析

【梦翼师兄今日分享】 三态门程序设计讲解

三态门逻辑功能的Multisim仿真方案

三态门原理HDL语言DSP和ARM总线的仿真及Modelsim使用教程资料

Verilog中的三态门与双向信号详解

Verilog中的三态门与双向信号详解

评论