芯片内部空间越来越紧凑,新技术有更多发挥空间。

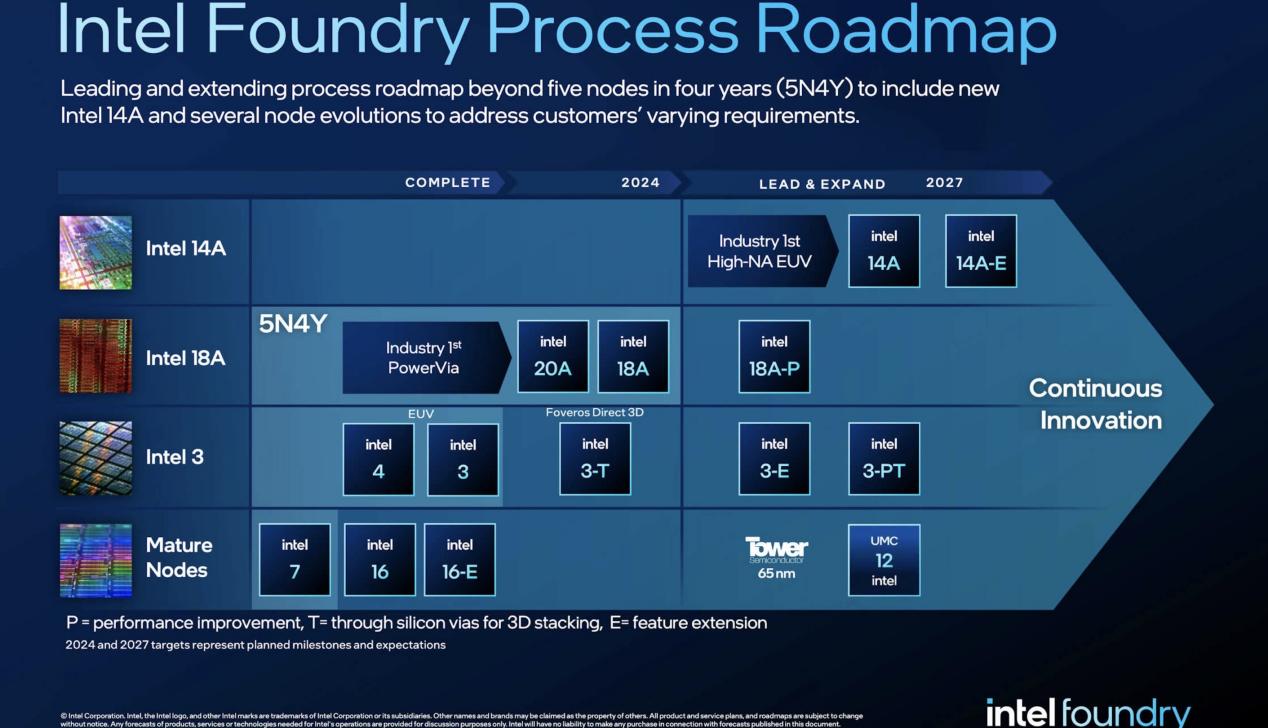

随着晶圆厂应对晶体管小型化的挑战,研究人员正在探索新材料和技术,以提高下一代芯片性能,这是先进半导体技术不断发展领域的一个关键焦点。现在,英特尔正准备通过其背面电源连接提供创新技术,这有助于减少功率损耗并提高器件性能。传统的电力输送在半导体中面临哪些挑战,新的背面电力输送方法如何工作,以及未来设备中还将部署哪些其它方法?

传统的电力输送在半导体中面临哪些挑战?

自60多年前推出第一批器件以来,集成电路经历了许多变化。随着新一代芯片的出现,晶体管都变得更小、更快,这也会消耗更少的功率。

然而,这种晶体管缩放导致更多的组件被集成到同一个空间中,导致整体功耗增加,这是高性能计算中的一个关键问题。这就是为什么 CPU 和 GPU 等高密度器件在每个新系列中逐渐消耗更多功率的原因。现代台式机CPU消耗超过100W的情况并不少见。

应对功耗挑战

深入研究功耗难题,这不仅仅是将更多晶体管集成到芯片中。半导体行业正在向创新材料转变。英特尔进军新型半导体化合物旨在解决导电路径中的固有电阻,这不仅仅是一个技术上的调整,也是朝着重新定义芯片效率和性能迈出的一大步。

虽然在较大的芯片中,高功耗是可控的,允许有效的热量分布和使用大型散热器,但在紧凑的芯片设计中,例如移动设备和物联网应用中使用的芯片,功耗成为一个重大挑战,随着芯片尺寸的减小,此类芯片的热密度如此之大,以至于冷却可能具有挑战性,在某些情况下,需要液体冷却机制。这对于紧凑型设计(如服务器机架)来说也是个问题,因为大型散热器的空间很紧张。

因此,芯片制造商必须尝试识别功耗的来源,并试图彻底消除它们或尽可能降低它们。例如,导电路径的固有电阻会导致少量的能量损失,从而直接产生热量,因此芯片制造商可以尝试减少所用导体的总长度,以及选择电阻较低的材料。

另一种选择是以芯片运行速度为目标,因为动态功耗会随着频率的增加而迅速增加。当然,降低设备速度会直接影响性能,因此,芯片制造商通常会采用低功耗模式,在空闲时关闭性能内核或降低内核速度。

但一个特别难以解决的问题是电力输送。典型的平面器件从有源层开始,包括晶体管结构和掺杂区域。

第一层之后的下一层包括这些晶体管的栅极以及晶体管之间的关键互连,而在此之后的下一层是形成额外互连的第一层金属层。每增加一层,互连的宽度和厚度都会增加,以降低功耗并提高性能。

然而,虽然这种设计方法在过去效果很好,但有一个问题会导致大量的功率损耗:功率走线长度,简而言之,由于电源连接需要从顶层开始,因此,连接到电源轨的每个晶体管都需要在每层之间具有多个过孔,因为电源连接器从顶部开始,一直向下进入第一层。

随着层的变化,连接器宽度的减小会增加电阻损耗,并且使用过孔会看到层之间形成边界,这本身就会引起额外的损耗。这也意味着电源线的散热也会扩散到芯片的其余部分,包括用于处理信号的互连。

纵观现代芯片的分层复杂性,很明显,传统的供电方法正在变得有点像走钢丝。挑战不仅在于管理功率,还在于掌握热管理的艺术。这是一个微妙的平衡。

背面供电

认识到典型平面技术面临的挑战,英特尔展示了其在开发一种新的功率传输机制方面的成就,他们认为这将有助于减少功率损耗,并且对未来的1nm制程节点至关重要。这个新概念被称为“背面电源和直接背面接触”,它与传统设计不同,因为所有电源连接都是从晶圆的底部进行的,而不是在顶部。

这种背面设计的使用意味着电源连接器不需要绕着信号线编织,而是直接连接到晶体管的底部。这不仅大大缩短了电源线的长度,还减少了将电源引入晶体管所需的通孔数量。这种设计还允许电源连接器保持宽而厚,从而减少电阻损耗。

新概念还与直接背面接触配对,该接触将触点暴露在芯片底部,而不是将所有触点带到芯片的顶部。这不仅有助于增加触点密度(因为顶部不再需要电源连接器),而且还有助于分离电源线和信号线,从而提高信号完整性。

还有哪些其它方法?

随着特征尺寸接近亚纳米世界,工程师将需要部署各种独特的解决方案来解决面临的挑战。虽然硅已被证明是一种非常适合现代应用的半导体,但它有可能在不久的将来被其它竞争者所取代。

石墨烯就是这样一种候选者,因为它不仅可以使其具有超导特性,而且可以很容易地产生各种独特的能力,包括形成能够捕获量子计算所需的粒子的复杂3D结构。然而,由于石墨烯很难大规模生产,因此在不久的将来,它远非硅的可行替代品。

展望未来,芯片设计将采用小芯片架构,其中,集成电路封装由多个更小的芯片组成,这一趋势在先进电子制造中越来越受欢迎,这不仅为工程师提供了足够的设计灵活性,还有助于降低功耗。

定制硅器件,如苹果公司展示的器件,也可能变得越来越重要。由于定制硅器件仅集成设计绝对需要的电路,与现成的解决方案相比,它们始终提供最佳的每瓦性能。

审核编辑:刘清

-

半导体

+关注

关注

334文章

27290浏览量

218085 -

晶圆

+关注

关注

52文章

4890浏览量

127931 -

芯片设计

+关注

关注

15文章

1015浏览量

54877 -

散热器

+关注

关注

2文章

1056浏览量

37529 -

晶体管

+关注

关注

77文章

9682浏览量

138080

原文标题:背面供电技术是如何降低芯片功耗的?

文章出处:【微信号:ICViews,微信公众号:半导体产业纵横】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

请问一下背面供电技术是如何降低芯片功耗的?

请问一下背面供电技术是如何降低芯片功耗的?

评论