引言

在过去的几年中,MOSFET结构从平面结构改变为鳍型结构(FinFETs ),这改善了短沟道效应,并导致更高的驱动电流泄漏。然而,随着栅极长度减小到小于20nm,进一步小型化变得越来越困难,因为它需要非常窄的鳍宽度,这导致驱动电流恶化。

在亚纳米工艺中,SiGe有望用于p-FET沟道,而Si仍然作为n-FET的沟道材料,就双沟道结构的各向异性干法刻蚀而言,需要同时刻蚀Si和SiGe。然而,不仅通过卤素化学,而且通过物理溅射,导致SiGe蚀刻速率比Si快。 因此,有必要找到一种蚀刻化学物质来获得相对于SiGe的选择性Si蚀刻。

实验与讨论

在这项研究中,英思特使用日立微波电子回旋共振(M-ECR)系统。在该系统中,源频率和晶片偏置频率分别为2.45 GHz和400 kHz。腔室具有喷淋板,工艺气体通过该喷淋板引入。一个300mm的晶片用静电吸盘固定在电极上,晶片的温度由背面氦冷却系统控制。

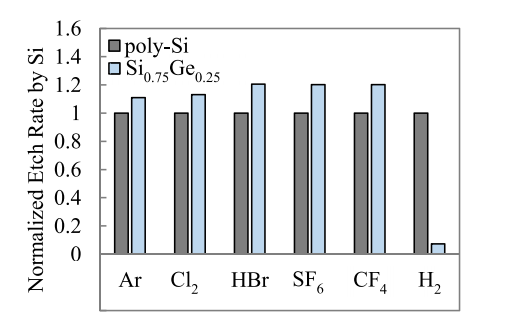

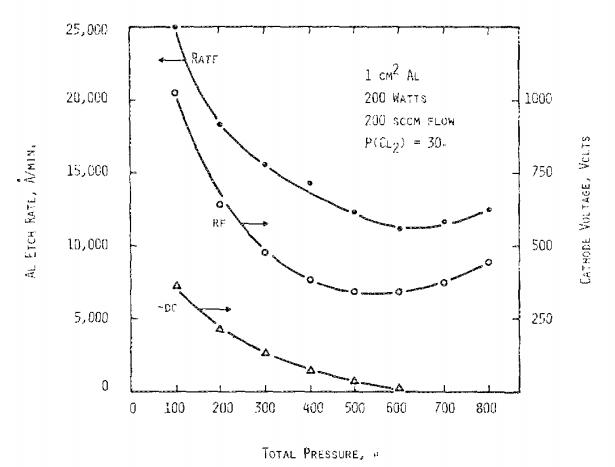

由硅蚀刻速率标准化的硅锗蚀刻速率如图1所示。使用卤素化学等离子体(Cl2、HBr、SF6和CF4),SiGe的蚀刻速率高于Si。甚至通过Ar等离子体的物理溅射显示出比Si蚀刻速率更高的SiGe蚀刻速率。

英思特提出了几个原因来解释Si上的选择性SiGe蚀刻:1、可能是由于Si-Ge (3.12 eV)和Ge-Ge (2.84 eV)的键合能低于Si-Si (3.25 eV),2、可能是由选择性去除高应变层以稳定系统引起的,因为在Si上外延生长的SiGe由于晶格失配而发生应变。 3、是因为SiGe的带隙较窄,电子效应可能导致SiGe蚀刻的化学反应增强。

图1:不同等离子体的SiGe蚀刻速率

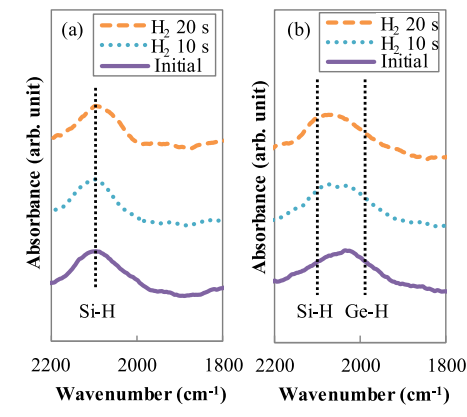

图1:不同等离子体的SiGe蚀刻速率为了了解Si-SiGe的蚀刻机理,我们研究了ATR-FTIR氢等离子体暴露后的Si和Si0.5Ge0.5。.图2为氢等离子体暴露10 s和20 s后Si和SiGe的吸光谱。对于图2(a)所示的Si表面,在氢等离子体暴露10s和20s后没有变化。

另一方面,对于图2 (b)所示的SiGe表面,在初始样品中发现Ge-H键和Si-H键之间存在宽峰。随着氢等离子体暴露时间的增加,峰值向Si-H方向移动,这意味着Si-H键被选择性地在Ge-H键上产生。

图2:(a) Si和(b) SiGe暴露于氢等离子体中10和20 s的吸光度光谱

图2:(a) Si和(b) SiGe暴露于氢等离子体中10和20 s的吸光度光谱结论

在本研究中,英思特研究了硅蚀刻控制在硅双通道鳍图案的应用。结果表明,不仅卤素化学性质和物理溅射蚀刻SiGe对硅有选择性,而氢等离子体蚀刻硅对SiGe也有选择性。这是因为SiH键的形成在能量上有利于Ge-H键的形成,即表面Ge会阻止蚀刻副产物的形成。

英思特还通过提出了一个离子能量沉积模型来解释蚀刻速率随着离子能量的增加而降低的现象。我们利用所开发的蚀刻化学方法,将Si和SiGe鳍的CDs和蚀刻深度的差异从正值控制到负值。在此研究中,我们还表明,该低温氢等离子体在SiGe表面会诱导硅偏析。

审核编辑 黄宇

-

等离子体

+关注

关注

0文章

147浏览量

15295 -

光纤

+关注

关注

20文章

4464浏览量

81074 -

SiGe

+关注

关注

0文章

99浏览量

24665 -

蚀刻

+关注

关注

10文章

431浏览量

16689

发布评论请先 登录

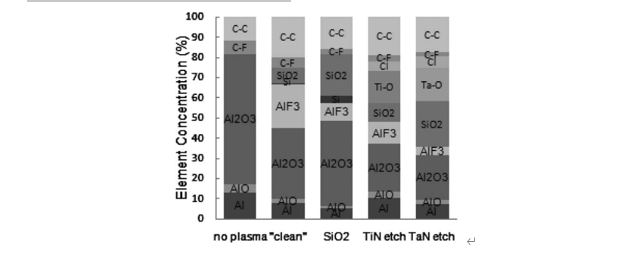

金属蚀刻残留物对对等离子体成分和均匀性的影响

等离子体蚀刻和沉积问题的解决方案

PCB多层板等离子体处理技术

PCB电路板等离子体切割机蚀孔工艺技术

PCB板制作工艺中的等离子体加工技术

低温等离子体废气处理系统

TDK|低温等离子体技术的应用

等离子体应用

大气压低温等离子体的研究

低温等离子体气体温度参数研究

低温等离子体处理废气

低温等离子体发生器的应用资料说明

低温等离子体技术的应用

硅双通道光纤低温等离子体蚀刻控制与SiGe表面成分调制

硅双通道光纤低温等离子体蚀刻控制与SiGe表面成分调制

评论