FPGA算法是指在FPGA(现场可编程门阵列)上实现的算法。FPGA是一种可重构的硬件设备,可以通过配置和编程实现各种不同的功能和算法,而不需要进行硬件电路的修改。

FPGA算法可以包括各种不同的计算和处理任务,例如数字信号处理(DSP)、图像处理、机器学习、通信协议处理等。FPGA的特点使得它非常适合实现需要高度并行计算和低延迟的算法。

实现FPGA算法的过程通常涉及以下几个方面:

1. 硬件描述语言(HDL)编写:使用硬件描述语言(如VHDL或Verilog)来描述算法的硬件结构和计算逻辑。

2. 综合和优化:使用综合工具将HDL代码转换为FPGA的可编程逻辑块和数字信号处理块。通过优化和资源利用率的考虑,提高算法的性能和效率。

3. 约束与布局:应用约束以满足时序、时钟频率和信号完整性的要求,并使用布局工具进行物理布局以最小化信号传输的路径。

4. 下载与调试:将设计下载到FPGA设备中,利用开发板支持工具进行功能验证和性能调试。

FPGA算法的优点在于它们可以提供高度的定制化和灵活性,使得算法可以根据实际需求进行优化和调整。此外,FPGA还可以实现硬件加速,提供比传统处理器更高的计算性能和吞吐量。因此,FPGA算法在许多领域中被广泛应用,包括嵌入式系统、高性能计算和实时信号处理等。

怎么用FPGA做算法

使用FPGA(现场可编程门阵列)来实现算法是一种常见的方法,它可以提供高效的硬件加速和灵活的算法设计。下面是一般的步骤来用FPGA实现算法:

1. 算法设计与验证:首先,你需要根据你的需求来设计算法。这包括确定输入和输出的数据格式、算法的处理步骤和计算流程等。你还可以使用软件工具如MATLAB或Python等进行算法验证,以确保其正确性和效果。

2. 硬件描述语言(HDL)编写:使用硬件描述语言如VHDL或Verilog,将算法转换成可在FPGA上实现的硬件描述。通过将算法进行逻辑门级的建模,你可以描述算法的功能和计算结构。

3. 综合和优化:使用综合工具,将HDL代码转换为对应 FPGA 的可编程逻辑块(PL)和数字信号处理(DSP)块。在综合期间,你可以选择各种优化选项,以提高资源利用率和性能。

4. 约束与布局:在 FPGA 上实现算法时,你需要考虑电路的物理限制。为了确保正确的时序和信号完整性,你需要应用各种约束,如时钟频率、I/O 路由和时序调整等。布局工具可以帮助你对设计进行布局,以使信号传输的路径最短。

5. 时序分析与时序约束:在算法实现的过程中,你需要进行时序分析以验证设计是否满足时序要求。通过应用时序约束,你可以确保数据在正确的时间窗口内被传输和处理。

6. 下载与调试:当你完成 FPGA 的编程和配置后,将设计下载到 FPGA 开发板中。使用相应的开发板支持工具,你可以进行功能和性能的调试和验证。

如何在FPGA上实现最大公约数算法

如何在FPGA上实现最大公约数算法,简单介绍在FPGA上实现算法的基本思想。希望通过本文的介绍,让各位朋友管中窥豹,初步形成如何用FPGA实现算法的基本概念。

辗转相除法是求解两个数的最大公约数最常用的方法,例如,计算a=1071和b=462的最大公约数的过程如下:

用1071除以462得到余数为147:1071 mod 462 = 147

用462除以147得到余数为21:462 mod 147 = 21

用147除以21得到余数为0:147 mod 21 = 0

此时余数为0,所以1071和462的最大公约数为21。

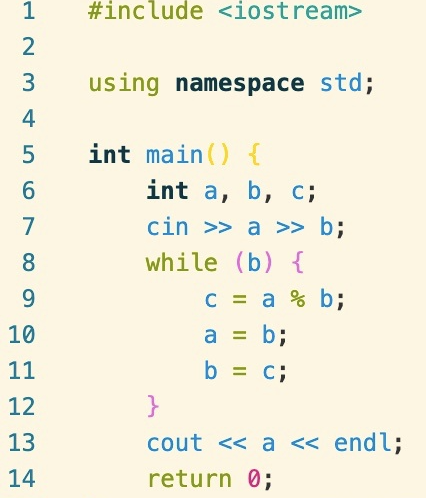

下图是该过程的C++实现,输入a和b,当b不为0时,不断进行上述过程直到b为0,此时a为最大公约数。各位同学有兴趣可以自行仿真上述代码并通过单步调试观察中间过程。

辗转相除法求最大公约数的实现

在验证算法的正确性后,可以进入算法实现阶段。在FPGA上实现该算法主要有以下两个步骤,首先需要优化算法,使算法更容易在硬件上实现。之后便是将算法模型转化为RTL模型,并用硬件描述语言将模型描述出来。下面分别介绍这两个步骤。

算法优化

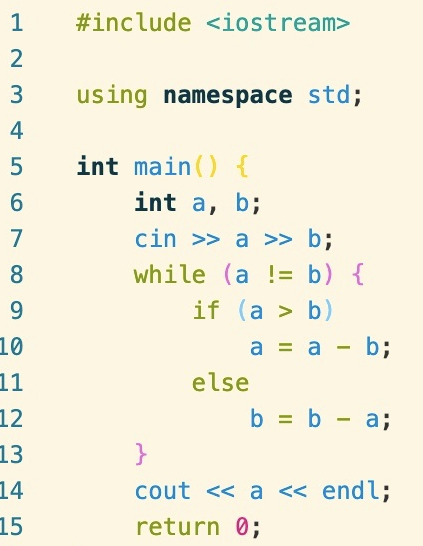

在上述过程中,存在使用除法求余数的步骤。用硬件实现除法开销较大,一般情况下会考虑将除法替换为其它运算操作。由于除法和减法之间存在等价关系,除法取余数本质上是不断做减法直到被除数小于除数。在这里可以首先考虑将该使用减法实现求余操作,可以使用以下方式实现辗转相除法:

使用减法实现求余操作

当a大于b时不断用a减去b,最后a的结果就是a mod b。当a小于b时则不断用b减去a,最后a的结果就是a mod b。当a等于b时,此时无论是a mod b还是b mod a都为0,因此,此时a的值即为a与b的最大公约数。

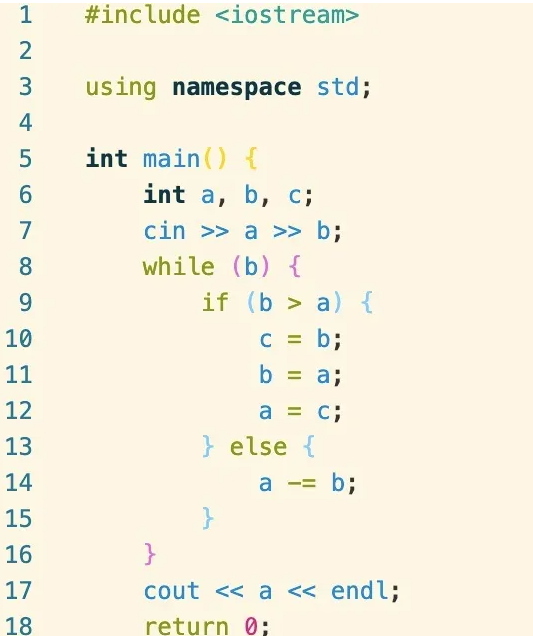

修改后的算法用减法实现取模操作,降低了硬件实现的开销。但是取模操作始终是用大的数去减小的数得到余数,因此并不需要两个减法器。如果规定a为a和b中的大数,每次取模运算都都求a mod b的值,则只需要使用到一个减法器。但这需要一个判断的步骤,在a小于b时交换a和b的值,以维护a始终大于b这一关系。按照这种思路可以写出如下代码:

用于最终实现的版本

在以上代码中,当b大于a时交换a和b,确保a永远是两个数中较大的那个数。否则不断用a减去b得到a mod b,直到b为0,此时a的值即为a和b的最大公约数。至此,我们将算法优化为更易于硬件实现的版本:首先将取模使用减法实现,再减少减法器的数量,得到了用于最终实现的版本。

简要总结一下,优化算法的目标有以下几点:

1. 减少硬件开销

2. 提高吞吐率,降低延迟

3. 降低系统功耗

而要实现这些目标主要可以考虑以下优化方向:

1. 将复杂的计算模块用简单的替换,比如使用减法算余数,但可能会带来计算时间的增加

2. 通过量化等方法减少数据位宽

3. 提高系统的并行度,增加数据处理的并发性

4. 调整计算顺序,优化计算过程以更符合硬件结构

在算法优化完成以后,下一步便是设计合适的硬件结构。

-

FPGA

+关注

关注

1634文章

21827浏览量

607855 -

算法

+关注

关注

23文章

4641浏览量

93654 -

可编程逻辑

+关注

关注

7文章

517浏览量

44276

原文标题:怎么用FPGA做算法 如何在FPGA上实现最大公约数算法

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA上的图像处理算法集成与优化

FPGA做深度学习能走多远?

为什么FPGA属于硬件,还需要搞算法?

【招聘】verilog vhdl FPGA

如何在FPGA中实现状态机

如何在FPGA上实现神经网络

基于FPGA的网络加速设计实现

怎么用FPGA做算法 如何在FPGA上实现最大公约数算法

怎么用FPGA做算法 如何在FPGA上实现最大公约数算法

评论