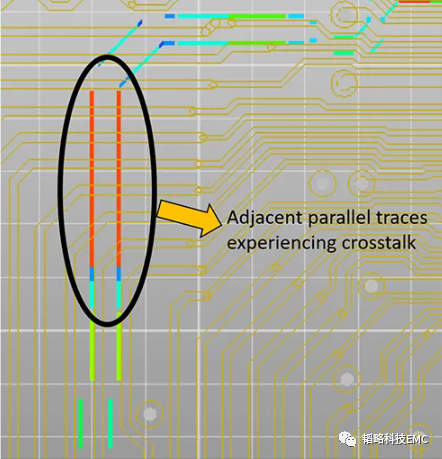

在PCB设计过程中,串扰(Crosstalk)是一个需要重点关注的问题,因为它会导致信号质量下降,甚至可能导致数据丢失。本文将详细介绍PCB中的串扰机制。

耦合是指两条信号线之间的磁场和电场相互作用,导致信号线之间的能量交换。当一条信号线上的电流变化时,会产生一个磁场,这个磁场会感应到另一条信号线上,导致另一条信号线上的电流发生变化。同样,当一条信号线上的电压变化时,会产生一个电场,这个电场也会感应到另一条信号线上,导致另一条信号线上的电压发生变化。

电容耦合

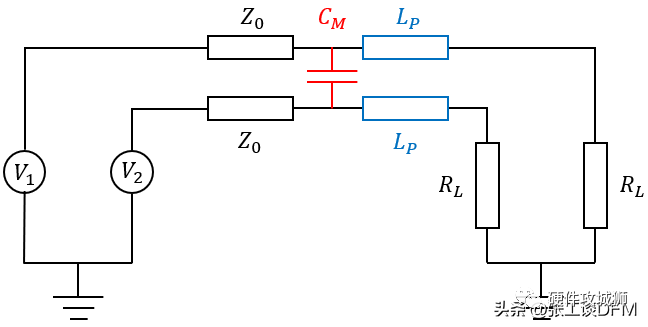

下图展示了如何利用电路理论来模拟不同类型串扰的情况。在这个图中,两条迹线之间存在一些寄生电容,这是由于迹线之间的宽边耦合而产生的。由于每条迹线都是一个导体环路,因此每条迹线都像一个电感器,并具有一些寄生电感。两个并联电感具有一定的互感,它决定了两条走线之间的电感耦合强度。

电容耦合不仅表示显示由走线边缘产生的等效电容,尽管这确实有助于互电容的计算。每条迹线的本机电容和宽边电容共同决定了总互电容。它们全部串联,并与地平面相互耦合。

容性耦合

容性耦合是指两条信号线之间的电容效应导致的串扰现象。当一条信号线上的电压变化时,会在两条信号线之间产生一个电场,这个电场会改变另一条信号线上的电荷分布。这种电荷分布的变化会导致另一条信号线上的电压发生变化。这种容性耦合也会导致串扰现象的发生。

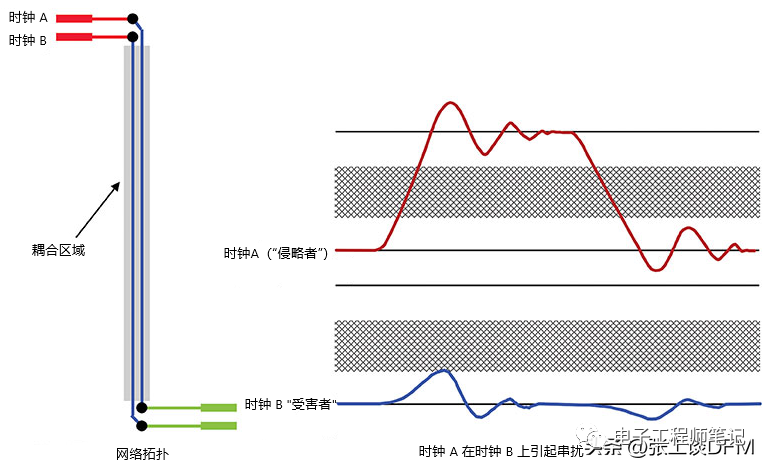

前向和后向串扰

实际上,在受害网络上叠加了两个耦合信号:一个前向信号和一个后向信号。前向脉冲与干扰信号一起传播,而后向脉冲则从干扰信号返回。位于受害远端的串扰被称为“远端串扰”或FEXT,而位于近端的耦合电压则称为“近端串扰”(NEXT)。

-

电容

+关注

关注

100文章

6111浏览量

151656 -

串扰

+关注

关注

4文章

189浏览量

27063 -

PCB

+关注

关注

1文章

1855浏览量

13204

发布评论请先 登录

相关推荐

高速PCB设计中的串扰分析与控制

高速PCB中微带线的串扰分析

pcb中的串扰机制是什么

pcb中的串扰机制是什么

评论