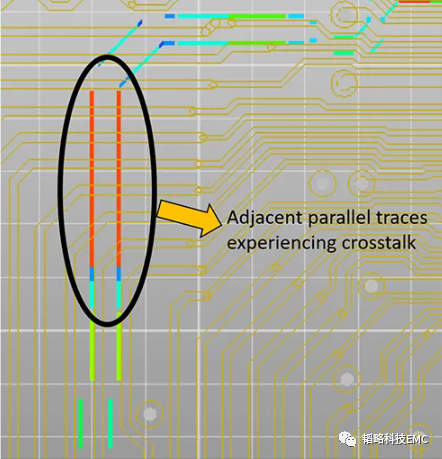

串扰是PCB(Printed Circuit Board)中走线之间产生的不需要的噪声(电磁耦合)。串扰会对时钟信号、周期和控制信号、数据传输线以及I/O产生不利影响。串扰无法完全消除,但可以通过一些方法尽量降低串扰的影响。那么减少串扰的方法有哪些呢?

检查靠近 I/O 网络的关键网络

检查与I/O线相关的关键网络的布线非常重要,因为这些线容易产生噪声,这些噪声可能会通过它们离开或进入电路板并与PCB连接,从而耦合到电路板内部或外部的世界,以及其他系统中的PCB或模块。

合理布局

合理的布局是减少串扰的关键。首先,尽量使高速、高频的信号线远离低速、低频的信号线,以减小电磁耦合和电容耦合的影响。其次,尽量使信号线之间的平行距离保持较大,以减小互感耦合的影响。此外,还可以采用地平面和屏蔽层来减小串扰的影响。

使用屏蔽层

在PCB上添加屏蔽层可以有效地减小电磁辐射和电磁耦合的影响。屏蔽层可以是金属箔、金属网格或者导电材料。屏蔽层应尽量覆盖整个PCB,以减小电磁辐射的影响。同时,屏蔽层应与地平面连接,以提供良好的接地效果。

保持相邻层的走线垂直

应配置PCB层,使穿过相邻层的信号具有相互垂直的方向,以避免它们的走线平行。

使用接地层

在两个相邻信号层之间放置接地层(或电源层)是推荐的做法,因为它可以进一步减少邻近耦合的可能性。这个解决方案有两个优点:增加了层之间的距离,并为信号层提供了更好的地线回流路径。

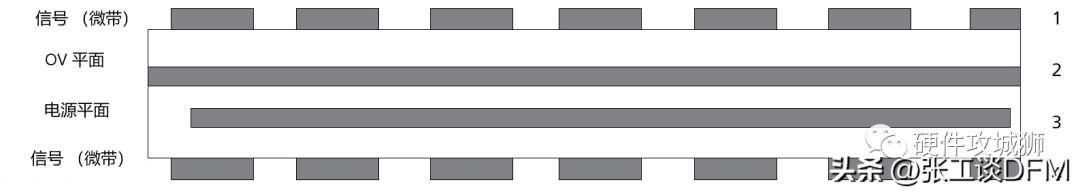

在下面的图示中,我们可以看到一个典型的四层PCB,它具有两个外部信号层,一个内部层用于接地(0V),以及一个内部层用于电源。

- 采用差分信号传输

差分信号传输是一种有效的抗干扰和抗串扰的信号传输方式。差分信号传输是指将信号分为两路,分别沿着两条平行的信号线传输。由于两路信号的极性相反,所以当外界干扰或串扰发生时,两路信号的变化趋势相同,从而抵消了干扰和串扰的影响。差分信号传输可以有效地提高信号的传输质量,减小串扰的影响。

-

电磁

+关注

关注

15文章

1141浏览量

52010 -

串扰

+关注

关注

4文章

189浏览量

27021 -

PCB

+关注

关注

1文章

1832浏览量

13204

发布评论请先 登录

相关推荐

什么是串扰?如何减少串扰?

减少串扰的方法有哪些

减少串扰的方法有哪些

评论