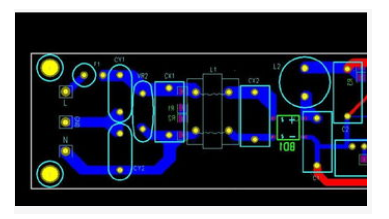

PCB产生串扰的原因及解决方法

PCB(印刷电路板)是电子产品中非常重要的组成部分,它连接着各种电子元件,并提供电气连接和机械支撑。在 PCB 设计和制造过程中,串扰是一个常见的问题,它可能会对电路性能产生负面影响。本文将详细介绍 PCB 产生串扰的原因,并提供一些解决方法。

一、串扰的原因

1. 电磁干扰(EMI)

电子设备在工作过程中会产生电磁辐射,信号线上的电流和电压变化会产生磁场,导致附近线路上的电荷和电流发生变化,从而产生串扰。电磁干扰主要源于高频信号、地面回流和电源回流。

2. 信号完整性(SI)

信号完整性是指信号在电路中传输时保持稳定性和准确性的能力。当信号在 PCB 中传输时受到阻抗不匹配、信号耦合和回流等因素的影响,会导致信号变形和串扰。

3. 电源噪声

电源噪声是指由于电源电压波动、电源线阻抗不匹配以及其他电气因素引起的电压和电流的变化。电源噪声可以通过电源线耦合到其他线路上,导致串扰。

4. 异步时钟系统

当 PCB 上有多个时钟源时,由于各个时钟源的频率和相位可能不同,会导致信号之间的相互干扰,产生串扰。

二、解决方法

1. 电磁屏蔽

为了减少电磁辐射和电磁干扰,可以在 PCB 上采用电磁屏蔽措施。例如,在高频线路旁边添加地面线、电源线或电磁屏蔽罩,以减少干扰的程度。

2. 合理布线和布局

合理的布线和布局可以减少信号的耦合和串扰。首先,应尽量减少信号线的长度和面积,避免信号线的交叉和重叠。其次,应避免将高频和低频线路放在相同的层次上,以及避免将信号线和电源线放在相邻位置。

3. 阻抗匹配

为了保证信号完整性,应在 PCB 设计中进行阻抗匹配。在信号线的末端添加阻抗匹配电阻,以确保信号的正常传输。此外,还可以使用 PCB 软件模拟工具进行阻抗匹配的优化。

4. 优化电源设计

优化电源设计可以减少电源噪声对其他线路的影响。首先,应尽量减少电源线的长度和阻抗。其次,应在 PCB 上添加电源过滤电容、电源稳压器和电源隔离器等元件,以降低电源噪声。

5. 同步时钟系统

为了避免异步时钟系统的串扰问题,可以采用同步时钟系统。同步时钟系统可以通过时钟信号的同步控制来保证各个时钟源的频率和相位的一致性,减少串扰。

以上是关于 PCB 产生串扰的原因及解决方法的详细介绍。通过合理的设计和优化措施,可以有效减少串扰问题,提高 PCB 的工作性能和可靠性。然而,在实际应用中,不同的电子设备和电路系统可能存在不同的串扰问题,解决方法也会有所差异。因此,在 PCB 设计和制造过程中,需要根据具体情况综合考虑,灵活应用各种措施,以最佳方式解决串扰问题。

-

pcb

+关注

关注

4318文章

23076浏览量

397402 -

信号完整性

+关注

关注

68文章

1404浏览量

95454 -

电磁干扰

+关注

关注

36文章

2312浏览量

105390

发布评论请先 登录

相关推荐

串扰产生的原因是什么

PCB焊盘脱落的原因及解决方法?

如何使用SigXplorer进行串扰的仿真

怎么样抑制PCB设计中的串扰

PCB产生串扰的原因及解决方法

PCB产生串扰的原因及解决方法

评论