审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

通信测试

+关注

关注

0文章

58浏览量

49535 -

PCIe

+关注

关注

15文章

1258浏览量

83063 -

5G

+关注

关注

1356文章

48503浏览量

565680 -

创龙科技

+关注

关注

2文章

132浏览量

7774 -

RK3566

+关注

关注

0文章

148浏览量

4971

发布评论请先 登录

相关推荐

RK3568内置MCU开发介绍之一

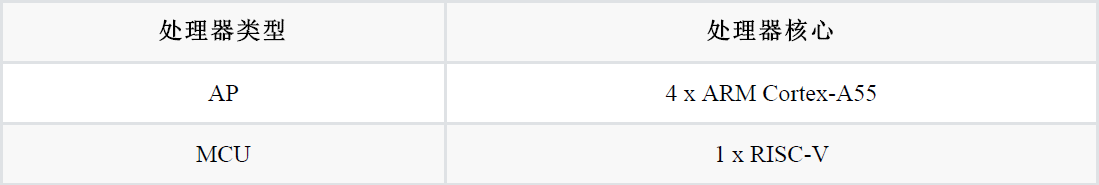

本文介绍RK3568内置的MCU的开发流程,首先介绍MCU程序的构建方法,然后介绍MCU核心与ARM CORTEX A55 AP核心之间的mailbox通信。 RK3568内置有4*cortex

迅为RK3568驱动指南|如何在Linux中使用模拟SPI

SATA/PCIE/USB3.0外围接口。RK3568内置独立NPU,可用于轻量级人工智能应用。RK3568支持安卓11和linux系统,主要面向物联网网关、NVR存

迅为RK3568开发板使用手册目录了解

各个应用场合。

底板分为连接器与邮票孔两种版本,双路千兆以太网、SATA3.0、PCIE3.0、MIPI、HDM、MIPI、CAMERA、4G、5G等接口一应俱全.

发表于 08-01 11:08

3568F-FPGA案例开发手册

元器件数量占比,数据仅供参考)。

核心板内部RK3568J/RK3568B2与Logos-2通过PCIe 2.0、FSPI、I2C、GPIO连接,经过专业的PCB Layout和高低温测试

发表于 07-25 15:35

3568F-MQTT通信协议案例

元器件数量占比,数据仅供参考)。

核心板内部RK3568J/RK3568B2与Logos-2通过PCIe 2.0、FSPI、I2C、GPIO连接,经过专业的PCB Layout和高低温测试

发表于 07-25 15:27

3568F-基于PTP的时钟同步测试手册

元器件数量占比,数据仅供参考)。

核心板内部RK3568J/RK3568B2与Logos-2通过PCIe 2.0、FSPI、I2C、GPIO连接,经过专业的PCB Layout和高低温测试

发表于 07-25 15:24

3568F-NPU开发案例

元器件数量占比,数据仅供参考)。

核心板内部RK3568J/RK3568B2与Logos-2通过PCIe 2.0、FSPI、I2C、GPIO连接,经过专业的PCB Layout和高低温测试

发表于 07-25 15:15

3568F-ARM+FPGA通信案例开发手册

元器件数量占比,数据仅供参考)。

核心板内部RK3568J/RK3568B2与Logos-2通过PCIe 2.0、FSPI、I2C、GPIO连接,经过专业的PCB Layout和高低温测试

发表于 07-25 15:12

3568F-Linux-RT系统测试手册

元器件数量占比,数据仅供参考)。

核心板内部RK3568J/RK3568B2与Logos-2通过PCIe 2.0、FSPI、I2C、GPIO连接,经过专业的PCB Layout和高低温测试

发表于 07-25 14:41

3568F-评估板测试手册(ARM端)

元器件数量占比,数据仅供参考)。

核心板内部RK3568J/RK3568B2与Logos-2通过PCIe 2.0、FSPI、I2C、GPIO连接,经过专业的PCB Layout和高低温测试

发表于 07-17 11:27

迅为RK3568手册上新 | RK3568开发板NPU例程测试

iTOP -RK3568开发板使用手册上新,后续资料会不断更新,不断完善,帮助用户快速入门,大大提升研发速度。

本次新增《itop-3568开发板NPU例程测试手册》是NPU视频教程的

发表于 07-12 14:44

全国产RK3568J + FPGA的PCIe、FSPI通信实测数据分享!

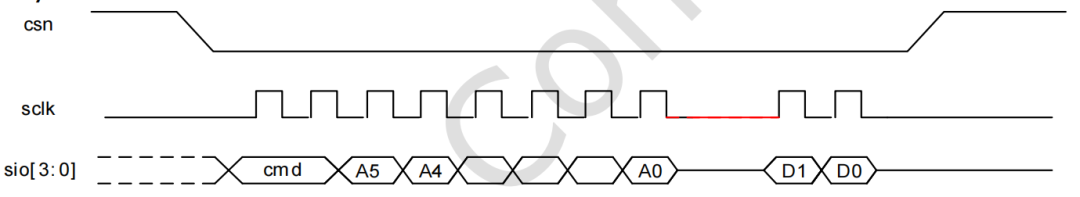

Interface)是一种高速、 全双工 、同步的串行通信总线,在RK3568J处理器中就有FSPI控制器,可用来连接FSPI设备。

基于HD-RK3568-CORE设计的HD-RK3568-OPS主板上新!

HD-RK3568-OPS主板基于HD-RK3568-CORE 工业级核心板设计,支持标准OPS接口,具有即插即用、操作简单的特点,适用于数字标牌、自助终端、教育一体机等应用场景。

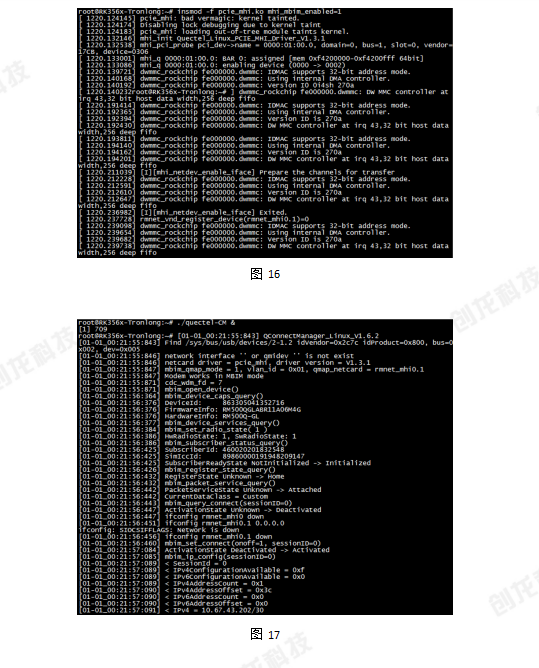

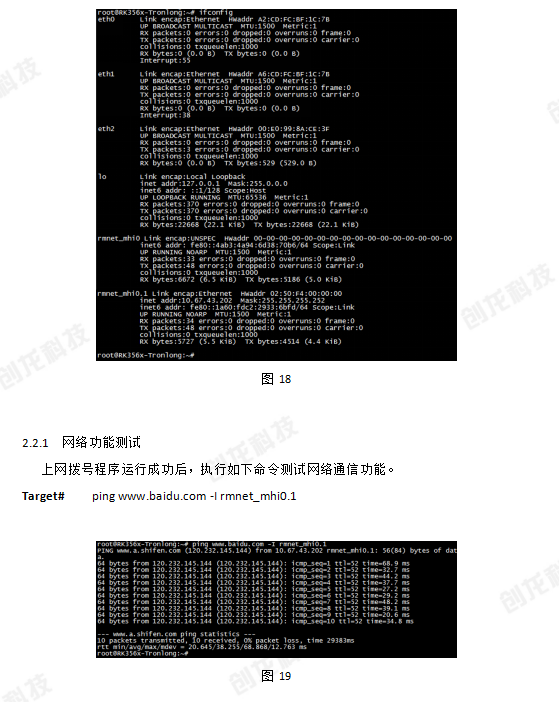

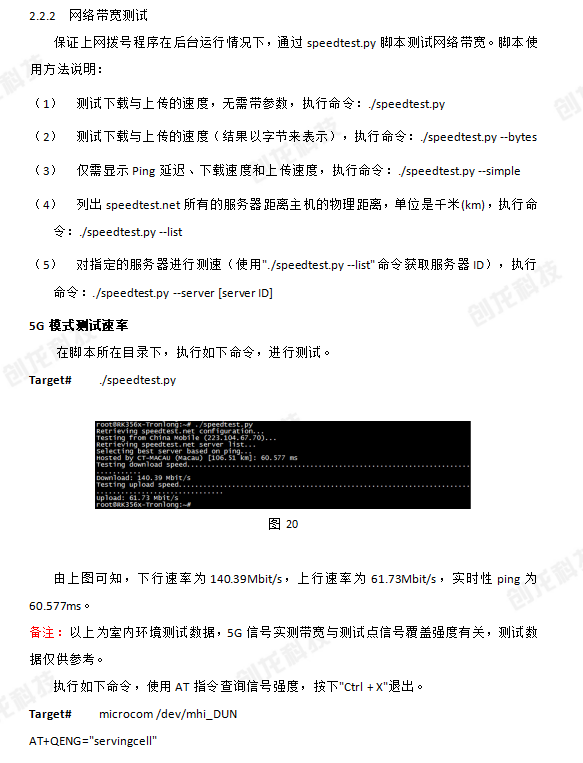

RK3568-PCIe 5G通信测试手册

RK3568-PCIe 5G通信测试手册

评论