芯砺智能近日宣布,其全自研的Chiplet Die-to-Die互连IP(CL-Link)芯片一次性流片成功并顺利点亮。这一重大突破标志着芯砺智能在异构集成芯片领域取得了领先地位,为人工智能时代的算力基础设施建设提供了更加多元灵活的互连解决方案。

CL-Link芯片作为人工智能时代片间互连的最优路径,展现了出色的性能。它完美地实现了高带宽、低延迟、低成本、高可靠性和高安全性,使其在智能汽车、人形机器人、高性能边缘计算和服务器等多个领域具有广泛应用前景。

芯砺智能的CL-Link芯片不仅突破了传统互连技术的限制,更在后摩尔时代为异构集成芯片领域带来了全新的思考和解决方案。这一创新技术将进一步推动人工智能和算力基础设施的发展,为未来的技术进步和应用拓展奠定坚实基础。

总的来说,芯砺智能的CL-Link芯片是一次重大里程碑,它不仅展示了公司在异构集成芯片领域的领先实力,更为人工智能时代的技术进步和应用拓展打开了新的篇章。我们期待在未来看到更多此类突破性的技术成果,共同推动半导体产业的发展和进步。

-

芯片

+关注

关注

456文章

51157浏览量

426671 -

人工智能

+关注

关注

1796文章

47643浏览量

239917 -

异构集成

+关注

关注

0文章

34浏览量

1914

发布评论请先 登录

相关推荐

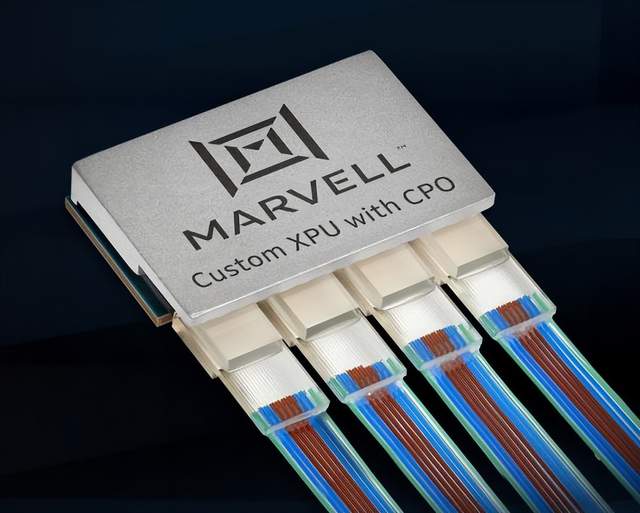

Marvell发布突破性CPO架构,浅析互连产品的利弊得失

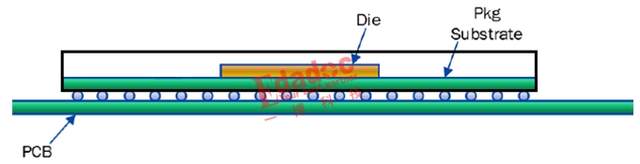

利用Multi-Die设计的AI数据中心芯片对40G UCIe IP的需求

奇异摩尔32GT/s Kiwi Link Die-to-Die IP全面上市

最新Chiplet互联案例解析 UCIe 2.0最新标准解读

芯砺智能Chiplet Die-to-Die互连IP芯片成功回片

芯砺智能Chiplet Die-to-Die互连IP芯片成功回片

评论