在高速的同步电路设计中,时序决定了一切,要求所有时序路径都必须在约束限制的时钟周期内,这成为设计人员最大的难题,因此,首先确定和分析基本时序路径有助于设计者快速,准确地计算时序裕量,使系统稳定工作,XILINX公司提倡的几种常用基本路径。

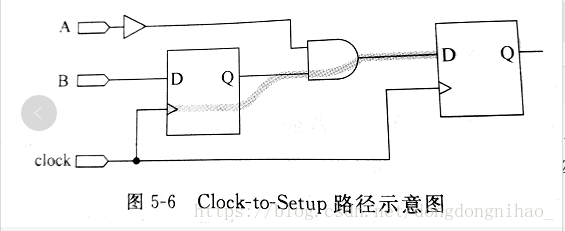

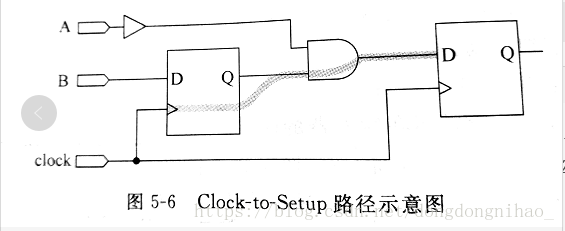

(1)Clock-to-Setup路径:

clock-to-setup路径从触发器的输入端开始,结束于下一级触发器,锁存器或者RAM的输入端,对终止端的数据信号要求一定的建立时间。

如下图所示:

该条路径包括了触发器内部clock-to-Q的延迟,触发器之间的由组合逻辑造成的路径延迟以及目标触发器的建立时间,其延时是数据从源触发器开始,在下一个时钟沿来到之前通过组合逻辑和布线的最大时间,Clock-to-Setup时间可通过约束文件中的周期约束来限制。

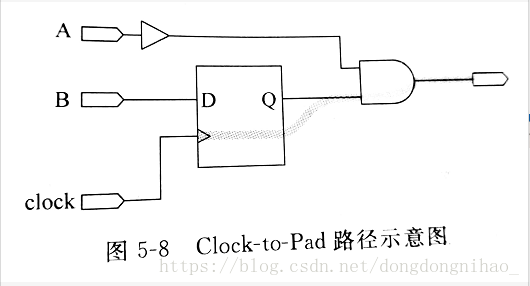

(2)Clock-to-pad路径:

Clock-to-Pad路径从寄存器或者锁存器的时钟输入端开始,终止于芯片的输出引脚,中间经过了触发器输出端以及所有的组合逻辑,如下图所示:

这条路径包括了经过触发器的延时和从触发器到输出引脚之间的逻辑延迟,在约束文件中,可以通过OFFSET语句和FROM:TO来约束,如果使用OFFSET语句,那么时延计算时会包含时钟输入BUFFER/ROUTING延时;如果使用FROM:TO约束,则延时从触发器自身开始,不包括输入路径,比较精确,所以使用相对更频繁一些。

① OFFSET语句:OFFSET说明了外部时钟和与其相关的输入,输出数据引脚之间的时序关系。其语法规则如下:

OFFSET={IN/OUT}"offset_time"[unit] {BEFORE/AFTER} "clk_name"[TIMEGRP"group_name"];

OFFSET可以用于设置多类约束,对于Clock-to-Pad需要将属性配置为OUT AFTER, 例如:

NET Q_out OFFSET = OUT 35.0 AFTER "CLK_SYS"

② FROM :TO 语句 :FROM:TO定义了两组信号之间时序关系。

其语法规则如下:

#TIMESPEC "TSname" = FROM "group1"TO "group2" value;

其中,TSname 必须以TS开头,group1是起始路径,group2是目的路径,value值的默认单位为ns,也可以使用MHZ。

实例:

TIMESPEC TS_aa = FROM FFS TO PAD 10;

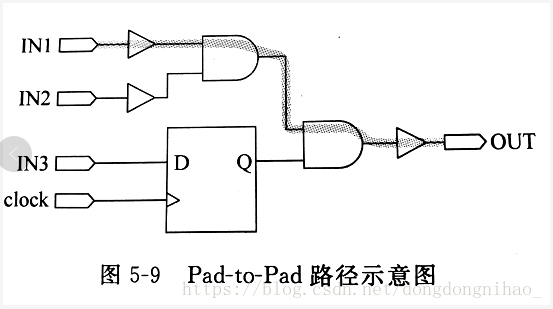

(3)Pad-to-Pad路径:

Pad-to-Pad路径从芯片输入信号端口开始,结束于芯片输出信号端口,中间包含所有组合逻辑,但并不包含任何同步逻辑如图所示:

Pad-to-Pad路径延时是数据输入到芯片,经过逻辑延时和布线时延后再输出芯片的最大时间要求,在约束文件中任然通过FROM:TO来约束,其语法如下:

TIMESPEC TS_aa = FROMPADSTO PADS 10 ;

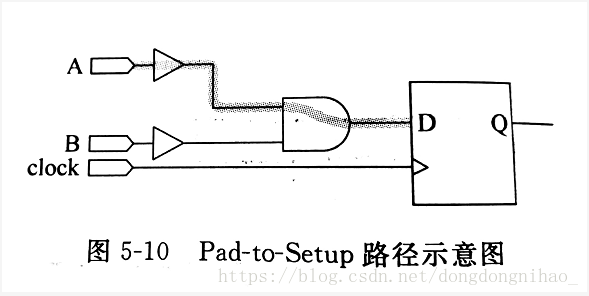

(4)Pad-to-Setup路径

Pad-to-setup路径从芯片的输入信号端口开始,结束于同步电路模块(触发器,锁存器和RAM),对相应的数据信号要求一定的建立时间,如下图所示:

该路径可以通过BUFFER和所有组合逻辑,不包含任何同步电路木块和双向端口,是数据到达芯片的最大时间要求,和Clock-to-Pad一样,该路径可以通过OFFSET和FROM:TO来设计,其中OFFSET语句的属性设置为OFFSET IN BEFORE。

例如:

OFFSET = IN 10 ns BEFORE my_clk TIMEGRP My_FFS;

-

FPGA

+关注

关注

1629文章

21736浏览量

603293 -

触发器

+关注

关注

14文章

2000浏览量

61152 -

时序

+关注

关注

5文章

387浏览量

37330

原文标题:FPGA设计的常用基本时序路径分析

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

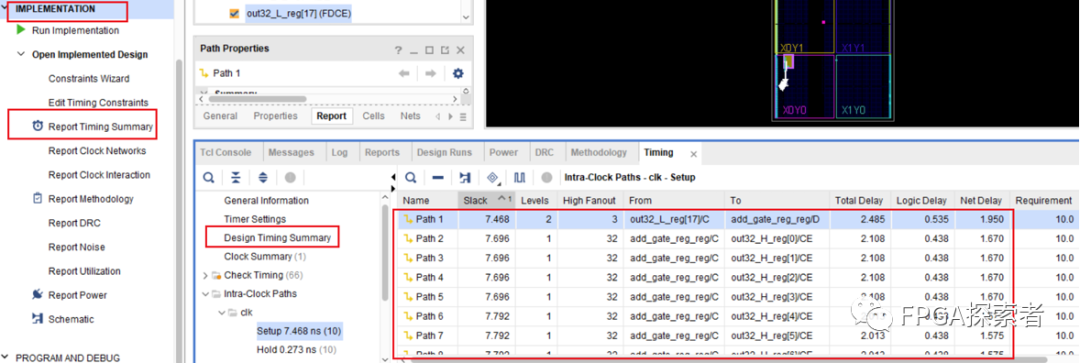

详细解析vivado约束时序路径分析问题

FPGA时序约束之伪路径和多周期路径

FPGA时序分析之关键路径

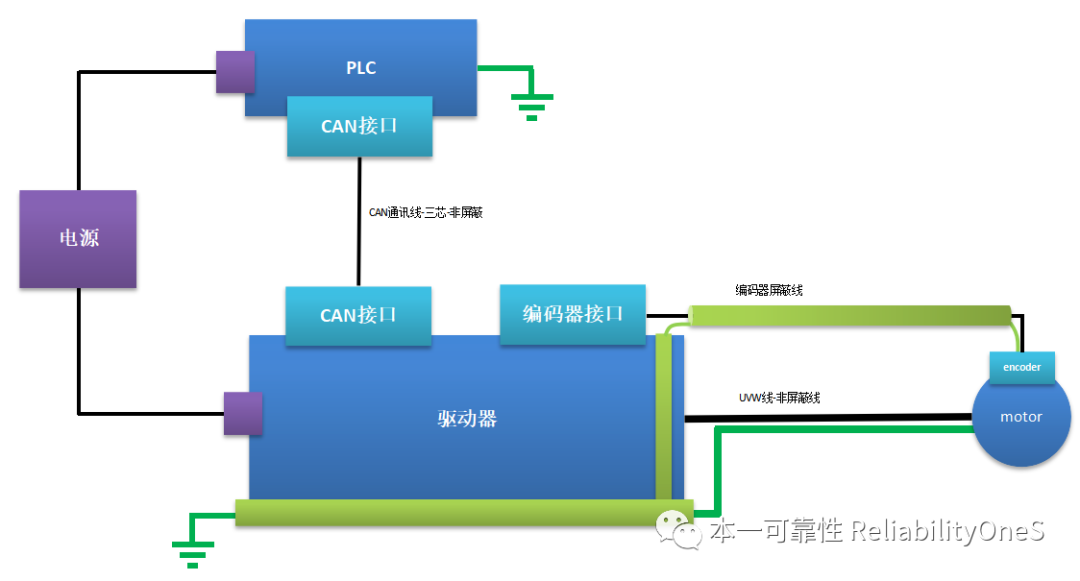

驱动器共模电流路径与数学模型分析

ArcGIS的路径分析

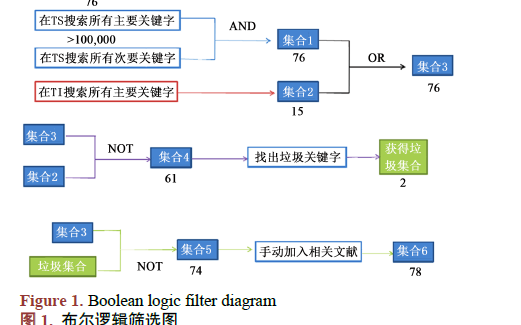

如何使用WOS进行负面口碑发展之路径分析

时序路径分析提速

FPGA设计的常用基本时序路径分析

FPGA设计的常用基本时序路径分析

评论