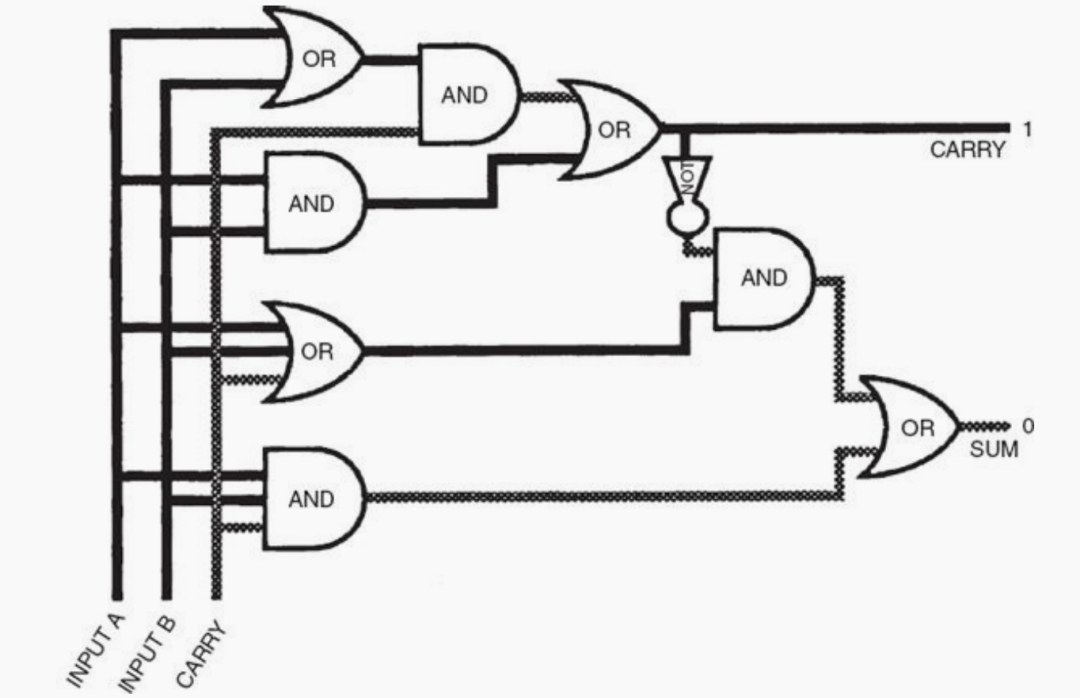

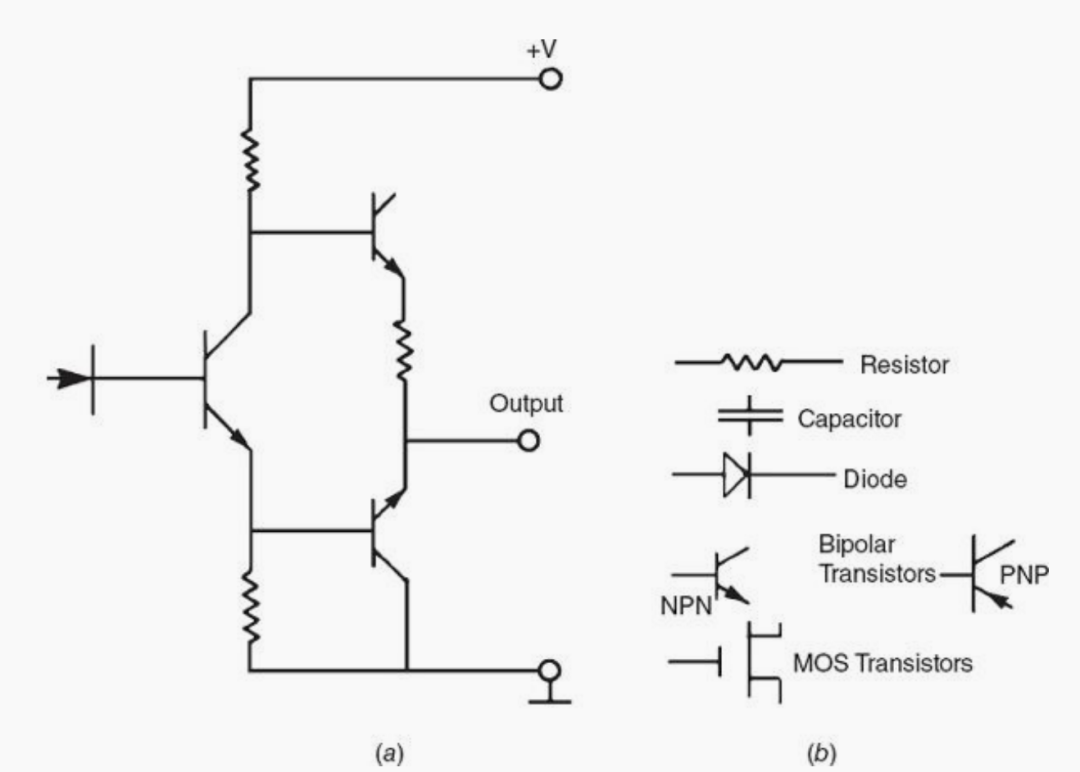

电路设计是制造微芯片的第一步。电路设计人员首先会从设计电路的单元功能图开始,如逻辑图中所示的这样。这张图列出的是一些主要功能和相应算法操作所需的电路。接下来,设计师将功能图转换为原理图(下图中进行了详细展示),在原理图当中,会显示各电路元件的数量和它们之间的相互连接方式。每个基本的电路组成部分都可以用一个符号来进行表示。随附在原理图,包含了一些电路的电气参数(电压、电流、电阻等),以及是否可以使电路正常工作所需要的条件。

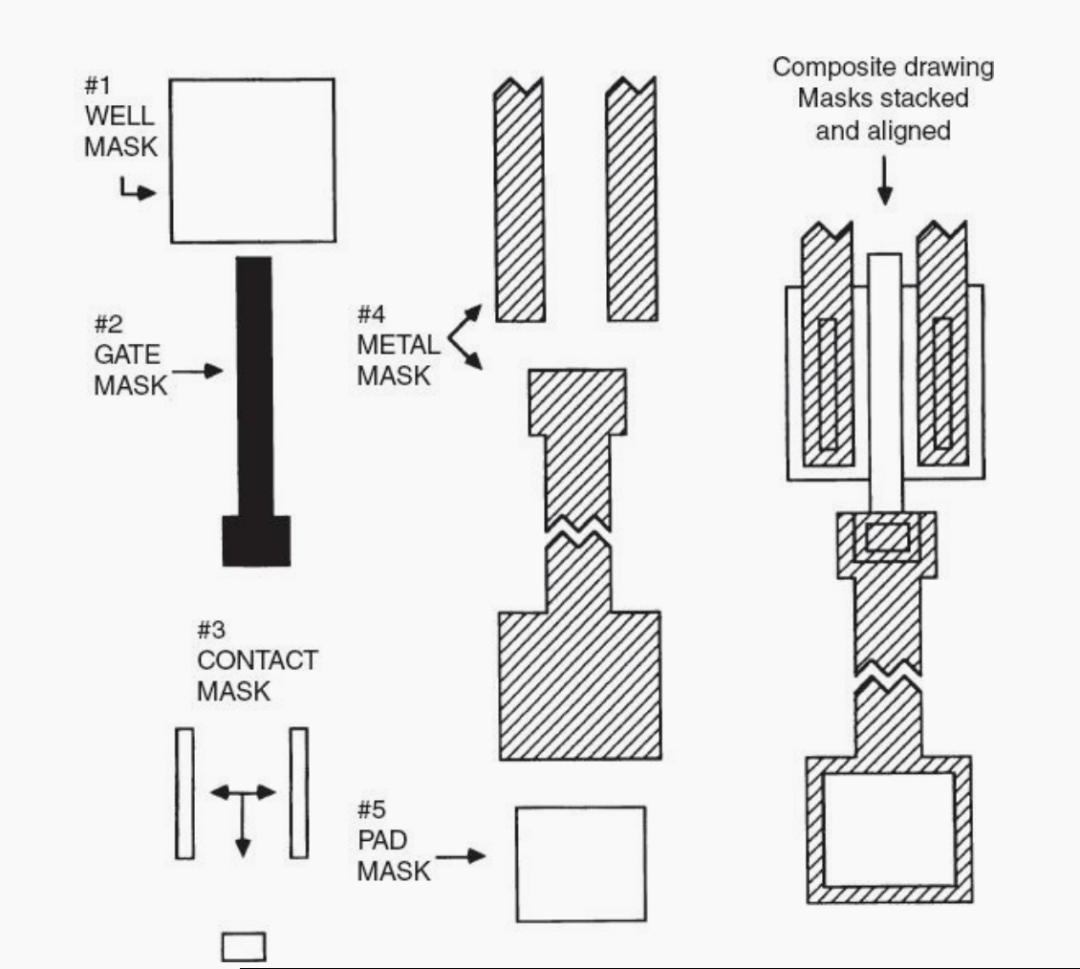

第三步,是电路布局阶段,这一点是半导体电路所特有的。电路操作取决于许多因素,包括材料电阻率,材料物理学,以及各个部件的物理尺寸。零件之间的相对位置是另一个因素。所有这些考虑因素都需要进行全面的考虑,最终决定了零件、设备或部件的物理布局和尺寸电路。电路的布局从使用复杂的计算机辅助设计(CAD)系统开始,将每个电路元件转换成其物理形状和尺寸。

通过在CAD的软件中,通过构建电路图,完全将我们前期的电路设计工作结合进来。最终在所有子层图案的共同叠加下,合成在电路表面。这称为复合图(如下图所示)。合成图类似于从顶部看多层办公楼的蓝图,它展示了所有的楼层。然而,复合材料比普通材料大很多倍,最终增大了电路的尺寸。

建筑物和半导体电路都是用一次建造一层的方式进行的。因此,有必要将复合绘图分离到电路中的单个层各自的布局中去。下图说明了多层和单层结构的一个简单的硅栅MOS晶体管的层图。

每个层图都是数字化的(数字化是将层图映射到数字数据库的一种方式),并绘制在计算机化的X-Y标绘表上。

十字线和掩模

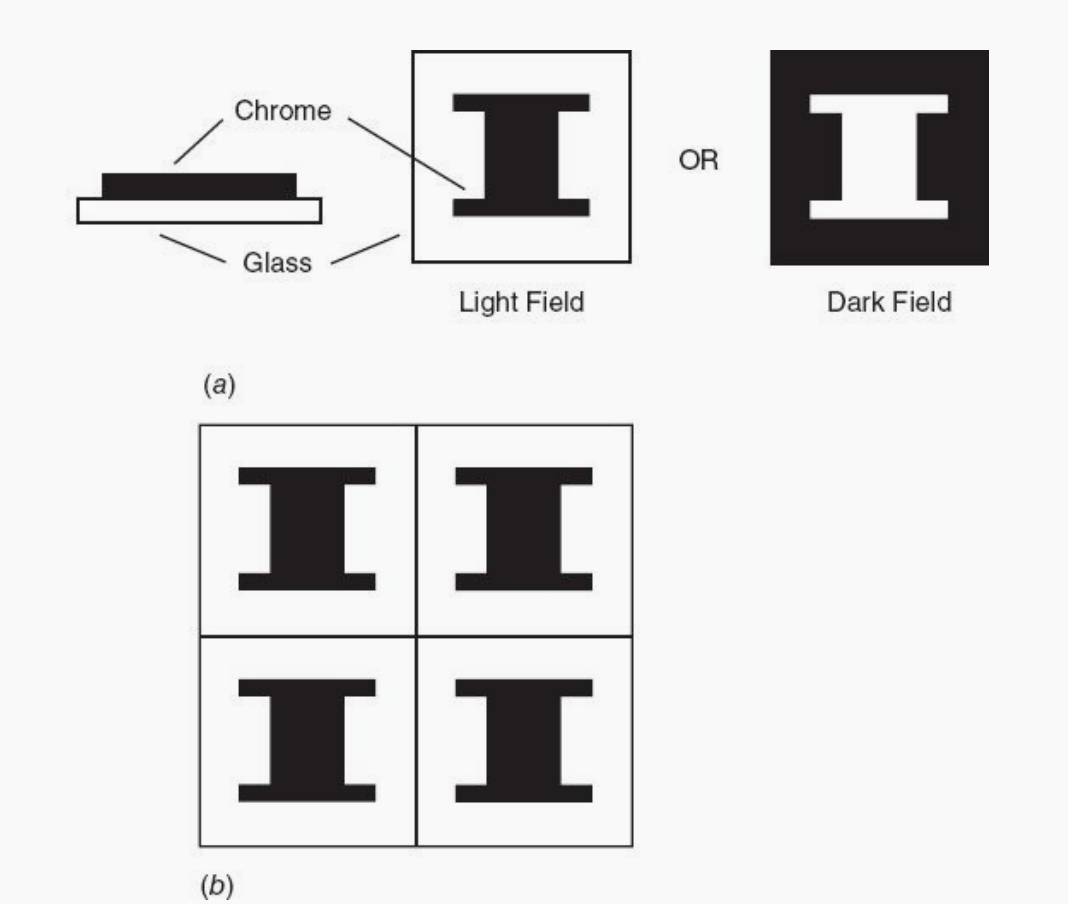

图案化过程用于在晶圆片表面创建所需的层图。将数字化的图案雕刻为晶圆片表面的图案需要几个基本的步骤。对于光处理,有一个中间步骤叫做十字线对准。十字线对准是一种“硬拷贝”,可以使用沉积在玻璃或石英板上的薄层铬形成相应的图案的方式完成再复制(如下图a所示)。它是使用光掩膜工艺来具体实现的。曝光光刻胶的(电子束)发生器与使用电子束在晶圆上使用的工艺相同。可以直接使用准星制作图案的方式或可用于制作光掩模。

掩模可以认为是一个玻璃板,表面有一层薄薄的铬层形成的。在制作之后,它就是一个覆盖着许多电路图案的副本(如下图b所示)。它被用来在整个晶圆片表面完成一个图案转移的过程。电子束曝光系统可以跳过划线或掩模步骤,直接在晶圆片表面曝光。光栅和掩模制作过程我们将在后续的章节中继续详细介绍。

十字线和掩膜一般可以由内部部门自己生产,也可以从外部供应商购买。每种电路类型都有自己的一组单独的掩模。

审核编辑:刘清

-

半导体

+关注

关注

334文章

27596浏览量

220767 -

MOS晶体管

+关注

关注

0文章

18浏览量

7710 -

晶圆制造

+关注

关注

7文章

281浏览量

24111

原文标题:半导体行业(二百三十七)之晶圆制造与封装概述(三)

文章出处:【微信号:FindRF,微信公众号:FindRF】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

半导体行业之晶圆制造与封装概述(三)

半导体行业之晶圆制造与封装概述(三)

评论