一般来说,复位信号有效后会保持比较长一段时间,确保 register 被复位完成。但是复位信号释放时,因为其和时钟是异步的关系,我们不知道它会在什么时刻被释放。

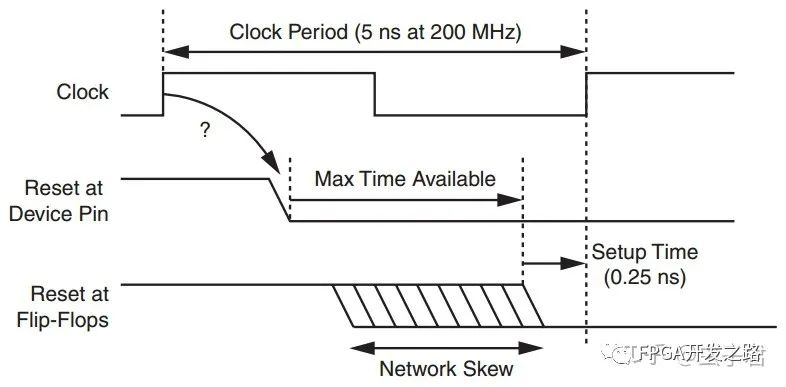

首先看图1,考虑复位信号在两个时钟沿之间被释放的情况。Reset 信号从 Device Pin 到 Flip-Flop 的延迟最大不能超过“Max Time Available”,如果延迟超过了这个限制,那么复位信号的释放会进入 Setup Time 要求的区间,导致 Flip-Flop 进入亚稳态。当时钟频率变高,时钟周期变短,不难发现,要满足这个要求是越来越难的。

图1 - Reset timing diagram, deasserted between clock edges

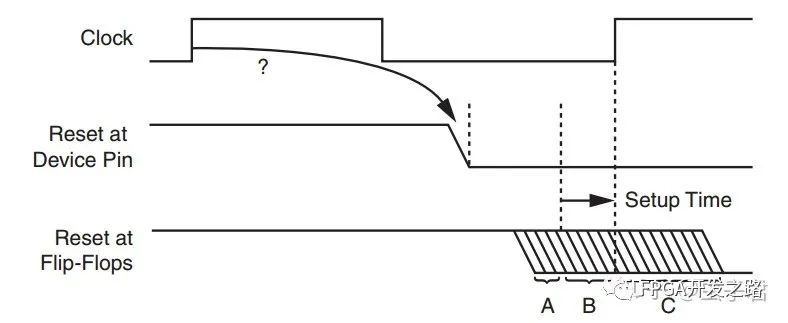

前面我们提到过,因为是异步信号,我们无法确保信号的释放在一个确定的区间。如图2所示,对于 Flip-Flop 来说,异步信号的释放可能在A区间,也可能在B或者C区间。假设现在我们的设计中包含三个 Flip-Flop,分别为FF1,FF2 和 FF3。FF1 的复位释放落在A区间,所以 FF1 会在复位信号释放后的第一个时钟沿有效,FF3 的复位释放落在C区间,那么 FF3 会在复位信号释放后的第二个时钟沿有效,而 FF2 的复位释放落在B区间,所以 FF2 可能会进入亚稳态。

图2 - Reset deasserted asynchronously to the clock

不同的 FF 因为复位信号释放的位置不同而在不同的时刻有效,这会对设计造成影响吗?

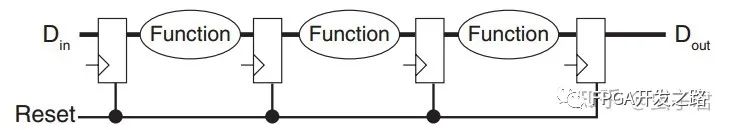

假如我们的设计是如图3所示的情况,是不会对设计的功能造成影响的。在复位释放之后,任何有问题的数据会被Pipeline排出去,经过4个cycle之后,这个pipeline便会恢复到正常的工作状态。

图3 - Reset for a pipeline

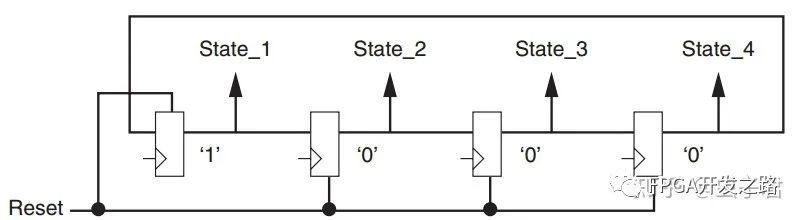

但如果我们的设计是如图4所示。被复位的FF是状态机的状态,那么复位释放后很有可能状态机会被复位到一个无效的状态,影响正常的功能。

图4 - Reset for a one-hot state machine

什么是同步释放 ?

从上一部分的内容我们发现,异步信号的异步释放会导致 FF 在不同的时刻有效,甚至进入亚稳态,从而影响设计的功能运行。如何避免这个问题呢?考虑同步释放。顾名思义,同步释放就是让复位信号的释放过程与时钟同步,从而确保所有 FF 在同一时刻有效。

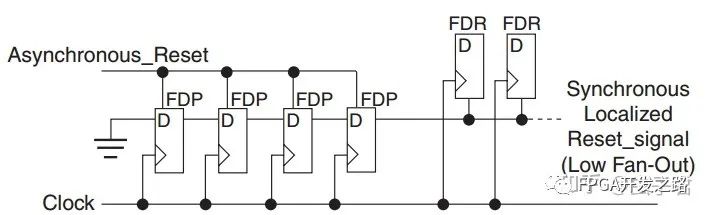

如图5所示,是异步复位同步释放的电路设计。FDP的个数决定复位信号保持的长度,最少要有两个。当复位信号释放后,FDP chain 会将接地的0逐级pipe到最后一个FDP输出,因为该FDP的输出是和Clock同步的,所以FDR的复位释放便是和Clock 同步的。

图5 - Async reset with sync dessertion

最后一个FDP不是仍然是异步复位异步释放么,会不会这个FDP因为异步释放进入亚稳态,那么其输出的复位信号也不确定从而导致复位失败?

答案是不会。FDP会进入亚稳态的条件是什么?一是异步释放非常贴近时钟沿,二是 FDP 输入D在时钟沿附近发生跳变。根据这个电路设计,FDP的输入D时不会在异步释放时发生跳变的,所以FDP不会进入亚稳态。

异步复位同步释放的时序约束

异步复位同步释放的电路我们已经设计好了,如何进行时序约束呢?

对于 FDR,我们可以不用考虑的。因为工具会分析复位信号的 Recovery Time 和 Removal Time 来确保时序收敛。如果发现 Recovey Time 或者 Removal Time 的违反,我们可能需要看一下 reset tree 或者 clock skew。一般都是 Recovey Time的违反,类似于 Setup Time,可能是由于 reset path的延迟太长导致。

对于 FDP,D端是同步电路,而CLR输入端是异步信号,通过电路的设计我们已经避免的异步信号带来的问题,所以为了避免 false timing violation,我们可以对 FDP 的 CLR 端设置 false path。

审核编辑:刘清

-

FPGA设计

+关注

关注

9文章

428浏览量

26606 -

状态机

+关注

关注

2文章

492浏览量

27641 -

FDR

+关注

关注

0文章

11浏览量

8702 -

异步复位

+关注

关注

0文章

47浏览量

13343

原文标题:FPGA复位设计中异步复位为什么要同步释放 ?

文章出处:【微信号:FPGA研究院,微信公众号:FPGA研究院】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Xilinx FPGA异步复位同步释放—同步后的复位该当作同步复位还是异步复位?

异步复位异步释放会有什么问题?FPGA异步复位为什么要同步释放呢?

异步复位异步释放会有什么问题?FPGA异步复位为什么要同步释放呢?

评论