之前介绍的项目《优秀的 Verilog/FPGA开源项目介绍(十四)- 使用FPGA实现LeNet-5 深度神经网络模型》最后我们分析了,纯FPGA实现神经网络的缺点,以及现在FPGA厂家的加速方案,这里引用一下:

到底纯FPGA适不适合这种大型神经网络的设计?这个问题其实我们不适合回答,但是FPGA厂商是的实际操作是很有权威性的,现在不论是Intel还是Xilinx都没有在自己传统的FPGA上推广AI,都是在基于FPGA的SoC上推广(Vitis和OpenVINO,前者Xilinx后者Intel),总结来看就是:纯 RTL 硬件设计不是AI的好选择。特别是对于大规模网络,权重和中间结果需要存储在外部存储器中。并且数据迭代器会更加复杂。设计周期长,AI相关领域迭代速度快,综上以上几点,可以很容易给你们指引一条道路。

目前主流的解决方案就是使用通用或专用处理器来做控制工作,让硬件来执行计算(加速的概念),今天就介绍两个针对以上解决方案的开源项目,这两个项目是用FPGA进行硬件加速的必备项目。

AI算法流程

在进行项目介绍前,我们先介绍一下软件架构和工具集。这个后面会影响理解。

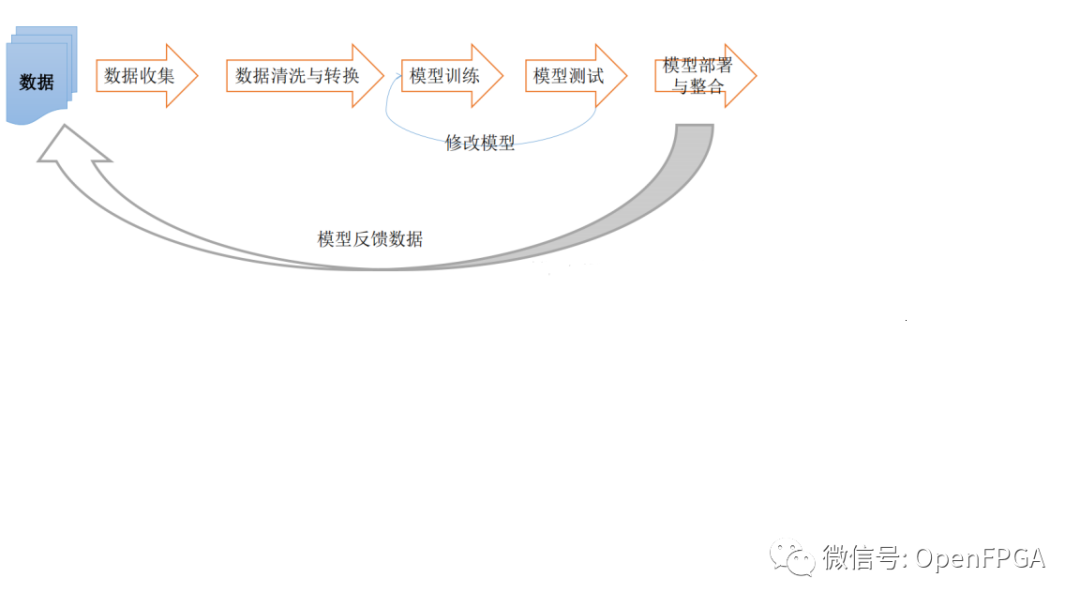

一个完整的深度学习框架中主要分为下面几个流程:

有一些是我们不太关心的部分(对于FPGA实现应用),即数据收集等,所以上诉流程再简单分为几个主要部分,即训练(training)和推理(inference)、部署(deployment)。

训练(Training)

使用训练模型(Caffe、TensorFlow、MxNET、ONNX等)根据训练数据得到相关的参数。举个例子,我现在想要设备识别猫和狗,我首先需要收集猫和狗的图片(这些图片称为训练数据集(training dataset)),但是这些数据集在进行训练前要有标签(即每张照片是狗,那张照片是猫),选择好训练模型后,将上诉数据给训练模型进行训练,训练模型不是万能的,虽然能通过训练不断的优化参数,但是在训练完还不一定能达到你想要的识别率(比如100张图片有50张能识别),接下来就是通过优化参数,让另外50张错的也变成对的。这整个过程就称之为训练(Traning)。

推理(Inference)

这个过程比较简单,就是把上面训练好的模型,去识别不是训练集里的图片(这种图片就叫做现场数据(live data)),如果对这些现场数据的识别也非常NICE,那么证明你的网络训练的是非常好的,如果不是特别好,就需要把训练数据集增加,重复这一过程,直到现场数据也达到比较好的效果。把训练好的模型拿出来进行现场实验推理的过程,称为推理(Inference)。

部署(deployment)

部署的理解很简单,就是经过上面两个步骤的模型应用,把它放在某个硬件平台上运行,这个过程称之为部署(deployment)。

其实各大厂家推出自己的架构/工具都是基于上诉流程,不同点就是会针对自家的硬件做细节优化。

现在常见的模型推理部署框架有很多,比如:英特尔的OpenVINO,英伟达的TensorRT,谷歌的Mediapipe,Xilinx Vitis。

Intel FPGA OpenVINO

介绍

OpenVINO是Intel推出的用于优化和部署 AI 推理的开源工具包。

提升计算机视觉、自动语音识别、自然语言处理和其他常见任务中的深度学习性能

使用通过 TensorFlow、PyTorch 等流行框架训练的模型

减少资源需求并在从边缘到云的一系列英特尔平台上高效部署

来源:知乎@火狐狸

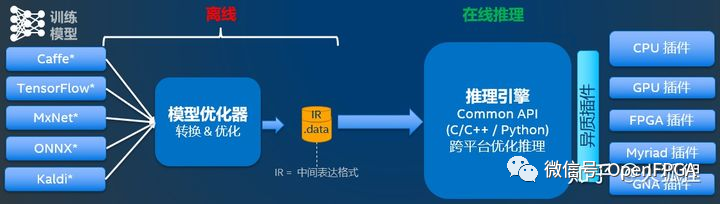

上图就是OpenVINO的组成,针对第一节的 AI算法流程 理解起来不是很难。其中,模型优化器是线下模型转换,推理引擎是部署在设备上运行的AI负载。

因为OpenVINO还有针对自己CPU的架构,没有对FPGA部分过多介绍,所以一些细节会在下一个项目介绍。

视频介绍

关于OpenFPGA在FPGA方面的加速应用,可以查看下面的两个官方中文视频介绍,这里就不再赘述。

Xilinx FPGA Vitis AI

2019年10月,Xilinx正式发布了统一开发软件平台Vitis。Vitis平台无需用户深入掌握硬件专业知识,即软件和算法自动适配到Xilinx的硬件架构。Xilinx Vitis AI是针对自家硬件平台推出的针对AI模型的硬件实现。Vitis AI 提供的工具链能在数分钟内完成优化、量化和编译操作,在赛灵思器件上高效地运行预先训练好的AI模型。

介绍

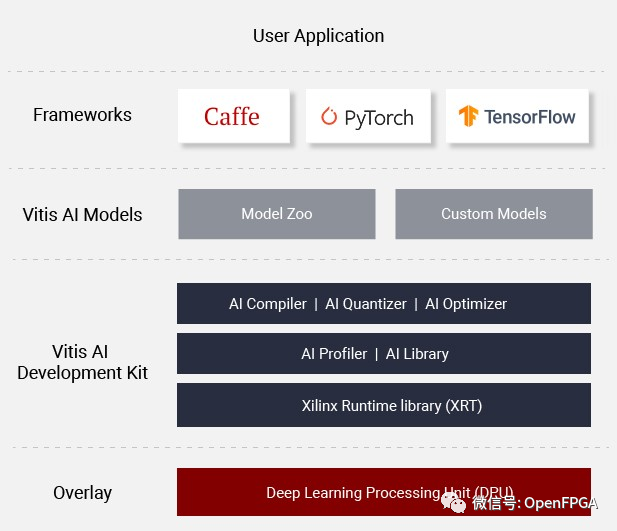

上图就是Vitis AI的整体架构,主要分为AI Model Zoo、AI 优化器、AI 量化器、AI 编译器、AI 配置器、AI 库、XRT、以及核心DPU。

整个流程和上图类似,下面针对每个部分简单介绍(Intel的类似)。

AI Model Zoo

这个就是最流行框架 Pytorch、Tensorflow、Tensorflow 2 和 Caffe 的现成深度学习模型的集合,也就是我们可以简单及快速的进行AI模型的训练和优化。

AI 优化器、AI 量化器、AI 编译器

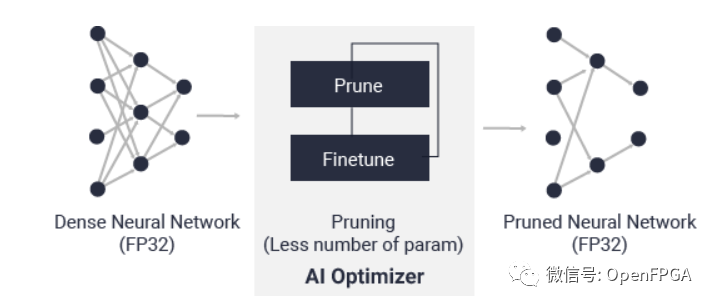

AI 优化器功能简介

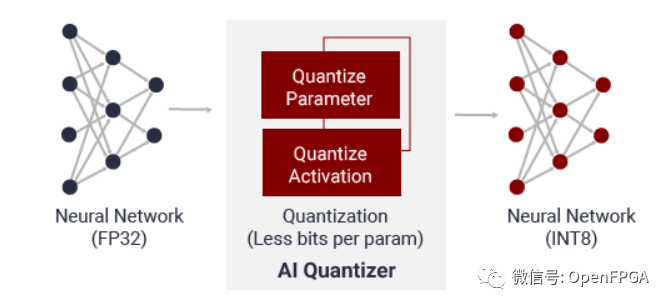

这三个作用就是将训练好的模型进行优化,其中AI 优化器是在牺牲很少的精度情况下降模型的复杂度;AI 量化器的作用其实和FPGA的结构有关(FPGA无法处理浮点数据),AI 量化器就是将32 位浮点权值和激活量转换为 INT8 这样的定点数据。

AI 量化器功能简介

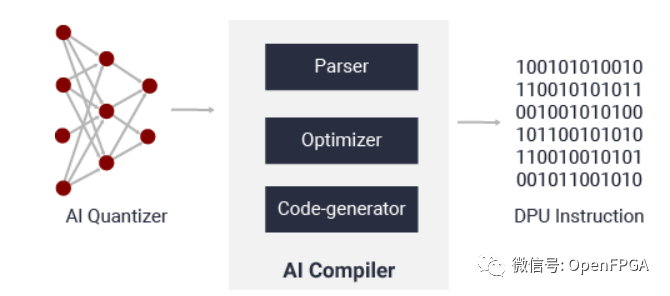

AI 编译器的作用就是将 AI 模型进行高级优化,主要包括指令集、数据流、层融合和指令排程等,并可尽量重复使用片上内存。

AI 编译器功能简介

AI 配置器、AI 库

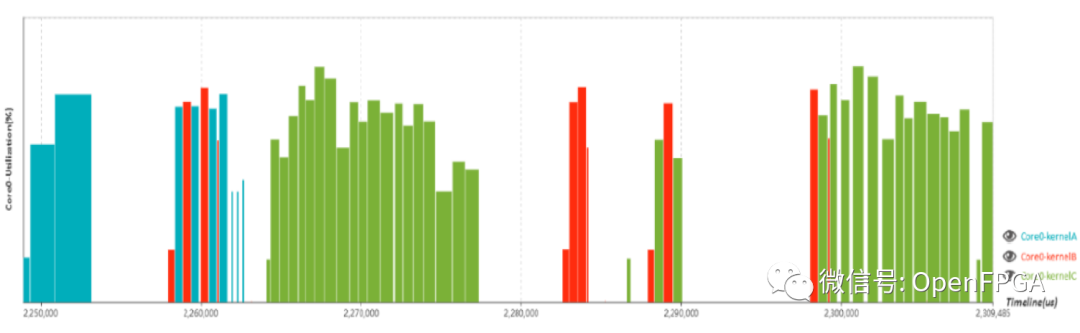

AI 配置器功能简介

AI 配置器主要是辅助开发人员对AI模型的方案实施的效率和利用率进行分析的性能分析器。

AI 库功能简介

AI库主要功能就是将DPU和上层进行链接(基于带有统一 API 的 Vitis AI Runtime 构建)。

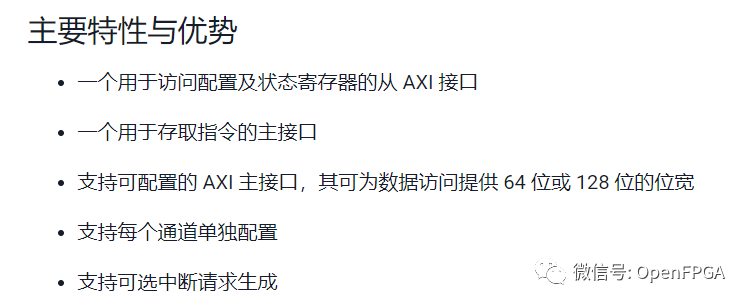

XRT、DPU

这两个是Xilinx的“王牌”了,其中DPU大家应该不陌生,是DNNDK的升级版本(DNNDK官方应该已经不维护了)。

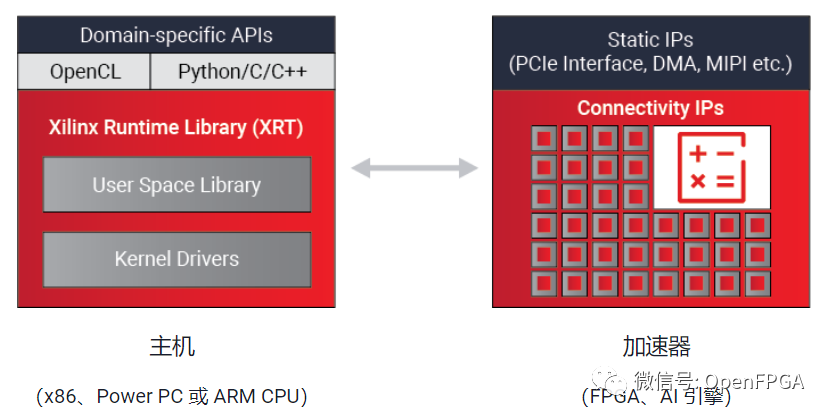

XRT

Xilinx 运行时库 (XRT) 是 Vitis 统一软件平台和 Vitis AI 开发环境的一个重要组成部分,其可帮助开发人员继续使用熟悉的编程语言(如 C/C++、Python 以及高层次特定域框架 TensorFlow 和咖啡等)在 Xilinx 灵活应变的平台上部署。

主要功能如下图所示:

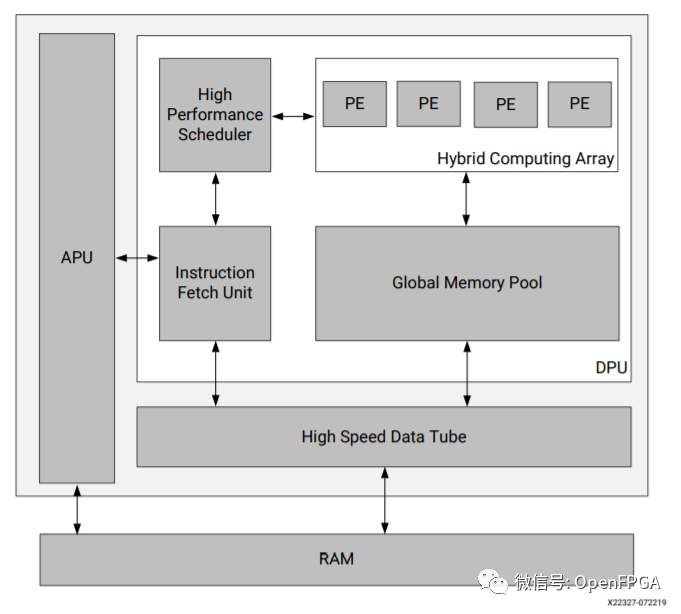

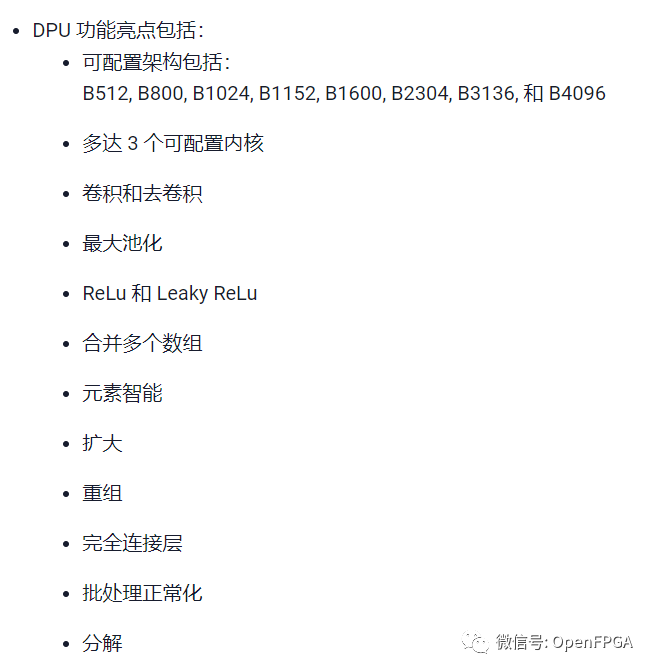

DPU

详细介绍:PG338 PG366

Xilinx深度学习处理器单元 (DPU) 是一个专门用于卷积神经网络的可编程引擎。该单元包含寄存器配置模块、数据控制器模块和卷积计算模块。在 DPU 中部署的卷积神经网络包括 VGG、ResNet、GoogLeNet、YOLO、SSD、MobileNet 以及 FPN 等。

总结

今天介绍了两个最重要的FPGA加速神经网络的开源项目,而且经过几年的发展越发稳定,总结一下就是,如果想用FPGA加速神经网络就快点去看看吧,这里在简单推荐一下这两个项目的入门开发板。

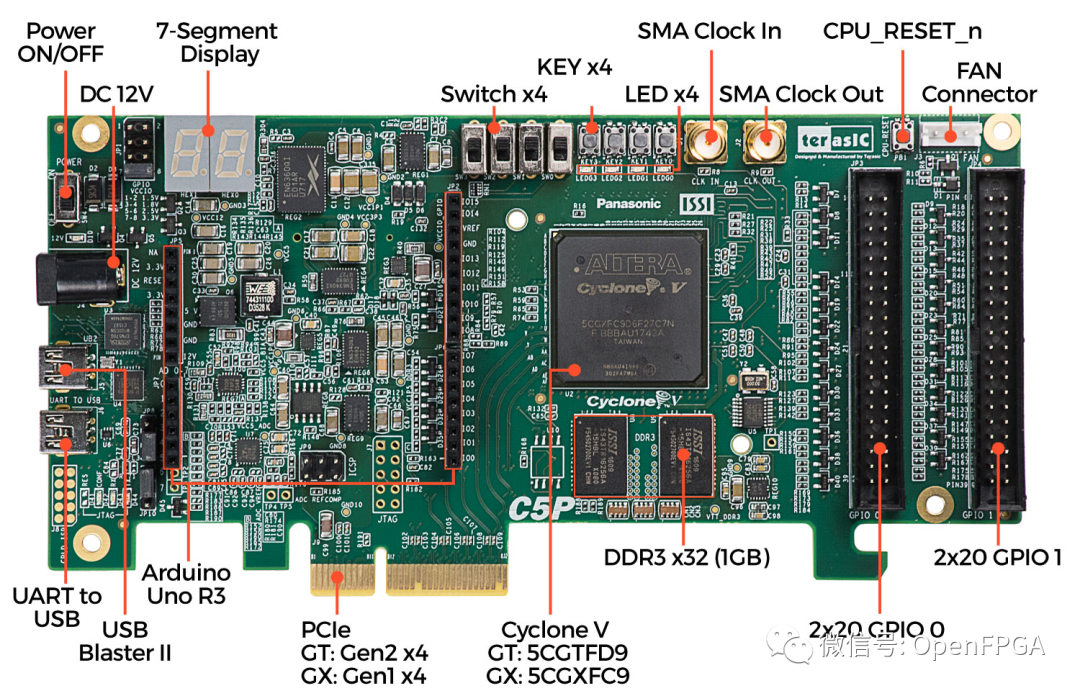

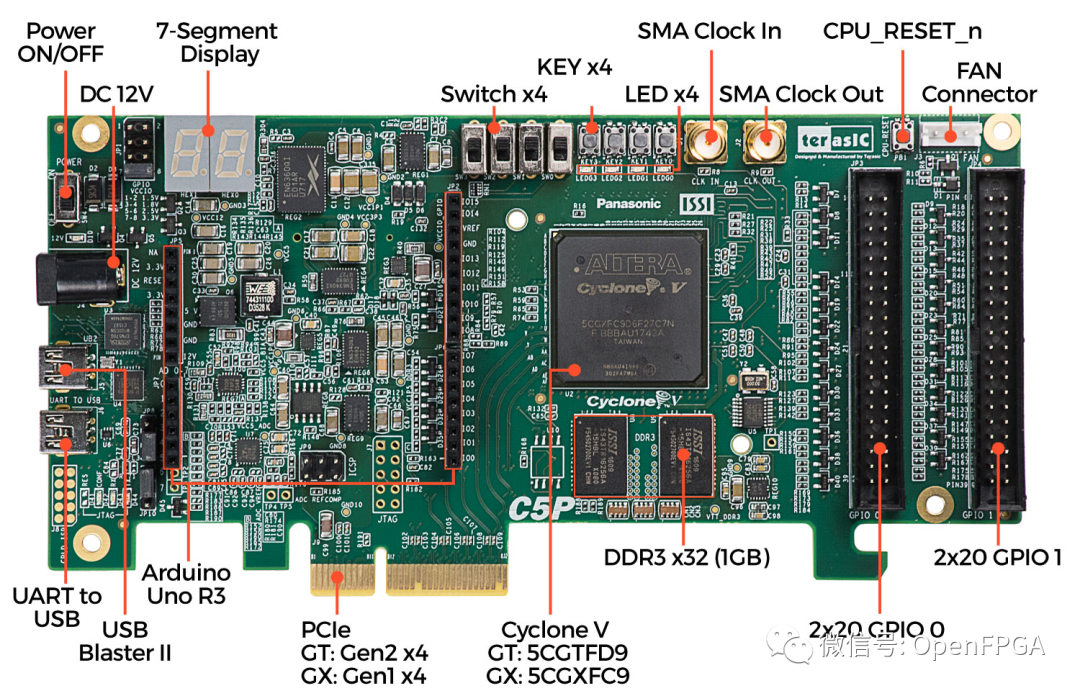

Intel C5P 开发板

Intel OpenVINO入门开发板

Xilinx Kria KV260开发板

最后,还是感谢各个大佬开源的项目,让我们受益匪浅。后面有什么感兴趣方面的项目,大家可以在后台留言或者加微信留言,今天就到这,我是爆肝的碎碎思,期待下期文章与你相见。

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21736浏览量

603333 -

神经网络

+关注

关注

42文章

4771浏览量

100763 -

Xilinx

+关注

关注

71文章

2167浏览量

121403 -

开源

+关注

关注

3文章

3348浏览量

42499

原文标题:想用FPGA加速神经网络,这两个开源项目你必须要了解

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何用FPGA加速神经网络

如何用FPGA加速神经网络

评论