FPGA设计中,生成时钟分为两大类:自动生成时钟和用户生成时钟。前者是指由CMB(Clock Modifying Blocks,例如MMCM、PLL、BUFR 、BUFGCE_DIV、PHASER_x等)生成的时钟;后者是指用户通过组合/时序逻辑生成的时钟。

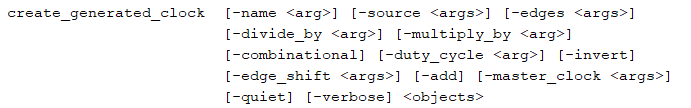

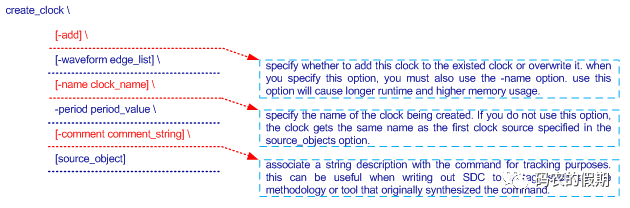

在某些场景下,对于生成时钟需要借助create_generated_clock创建。这里我们讨论一下create_generated_clock的典型应用场景。首先给出create_generated_clock的基本参数,如下图所示。生成时钟都有一个与之伴随的主时钟(MasterClock)。这个主时钟可以是全局时钟管脚进来的时钟(也就是设计的PrimaryClock),也可以是其他生成时钟。可通过选项-master_clock指定。

场景1:重命名自动生成时钟

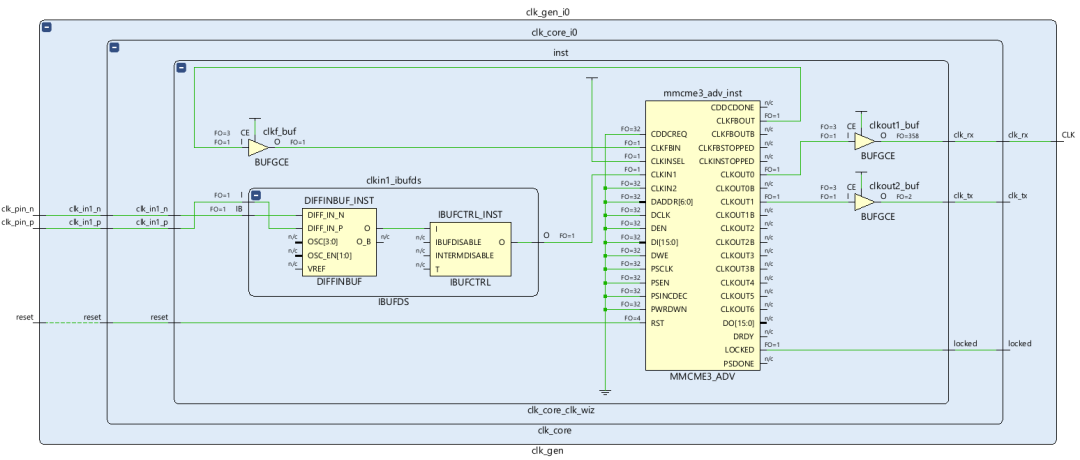

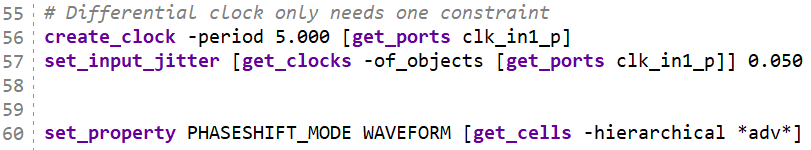

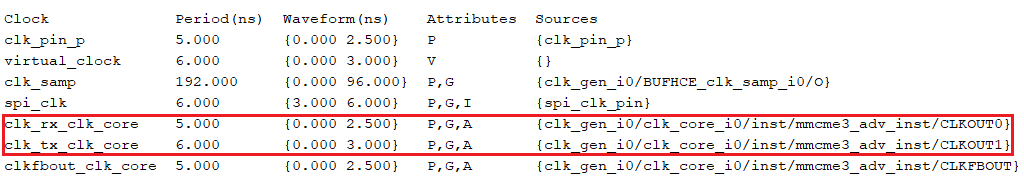

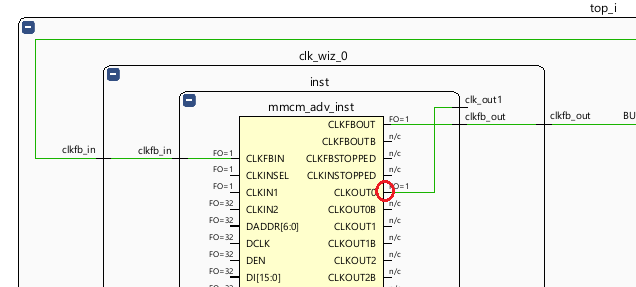

对于自动生成时钟(又称自动衍生时钟),只要创建了主时钟,工具会自动创建生成时钟。因此,如果设计中只存在“全局时钟管脚->MMCM/PLL->BUFG”这种情形,而且MMCM/PLL是通过Clocking Wizard IP生成的,那么用户就不用通过create_clock创建时钟,因为IP会自动创建。例如,对于下图所示设计,IP会自带约束。在这种情况下,打开综合后的设计,执行report_clocks命令,可以看到自动生成的时钟。

如上图所示,自动生成时钟的名字之所以如此,是因为我们在调用IP时对输出端口进行了重命名,如下图所示。

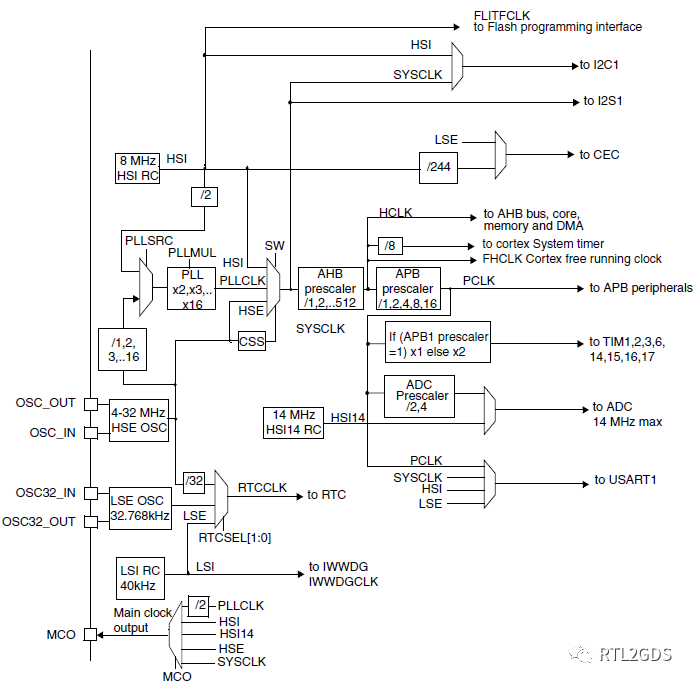

另一方面,如果我们没有对端口重命名,而希望生成时钟名字是期望的名字,以便于阅读分析以及后续约束的引用,这时就可以通过create_generated_clock命令进行重命名。例如:要将下图中的MMCM输出端口CLKOUT0输出时钟命名为clk200,这时需要通过选项-name给时钟命名,同时指定时钟的端口,这里通过get_pins获取。

审核编辑:刘清

-

FPGA设计

+关注

关注

9文章

428浏览量

26593 -

PLL电路

+关注

关注

0文章

92浏览量

6451

原文标题:create_generated_clock该怎么使用?

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA中时钟的用法

对边沿对齐源同步输入端口的约束

时序约束之时钟约束

CLOCK作为外部输出控制Pin的整体延迟?

create_generate_clock无法找到正确的引脚

Xilinx工具vivado使用约束命令时出现警告的解决办法?

请问如何约束作为输入时钟复制的时钟?

子模块的generated clock是否需要和其它子模块进行balance?

静态时序分析

今日说“法”:TimeQuest约束外设之诡异的Create Generated Clocks

FPGA案例之衍生时钟约束

Vivado的XDC设置输出延时问题

请问create_generated_clock该怎么使用呢?

请问create_generated_clock该怎么使用呢?

评论