CLK的作用和注意事项

SD NAND的时钟引脚(CLK)的作用是提供一个时钟信号,用于同步数据传输。时钟信号是由主设备(如微控制器或存储控制器)提供的,用于确保SD NAND和主设备之间的数据交换是按照相同的时序进行的。

1、时钟频率: CLK信号的频率取决于TF卡和主设备之间的通信协议和速率。时钟频率不能超过TF卡规格中定义的最大工作频率,否则可能导致通信错误或数据丢失。

2、时序要求: 时钟信号的上升沿和下降沿需要符合TF卡规格中定义的时序要求。违反时序要求可能导致通信故障。

3、电压要求: 时钟信号的电压应符合TF卡规格中定义的电气特性要求。过高或过低的电压可能对TF卡产生不良影响。

4、连接方式: 确保CLK引脚正确连接到主设备,并且按照TF卡规格连接。通常,CLK引脚连接到主设备的时钟输出引脚。

5、时钟同步: 在进行TF卡通信之前,主设备和TF卡之间需要建立正确的时钟同步。这通常由主设备负责。

6、时钟停止: 在TF卡不被使用时,可以将时钟信号停止以降低功耗。但是,要确保在重新开始通信之前正确地重新启动时钟。

CLK的走线规范

1、CLK的走线越短越好;

2、CLK避免走线经过大电感下面,或者其他干扰强的器件下面;

3、CLK走线不需要加电容滤波,加电容滤波会导致时钟信号变差,

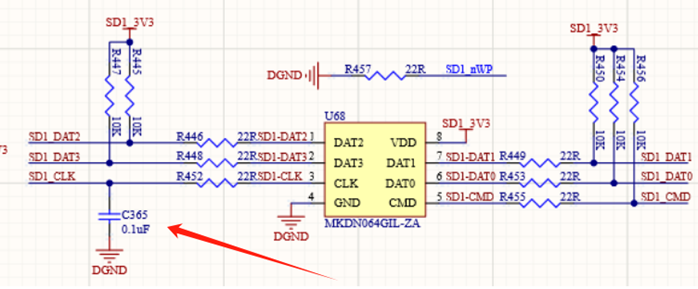

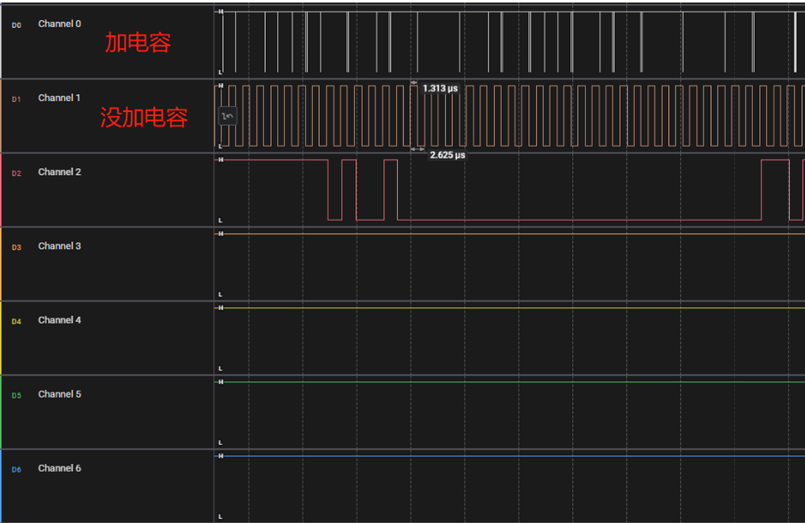

例如下面是CLK加电容的设计原理图和时序

这是同一个程序输出的时钟信号,加了电容的时钟信号看起来不正常,实际也是SD NAND初始化异常。

审核编辑 黄宇

-

引脚

+关注

关注

16文章

2127浏览量

56142 -

SD

+关注

关注

1文章

174浏览量

36596 -

CLK

+关注

关注

0文章

132浏览量

18117

发布评论请先 登录

HDMI在TV应用中的注意事项

DC电源模块的使用注意事项和安全规范

SD NAND的CLK引脚的注意事项和走线规范

SD NAND的CLK引脚的注意事项和走线规范

评论