FPGA输入的时钟信号必须是方波么?正弦波会有影响么?

FPGA是一种可编程逻辑器件,通常用于实现数字电路。输入时钟信号是FPGA中非常重要的时序信号,对整个系统的稳定性和性能都有很大影响。在FPGA设计中,时钟信号通常需要满足一定的要求。

首先,时钟信号在FPGA中必须是一个周期性的信号。这是因为FPGA内部的逻辑电路和存储元件的工作是基于时钟信号的边沿来进行的。通过适当的同步和时序控制,时钟信号的边沿可以有效地用来触发不同的操作和数据传输。因此,时钟信号必须具有与系统同步的周期和相位。

其次,时钟信号在FPGA中通常需要是一个方波信号。方波信号具有明确的跳变边沿,适合用来触发和同步FPGA内部的逻辑运算。方波信号可以提供准确的时序信息,并且与最小化噪声和时序不确定性有关。

然而,如果使用正弦波作为时钟信号会有一些影响。首先,正弦波信号的周期和相位通常不是固定的,因此很难确保与FPGA内部逻辑的同步。其次,正弦波信号可能引入额外的相位噪声和频率扰动,从而影响FPGA内部时序的稳定性和可靠性。此外,正弦波信号在传输过程中存在幅度衰减和相位变化的问题,可能导致时钟信号信噪比的下降。

为了解决这些问题,通常使用专门的时钟发生器或PLL电路来生成稳定的方波时钟信号。这样可以确保时钟信号的周期性、相位准确性和稳定性,以满足FPGA内部逻辑的要求。

总之,FPGA输入时钟信号要求为周期性的方波信号,正弦波信号可能会引入相位、频率和幅度方面的问题,影响FPGA内部逻辑的正确性和性能。因此,在FPGA设计中,使用稳定的方波时钟信号是非常重要的。

-

FPGA

+关注

关注

1664文章

22504浏览量

639306 -

正弦波

+关注

关注

11文章

662浏览量

59323 -

时钟信号

+关注

关注

4文章

510浏览量

30080

发布评论请先 登录

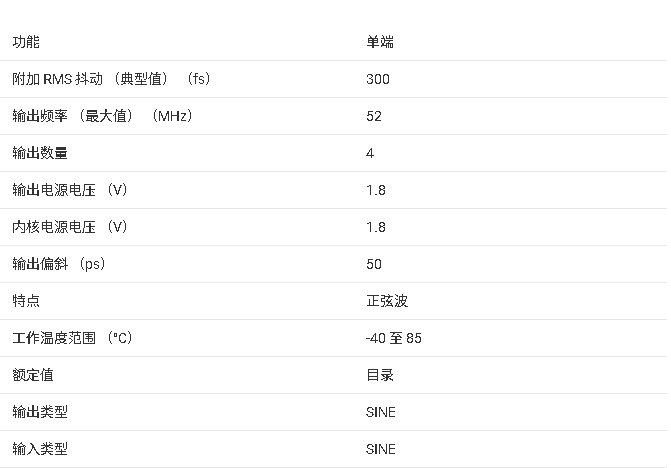

CDC3S04:四通道低功耗低抖动正弦波时钟缓冲器的卓越之选

基于STM32F103驱动AD9833模块 DDS信号发生器输出正弦波/三角波/方波可编程信号

基于STM32F103 并行驱动AD9851模块 DDS函数信号发生器输出正弦波/方波信号

普源DG1022Z信号发生器正弦波频率调节指南

CDC3S04 四通道正弦波时钟缓冲器技术文档总结

信号发生器产生正弦波的频率精准调节方法

正弦波逆变器的工作原理与控制方式

磁性元件变革:告别正弦波激励源,拥抱方波

无刷直流电机方波正弦波复合驱动器设计

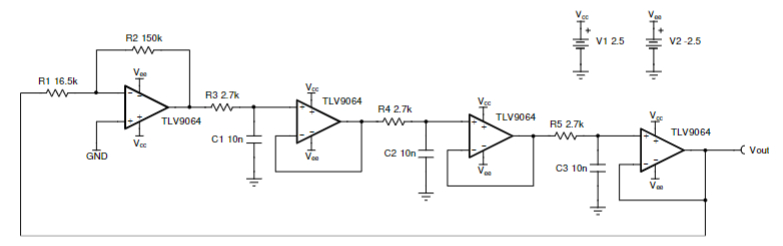

TI 正弦波发生器电路

STM32F723ZET6使用ADC捕获标准正弦波并通过USB主动上报,正弦波重新拟合后存在凹陷峰怎么解决?

实用电源——正弦波逆变器

正弦波低失真度测试仪功能特点 音频信号分析仪 失真度仪

FPGA输入的时钟信号必须是方波么?正弦波会有影响么?

FPGA输入的时钟信号必须是方波么?正弦波会有影响么?

评论