常用的组合逻辑电路

以下是一些常用的组合逻辑电路的例子:

1. 与门(AND gate)- 当且仅当所有输入都为高电平时,输出为高电平。可以用于逻辑乘法和逻辑与运算。

2. 或门(OR gate)- 只要有一个或多个输入为高电平时,输出为高电平。可以用于逻辑加法和逻辑或运算。

3. 非门(NOT gate)- 输入信号取反,当输入为高电平时,输出为低电平;当输入为低电平时,输出为高电平。

4. 与非门(NAND gate)- 与门的输出取反,当所有输入都为高电平时,输出为低电平;否则输出为高电平。

5. 或非门(NOR gate)- 或门的输出取反,只要有一个或多个输入为高电平时,输出为低电平;否则输出为高电平。

6. 异或门(XOR gate)- 只有一个输入为高电平时,输出为高电平;否则输出为低电平。常用于校验和运算和奇偶校验等。

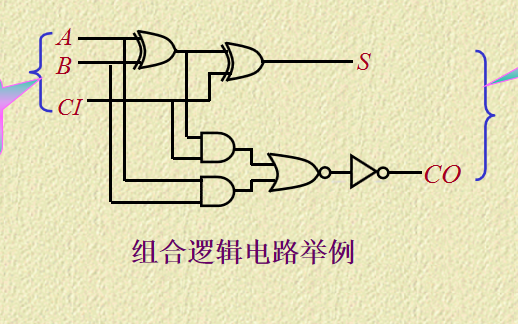

这些逻辑门可以通过连续组合和连接,构建出更复杂的组合逻辑电路,实现各种逻辑功能和运算。

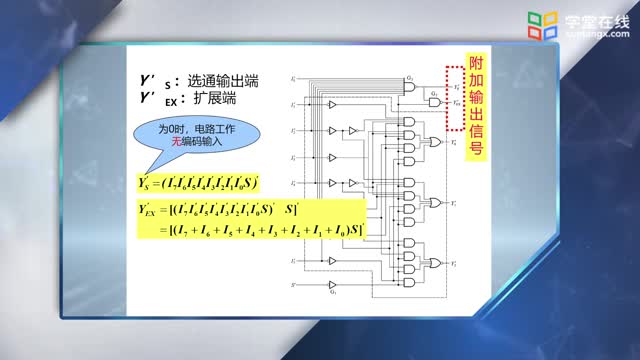

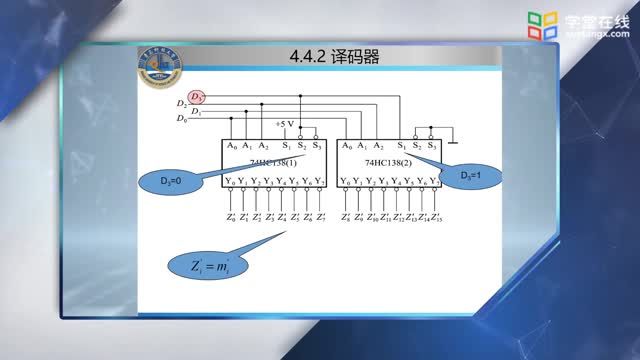

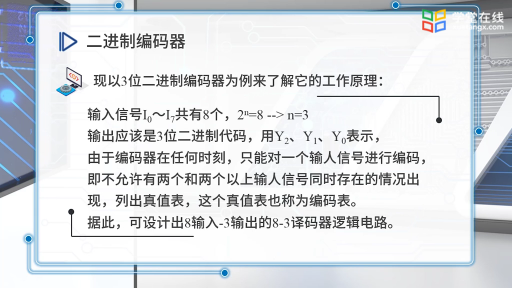

除了上述基本逻辑门,还有一些常用的组合逻辑电路包括多路选择器(MUX)、译码器(Decoder)、编码器(Encoder)、比较器(Comparator)等。这些电路可以用于选择、解码、编码、比较等不同的应用场景。

组合逻辑电路和时序逻辑电路的区别

组合逻辑电路和时序逻辑电路是数字电路中两种重要的逻辑电路类型,它们主要区别在于其输出信号的依赖关系和对时间的敏感性。

1. 组合逻辑电路:

- 输出信号仅依赖于当前的输入信号,与过去的输入信号无关。

- 组合逻辑电路可以通过逻辑门的组合和连接来实现各种逻辑功能和运算。

- 输出信号的计算是瞬时的,没有存储功能。即使输入信号发生改变,输出信号会立即响应并产生相应的变化。

2. 时序逻辑电路:

- 输出信号的计算不仅依赖于当前的输入信号,还可能依赖于过去的输入信号和内部的存储状态(寄存器等)。

- 时序逻辑电路涉及到时钟信号,通过时钟的控制来同步和顺序地处理输入信号和存储状态,以确保正确的操作顺序和时序关系。

- 输出信号的计算可能需要一定的时间延迟,直到时钟信号到达时才会更新输出。

时序逻辑电路在设计和实现中更复杂,对时钟信号、状态存储和时序关系的处理相对较为重要。它适用于需要记忆、状态转换和顺序控制的应用,如计数器、状态机、时序控制逻辑等。而组合逻辑电路更适用于只需根据当前输入进行逻辑运算,不需要考虑存储和时序关系的应用,如逻辑门、数据选择器等。

组合逻辑电路在每个时刻独立地计算输出,而时序逻辑电路则需要考虑存储状态和时序关系,输出的计算需要基于过去的输入和内部状态。

审核编辑:黄飞

-

时序逻辑电路

+关注

关注

2文章

94浏览量

16577 -

时钟信号

+关注

关注

4文章

452浏览量

28648

发布评论请先 登录

相关推荐

掌握常用组合逻辑电路的 EDA 设计方法

中大规模集成组合逻辑构件

计算机常用的组合逻辑电路:加法器

数字电路教程之组合逻辑电路课件详细资料免费下载

常用的组合逻辑电路

常用的组合逻辑电路

评论