稳态是指触发器在某个特定的输入状态下稳定保持输出的状态。根据触发器的类型和触发方式,触发器分为很多种类,不同类型的触发器有不同的稳态。本文将详细描述几种常见的触发器及其稳态,并介绍如何判断触发器的上升沿和下降沿。

一、SR触发器

SR触发器是最基本的触发器之一,通过它可以实现存储器、寄存器等功能。

SR触发器有两个输入:S和R,以及两个输出:Q和Q'。在SR触发器中,有四种不同的输入组合,分别是:

- S=0,R=0:保持状态,稳态。

- S=0,R=1:复位状态,稳态。

- S=1,R=0:设置状态,稳态。

- S=1,R=1:禁止状态,不稳态。

所以,SR触发器的稳态可以有三种不同的情况:保持状态、复位状态和设置状态。

判断SR触发器的上升沿和下降沿可以通过输入引脚的变化情况来确定。在SR触发器中,上升沿指的是从输入引脚的低电平(0V)变为高电平(5V)的过程,下降沿指的是从高电平(5V)变为低电平(0V)的过程。

二、D触发器

D触发器是常用的一种触发器,它可以实现时钟触发、数据存储等功能。

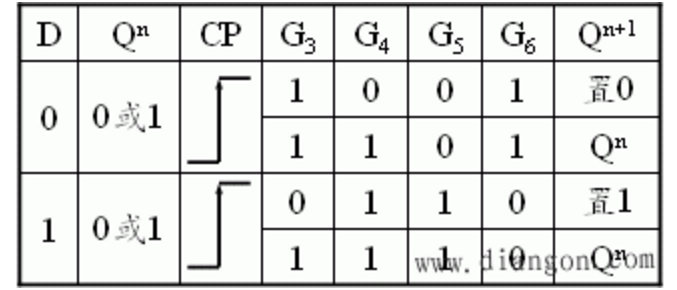

D触发器有一个输入:D,一个时钟输入:CLK,以及一个输出:Q。D触发器的特点是:当CLK信号的边沿(可以是上升沿或下降沿)来临时,Q的状态将跟随D的状态。

D触发器的稳态取决于时钟信号的边沿类型(上升沿或下降沿),以及该时钟边沿前D输入引脚的电平。对于上升沿触发的D触发器,当时钟信号从低电平变为高电平时,D输入在该时刻的电平将被锁存到输出引脚Q上;对于下降沿触发的D触发器,当时钟信号从高电平变为低电平时,D输入在该时刻的电平将被锁存到输出引脚Q上。

因此,判断D触发器的上升沿和下降沿,需要关注时钟信号的变化,并记录D输入引脚在时钟边沿前的电平。如果D在该边沿时刻的电平与上一边沿时刻的电平相比发生了变化,那么可以判断为上升沿或下降沿。

三、JK触发器

JK触发器是一种广泛应用的触发器,它在数字电路设计和时序电路中起到重要的作用。

JK触发器有两个输入:J和K,一个时钟输入:CLK,以及一个输出:Q。JK触发器的特点是:当时钟的边沿来临时,根据J和K的状态决定输出Q的状态,同时还具有置位、复位和翻转的功能。

JK触发器的稳态有三种情况:保持状态、复位状态和设置状态。根据J和K的状态,以及时钟边沿的类型,可以确定JK触发器的稳态。

判断JK触发器的上升沿和下降沿,同样需要注意时钟信号的变化,并记录J和K输入引脚在时钟边沿前的状态。如果J和K在该边沿时刻的状态与上一边沿时刻的状态相比发生了改变,那么可以判断为上升沿或下降沿。

综上所述,不同类型的触发器有不同的稳态。判断触发器的上升沿和下降沿需要注意时钟信号的变化,并记录相应输入引脚的电平或状态的改变。

-

寄存器

+关注

关注

31文章

5620浏览量

130444 -

存储器

+关注

关注

39文章

7758浏览量

172245 -

电平

+关注

关注

5文章

373浏览量

41796 -

D触发器

+关注

关注

3文章

181浏览量

49908 -

时钟信号

+关注

关注

4文章

510浏览量

30086

发布评论请先 登录

d触发器有几个稳态 触发器上升沿下降沿怎么判断

d触发器有几个稳态 触发器上升沿下降沿怎么判断

评论