在实际的电路设计过程中,存在传播延时和信号变换延时。由延时引起的竞争与冒险现象会影响输出的正确与否。下面将就竞争与冒险产生的原因,判断方法和避免竞争与冒险的方法进行讨论,希望对诸位有所帮助。

产生原因

竞争:在组合逻辑电路中不同路径的输入信号到达同一个门级电路时,在时间上有先有后,这种先后时间上的差异称之为竞争(Competition)

冒险:由于竞争的存在,信号在过渡时间瞬间可能产生错误的输出,例如尖峰脉冲。成为冒险。

有竞争不一定产生冒险,但是有冒险一定存在竞争。

判断方法

代数法

在电路的逻辑表达式中保持一个变量不变,其余变量用0或者1替代如果逻辑表达式可以化成:

F = A + ~A

或

F = A·~A

的形式则可以判断出此逻辑存在竞争与冒险。

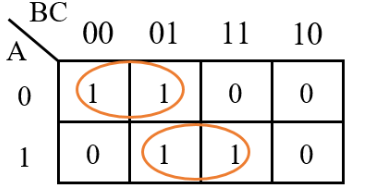

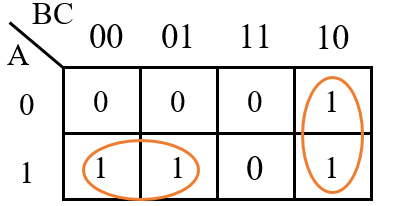

卡诺图法

存在两个相切的卡诺图,若在相切处没有其他卡诺图包围,可能会出现竞争与冒险现象。如下图所示:

F = ~A·~B + A·C

F = A·~B + B·~C

消除方法

常见的避免竞争与冒险的办法有以下四种:

增加滤波电容,滤除窄脉冲

在输出端并联一个小电容,将尖峰脉冲幅度削弱至门电路阈值以下。这种方法的突出问题是会增加输出电压的翻转时间,容易破坏波形。

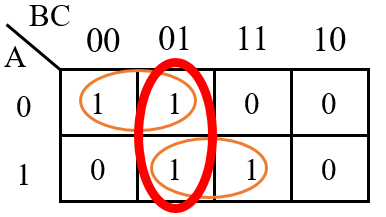

修改逻辑,增加冗余项

在卡诺图中两个相切的圈之间增加一个圈,并加入逻辑表达式之中。如下图所示:

F = ~A·~B + A·C + ~B·C

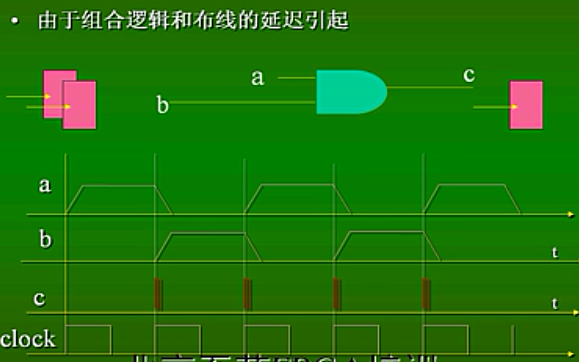

使用时钟同步电路,利用触发器进行打拍延迟

同步电路信号的变化都发生在时钟边沿,对于D触发器的输入端而言,只要毛刺不出现在时钟上升沿并且还不满足建立保持时间要求,就不会对系统产生危害,即D触发器对输入端毛刺不敏感。因此在时钟边沿驱动下,对组合逻辑信号进行延迟打拍即可消除竞争冒险。实际设计过程中可以根据设计需求对信号进行合理的打拍延迟。

采用格雷码计数器

在递加的多bit位计数器,计数值有时候会发生多bit的跳变,产生短暂的尖峰脉冲。而格雷码计数器,计数时相邻的数之间只有一个bit数据发生跳变,所以能有效避免竞争与冒险。

总结

在消除竞争与冒险的办法中,增加滤波电容和逻辑冗余都不是在代码层面考虑的问题。利用触发器在时钟同步电路下对异步信号进行打拍延时常在Verilog中使用。

审核编辑 黄宇

-

电路

+关注

关注

173文章

5984浏览量

173268 -

竞争冒险

+关注

关注

0文章

2浏览量

5044

发布评论请先 登录

相关推荐

FPGA设计中竞争冒险问题的研究

怎样消除竞争冒险

组合逻辑电路的竞争冒险,输入信号同时从1变0会产生竞争冒险吗

FPGA中的竞争和冒险现象

什么是竞争与冒险现象?怎样判断?如何消除?

FPGA | 竞争冒险和毛刺问题

组合逻辑中的竞争与冒险及毛刺的处理方法

竞争与冒险产生的原因,判断方法和避免竞争与冒险的方法

竞争与冒险产生的原因,判断方法和避免竞争与冒险的方法

评论